# 6. Delta-Sigma Modulators for ADC

Francesc Serra Graells

francesc.serra.graells@uab.cat Departament de Microelectrònica i Sistemes Electrònics Universitat Autònoma de Barcelona

> paco.serra@imb-cnm.csic.es Integrated Circuits and Systems IMB-CNM(CSIC)

- 2 Architecture Selection Based on Quantization Error

- 3 Switched-Capacitor CMOS Implementations

- 4 Modeling Circuit Second Order Effects

- 5 Digitally Assisted Techniques

- 6 Low-Power Circuit Topologies

F. Serra Graells

F. Serra Graells

- Oversampling and Noise Shaping Principles

- Architecture Selection Based on Quantization Error

- Switched-Capacitor CMOS Implementations

- Modeling Circuit Second Order Effects

- Digitally Assisted Techniques

- Low-Power Circuit Topologies

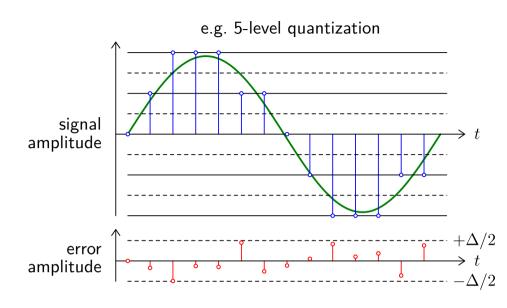

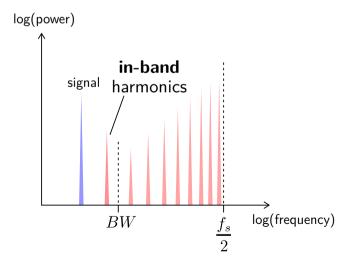

► Flat (white) error spectrum profile

$$\Delta = \frac{V_{FS}}{2^N} \qquad QN = \frac{\Delta^2}{12}$$

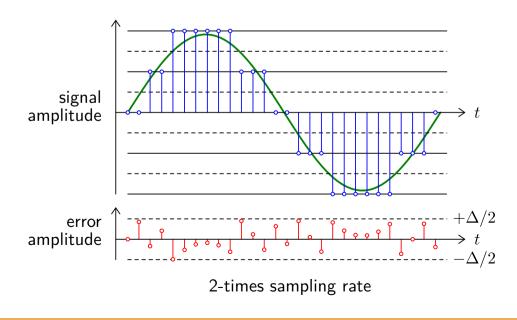

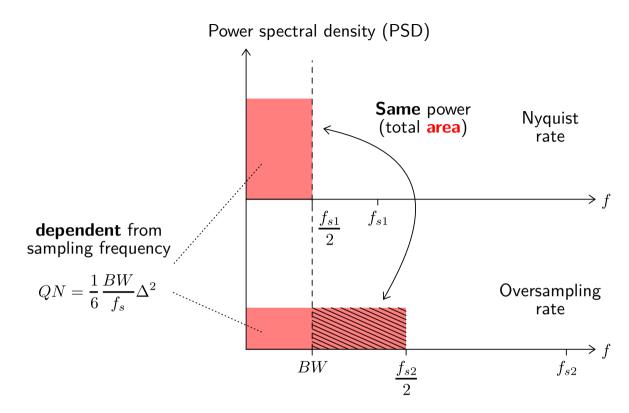

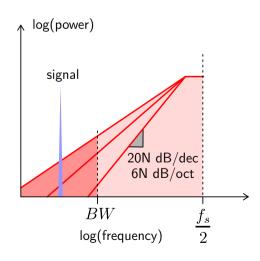

# **Oversampling**

► Flat (white) error spectrum profile:

$$QN(f) = \frac{1}{6} \frac{\Delta^2}{f_s} \quad \text{[W/Hz]}$$

- ► **Spread** across spectrum (fs/2)

- Oversampling ratio:

$$OSR \doteq \frac{f_s}{f_{nyq}} \equiv \frac{f_s}{2BW}$$

- ▲ Lower in-band noise

- ▼ Higher clock frequencies

$$QN = \frac{\Delta^2}{12} \frac{1}{OSR}$$

$S_{max} = \left(\frac{V_{FS}}{2\sqrt{2}}\right)^2$   $SQNR_{max} \doteq \frac{S_{max}}{QN} = \left(2^N\sqrt{1.5}\right)^2 OSR$

$$SQNR_{max} = 6.02N + 1.76 + 10\log OSR \quad \text{[dB]}$$

$$+3\text{dB/oct}$$

$$+0.5\text{bit/oct}$$

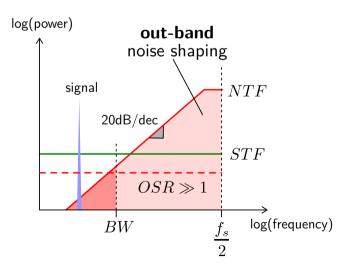

### **Quantization Noise Shaping**

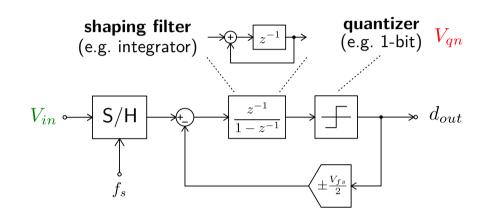

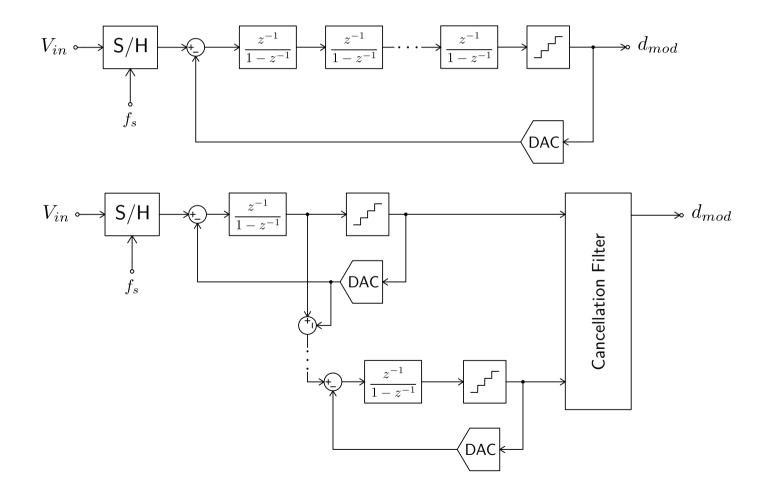

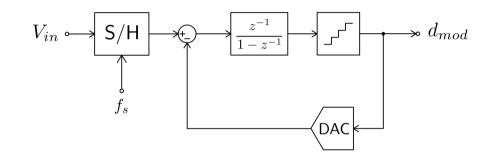

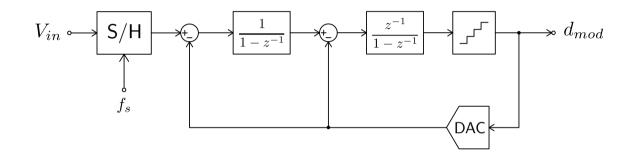

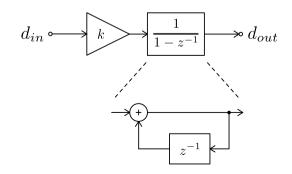

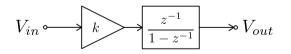

Basic single-loop Delta-Sigma modulator (**DSM**) for discrete time (**DT**) ADCs:

$$D_{out} = STF(z)V_{in} + NTF(z)V_{qn} \begin{cases} STF = \frac{H}{1+H} & \to 1 \\ H \to \infty \\ NTF = \frac{1}{1+H} & \to 0 \end{cases}$$

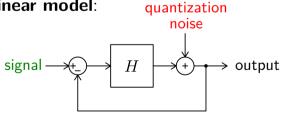

Equivalent **linear model**:

ion

$$H(z)=\frac{z^{-1}}{1-z^{-1}}\left\{\begin{array}{l} STF=\frac{H}{1+H}\equiv z^{-1}\\ NTF=\frac{1}{1+H}\equiv 1-z^{-1}\\ & \text{high-pass}\\ \text{shaping} \end{array}\right.$$

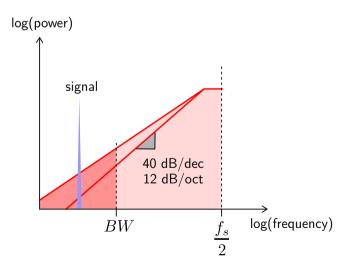

### **Quantization Noise Shaping**

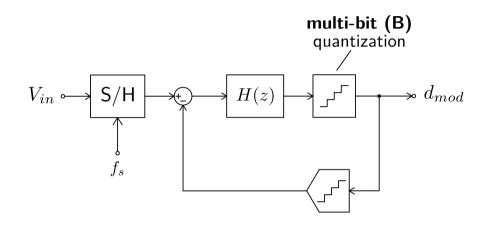

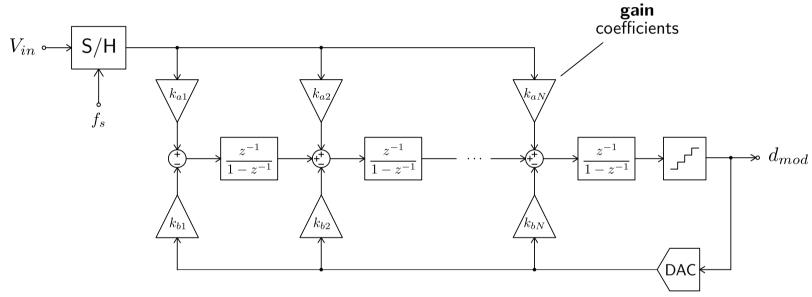

► N-order B-bit single loop architecture:

- ► Multi-bit quantization:

- Resolution added to overall **DR**

- Internal full-scale reduction

- Feedback DAC not intrinsically linear

oversampling

- ► **High-order** filtering:

- Sharper noise shaping

- **Stability** issues

► **Ideal** dynamic range:

$$DR = \frac{3\pi}{2} \left(2^B - 1\right)^2 (2N + 1) \left(\frac{OSR}{\pi}\right)^{2N+1} \tag{N+0.5)-bit/oct(OSR)}$$

$$DR[\mathsf{dB}] = 6.7 + 20 \log \left(2^B - 1\right) + 10 \log \left(2N + 1\right) + 20 \left(N + 0.5\right) \log \frac{OSR}{\pi}$$

$$\frac{\mathsf{direct}}{\mathsf{improvement}}$$

shaping

- Oversampling and Noise Shaping Principles

- Architecture Selection Based on Quantization Error

- Switched-Capacitor CMOS Implementations

- Modeling Circuit Second Order Effects

- Digitally Assisted Techniques

- Low-Power Circuit Topologies

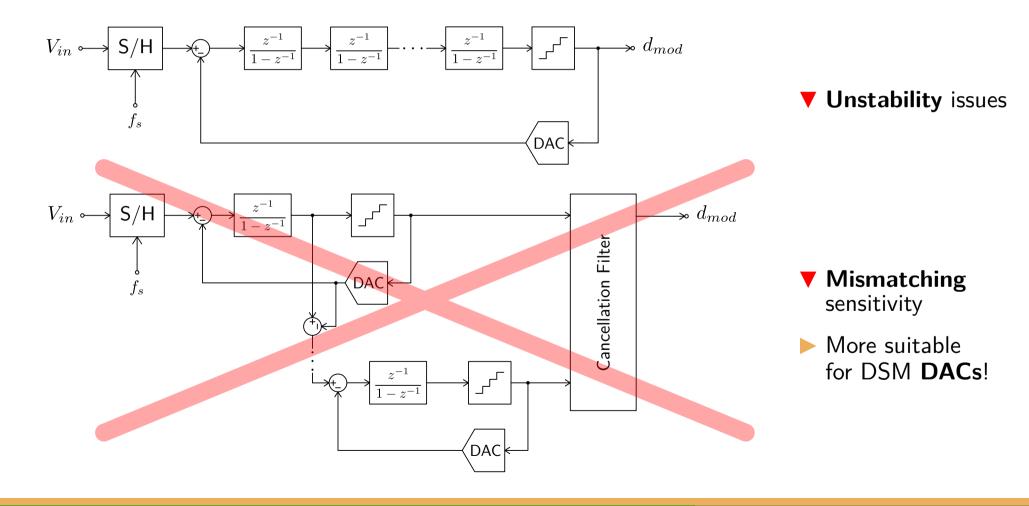

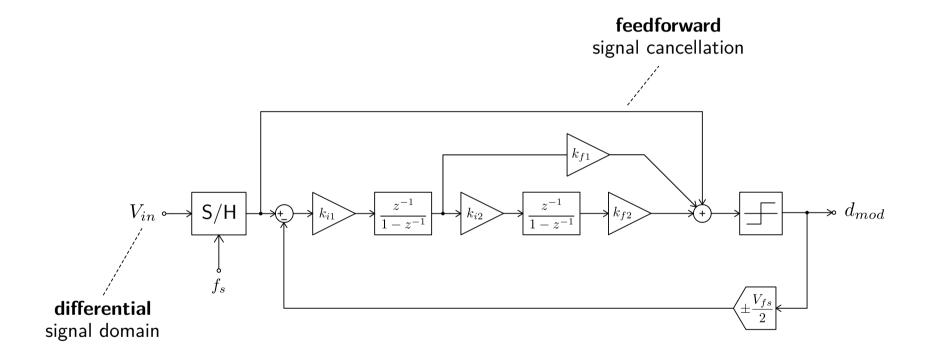

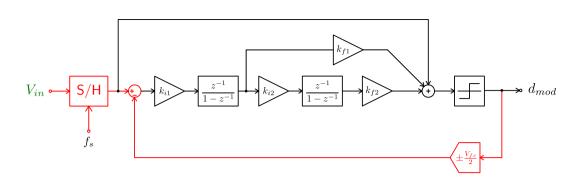

### Single-Loop vs MASH

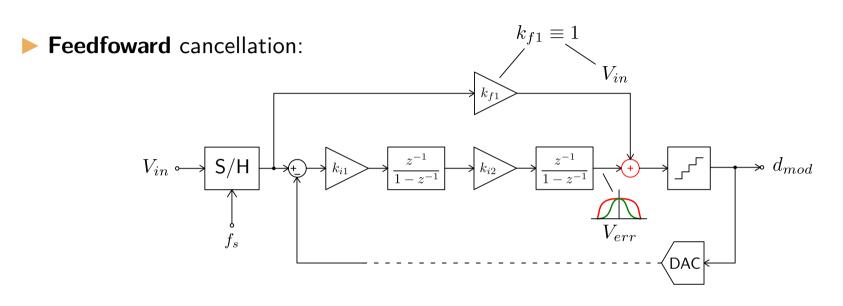

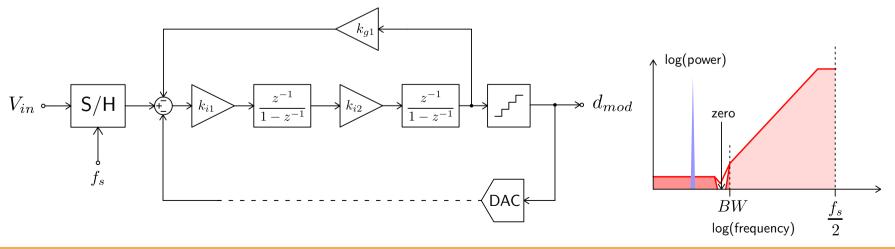

► High-order **feedback** or **feedforward** DSM architectures:

### Single-Loop vs MASH

► High-order **feedback** or **feedforward** DSM architectures:

11/47

#### **Order Selection**

Simplest DSM architecture: first order

$$H(z) = \frac{z^{-1}}{1 - z^{-1}} \quad \begin{cases} STF = \frac{H}{1 + H} \equiv z^{-1} \\ NTF = \frac{1}{1 + H} \equiv 1 - z^{-1} \end{cases}$$

- ▲ Intrinsically **stable**

- **▼ Large OSR** needed

- **▼ Tonal** spectrum caused by signal to quantization noise correlation!

#### **Order Selection**

► Next architecture step: **second order**

$$\begin{cases} STF = \frac{1}{\left(\frac{1-z^{-1}}{z^{-1}} + 1\right)(1-z^{-1}) + 1} \equiv z^{-1} \\ NTF = \frac{1}{1 + \left(\frac{1}{1-z^{-1}} + 1\right)\frac{z^{-1}}{1-z^{-1}}} \equiv (1-z^{-1})^2 \\ & \text{second-order high-pass} \end{cases}$$

- ▲ Intrinsically **stable** for limited input range

- ▲ Signal to quantization noise **uncorrelation** (continuous spectrum)

- Moderate OSR requirements

### **Delta-Sigma Noise Shaping**

► **Higher-order** general architecture:

- ▲ Sharper noise shaping

- ▼ Possibility of loop instability for N>2

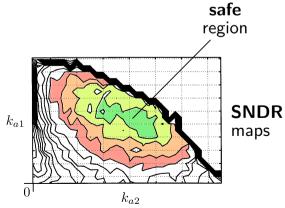

► Coefficients optimization against mismatching

Delta-Sigma Modulators for ADC Basics Architectures SC Modeling Assisted Low-Power

### **Commonly Used Architectures**

- ▲ Internal full scale low occupancy

- ▼ Additional **adder stage** in front of quantizer

Resonator attenuation:

▲ Extra noise shaping at **band edge**

14/47

▼ Zero sensitivity to coefficient **matching**

- Oversampling and Noise Shaping Principles

- Architecture Selection Based on Quantization Error

- Switched-Capacitor CMOS Implementations

- Modeling Circuit Second Order Effects

- Digitally Assisted Techniques

- Low-Power Circuit Topologies

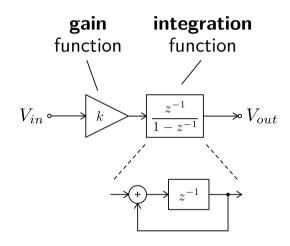

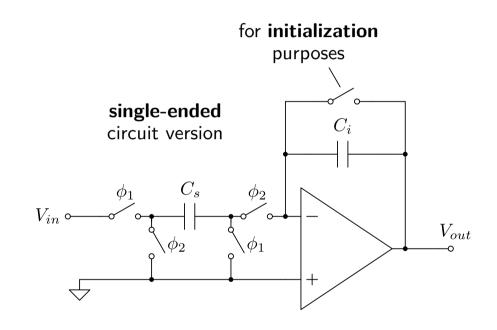

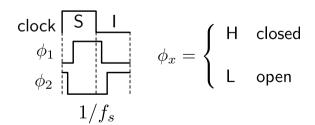

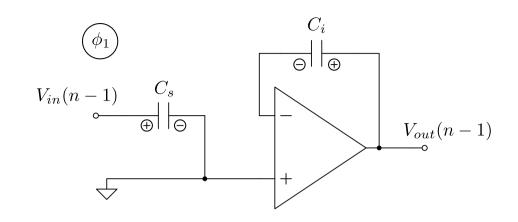

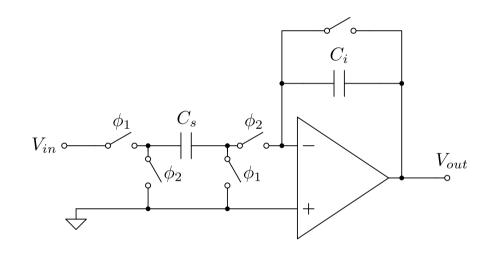

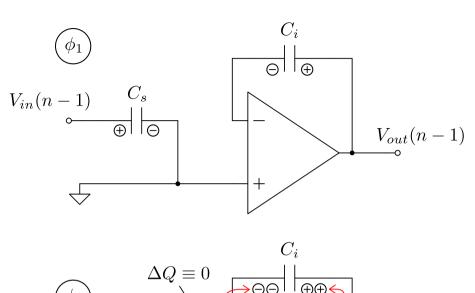

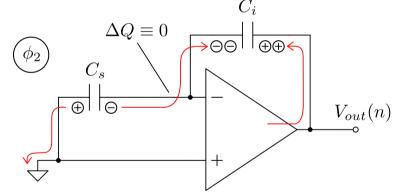

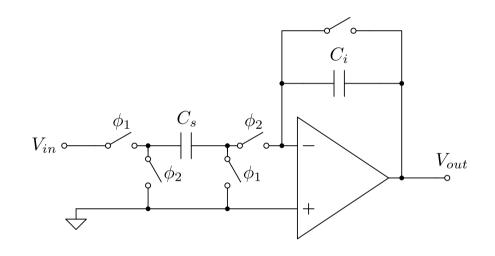

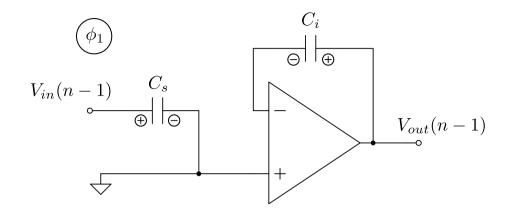

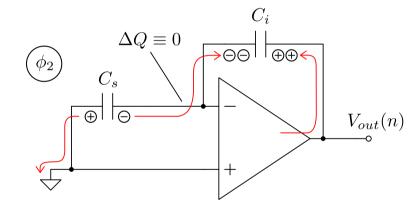

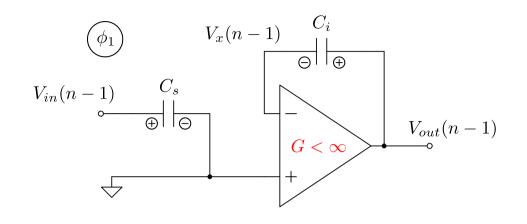

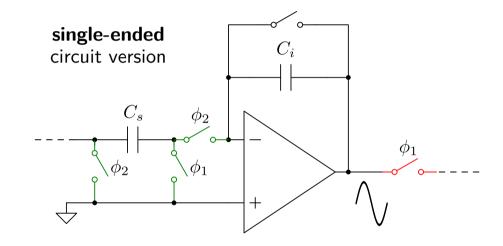

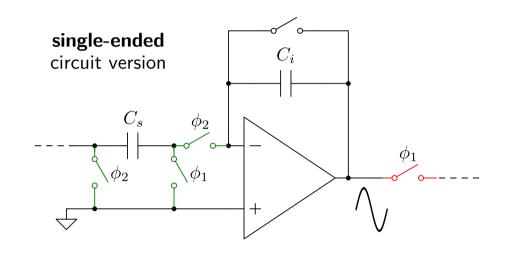

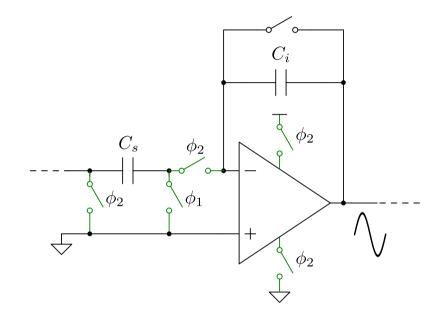

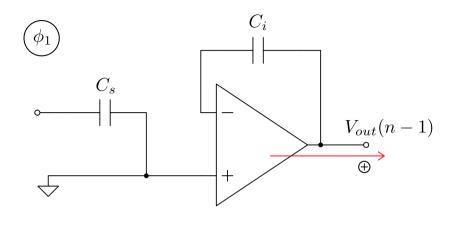

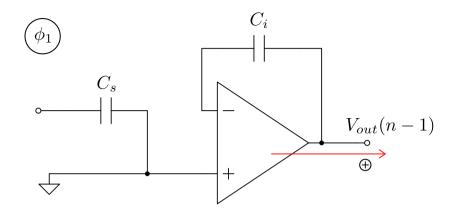

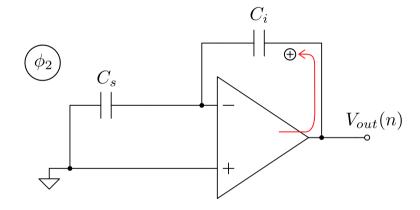

Shaping filter basic building **block**:

Analog circuit realization (ADC)

**Digital** circuit realization (DAC)

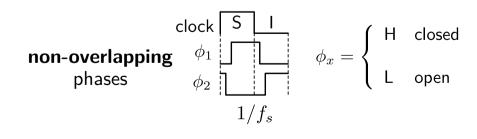

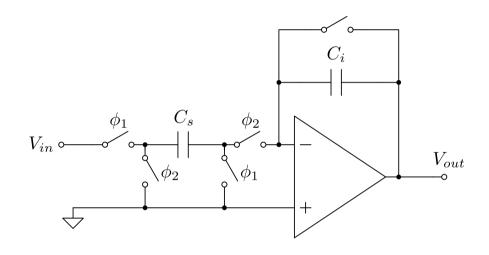

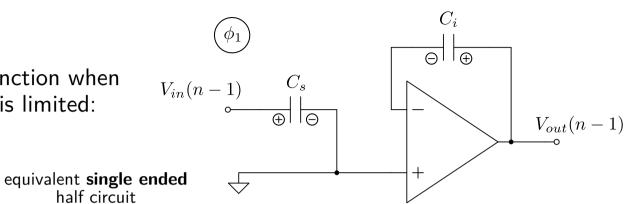

► SC-OpAmp **compact** implementation:

► SC-OpAmp **compact** implementation:

F. Serra Graells

► SC-OpAmp **compact** implementation:

$$V_{out}(n) = V_{out}(n-1) + \frac{C_s}{C_i}V_{in}(n-1)$$

► SC-OpAmp **compact** implementation:

$$\frac{V_{out}(z)}{V_{in}(z)} = k \frac{z^{-1}}{1 - z^{-1}} \qquad k \doteq \frac{C_s}{C_i}$$

$$V_{out}(n) = V_{out}(n-1) + \frac{C_s}{C_i}V_{in}(n-1)$$

$$V_{out}(z) = z^{-1}V_{out}(z) + \frac{C_s}{C_i}z^{-1}V_{in}(z)$$

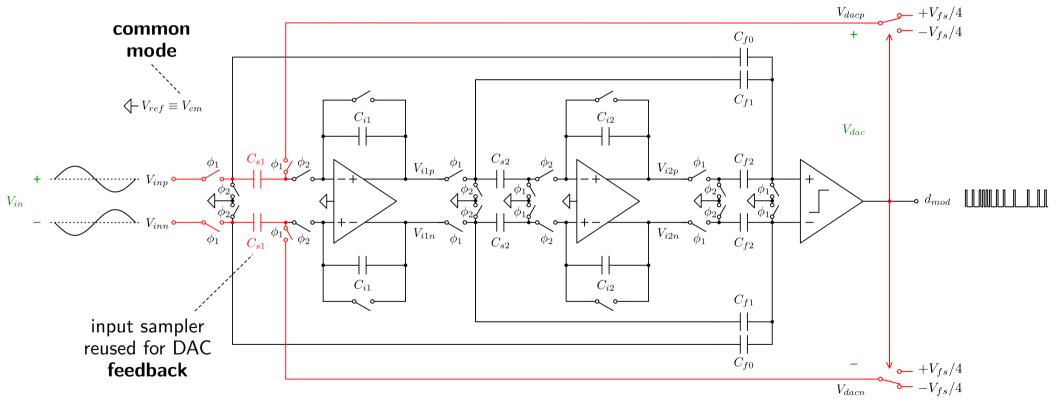

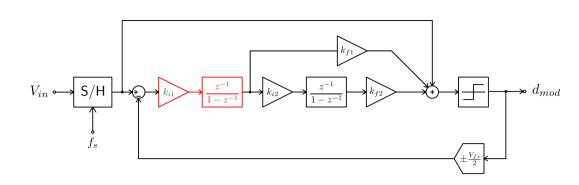

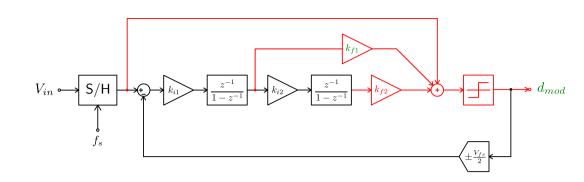

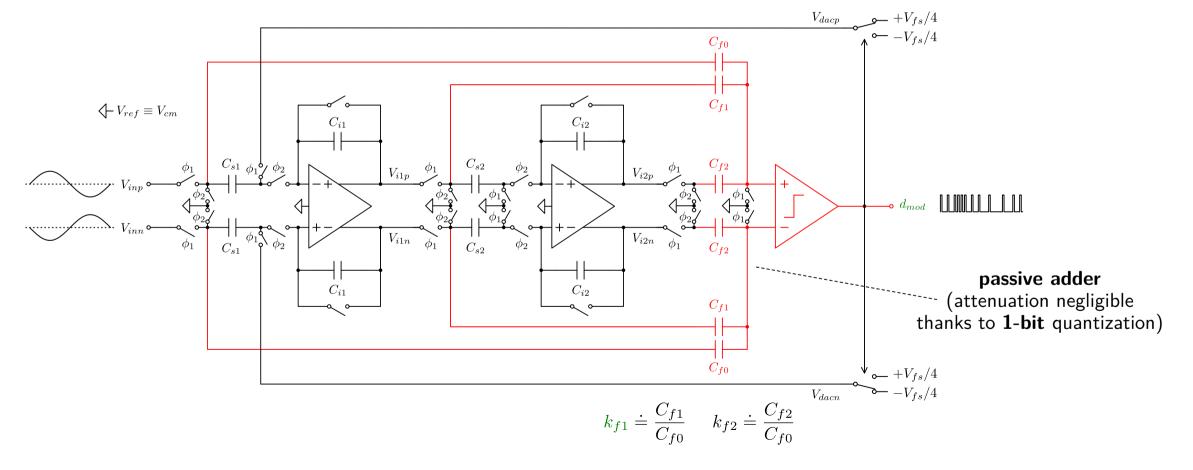

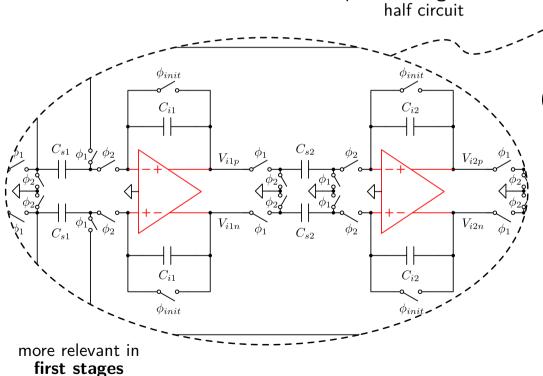

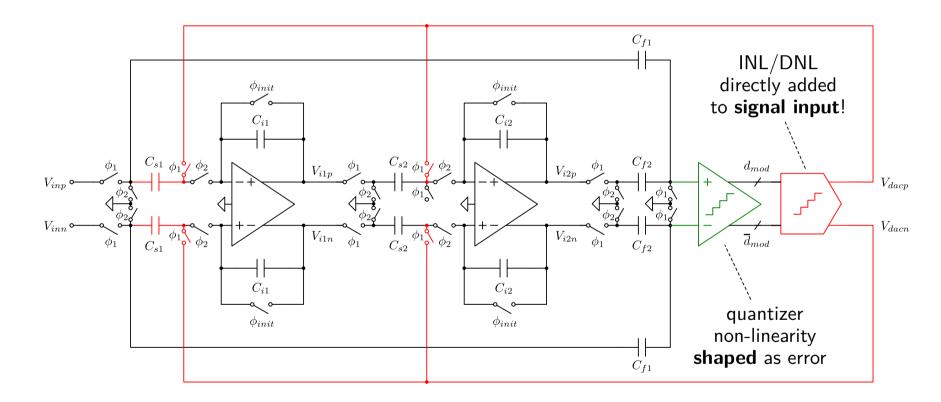

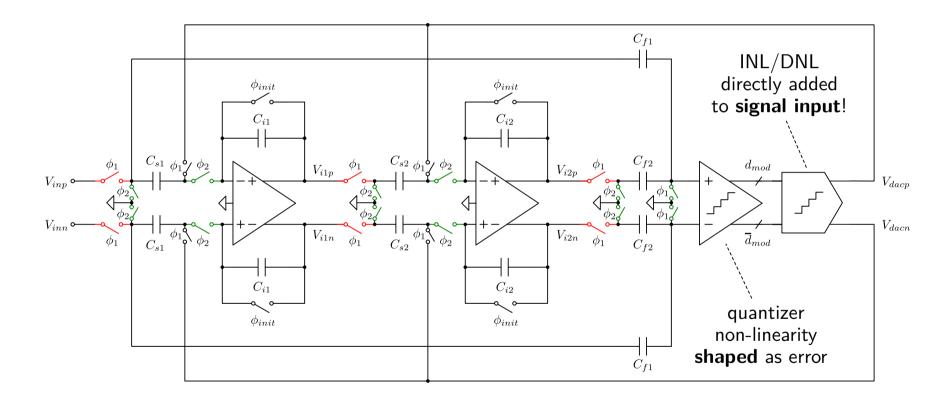

► Fully-differential 2nd-order single-bit DSM example:

► Fully-differential 2nd-order single-bit DSM example:

$$(\phi_1)$$

$Q_{s1}(n-1) = C_{s1} [V_{in}(n-1) - V_{dac}(n-1)]$

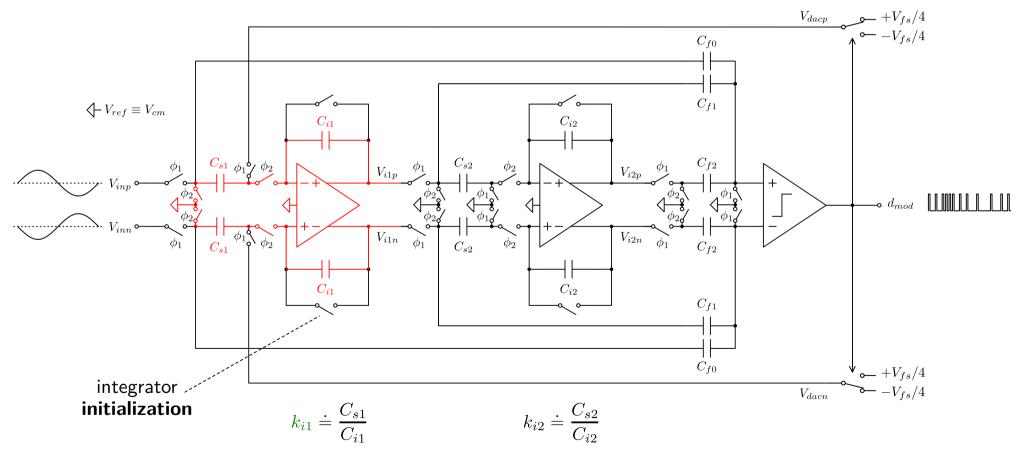

► Fully-differential 2nd-order single-bit DSM example:

► Fully-differential 2nd-order single-bit DSM example:

- Architecture Selection Based on Quantization Error

- Switched-Capacitor CMOS Implementations

- Modeling Circuit Second Order Effects

- Digitally Assisted Techniques

- Low-Power Circuit Topologies

25/47

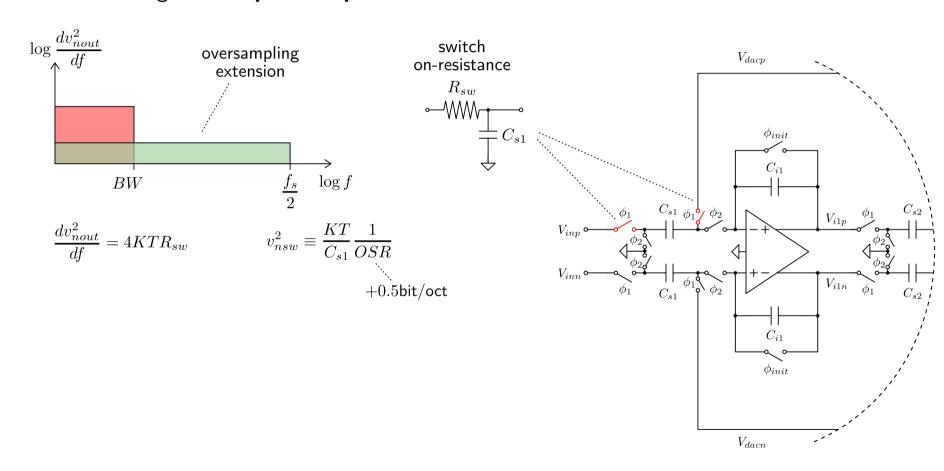

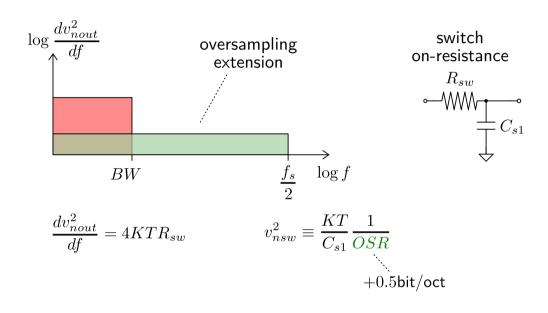

#### **Switch Thermal Noise**

► Added to signal at **input sampler**:

#### **Switch Thermal Noise**

Added to signal at **input sampler**:

$\phi_{init}$

$V_{dacn}$

$V_{dacp}$

► Fully differential contributions:  $v_{nswtot}^2 \equiv \frac{2}{C_{s1}} \frac{1}{OSR}$

$$DR_{diff} = DR_{sing} - \underbrace{3dB}_{\text{switches} \times 2} + \underbrace{6dB}_{\text{full-scale} \times 2} = DR_{sing} + 3dB(+0.5bit)$$

▼ Large capacitor area and low input impedance values!

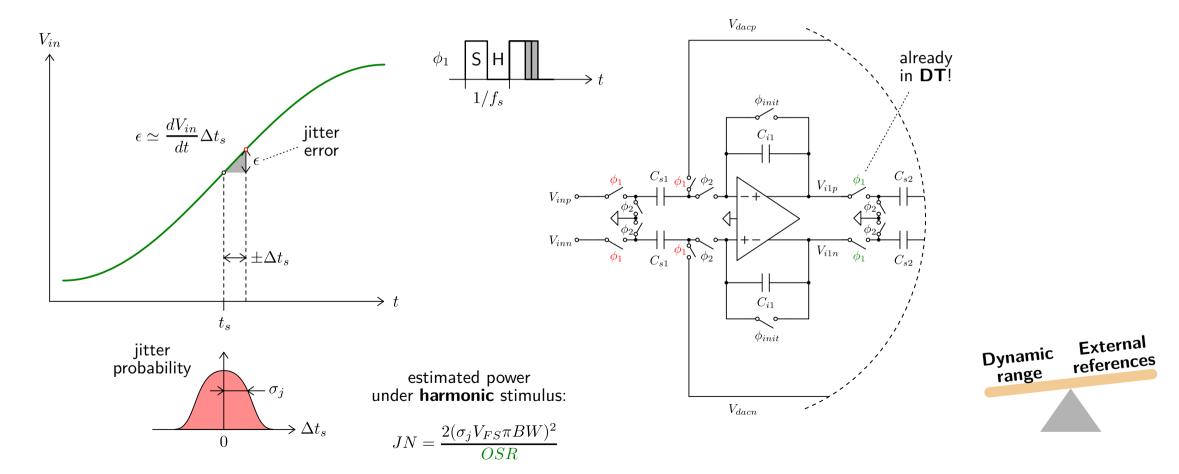

#### **Clock Jitter**

Critical at input sampler due to its continuous (CT) to discrete time (DT) conversion:

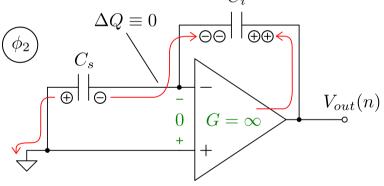

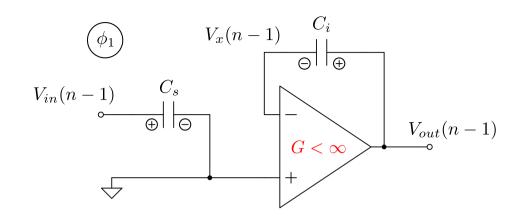

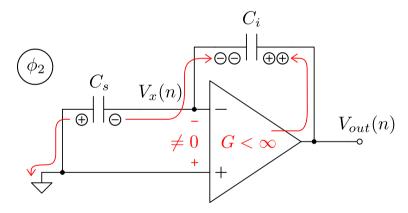

# **OpAmp Finite Gain**

► SC **integrator** transfer function when OpAmp **open loop gain** is limited:

$$V_{out}(n) = V_{out}(n-1) + \frac{C_s}{C_i}V_{in}(n-1)$$

$$\frac{V_{out}}{V_{in}}(z) = k \frac{z^{-1}}{1 - z^{-1}} \qquad k \doteq \frac{C_s}{C_i}$$

### **OpAmp Finite Gain**

SC integrator transfer function when OpAmp open loop gain is limited:

$$Q_x(n) \equiv Q_x(n-1)$$

$$C_s V_x(n) + C_i [V_x(n) - V_{out}(n)] =$$

=  $-C_s V_{in}(n-1) + C_i [V_x(n-1) - V_{out}(n-1)]$

$$V_x \doteq -\frac{V_{out}}{G}$$

$$+C_s \frac{V_{out}(n)}{G} + C_i \left(1 + \frac{1}{G}\right) V_{out}(n) =$$

$$= +C_s V_{in}(n-1) + C_i \left(1 + \frac{1}{G}\right) V_{out}(n-1)$$

integration **leakage** gain **mismatch**

$$k \doteq \frac{C_s}{C_i} \qquad V_{out}(n) = \frac{V_{out}(n-1)}{1+\frac{k}{1+G}} + \frac{kV_{in}(n-1)}{1+\frac{1}{G}(k+1)}$$

### **OpAmp Finite Gain**

SC **integrator** transfer function when OpAmp **open loop gain** is limited:

$$Q_x(n) \equiv Q_x(n-1)$$

$$C_s V_x(n) + C_i [V_x(n) - V_{out}(n)] =$$

=  $-C_s V_{in}(n-1) + C_i [V_x(n-1) - V_{out}(n-1)]$

$$V_x \doteq -\frac{V_{out}}{G}$$

$$+C_s \frac{V_{out}(n)}{G} + C_i \left(1 + \frac{1}{G}\right) V_{out}(n) =$$

$$= +C_s V_{in}(n-1) + C_i \left(1 + \frac{1}{G}\right) V_{out}(n-1)$$

integration **leakage** gain **mismatch**

$$k \doteq \frac{C_s}{C_i} \qquad V_{out}(n) = \frac{V_{out}(n-1)}{1+\frac{k}{1+G}} + \frac{kV_{in}(n-1)}{1+\frac{1}{G}(k+1)}$$

▼ **Signal dependent** gain generates output **distortion**

$$G o \infty$$

$$V_{out}(n) = V_{out}(n-1) + kV_{in}(n-1)$$

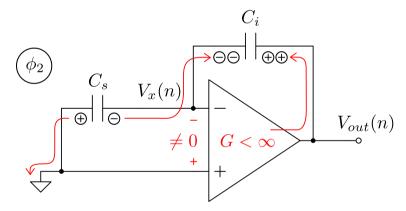

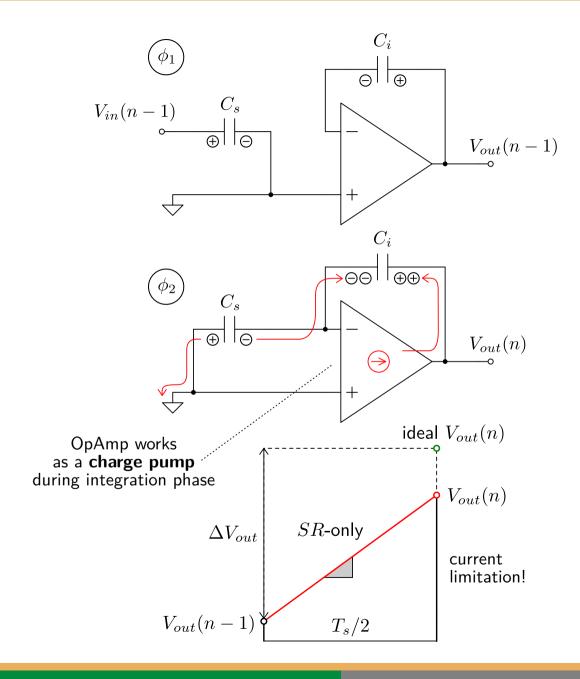

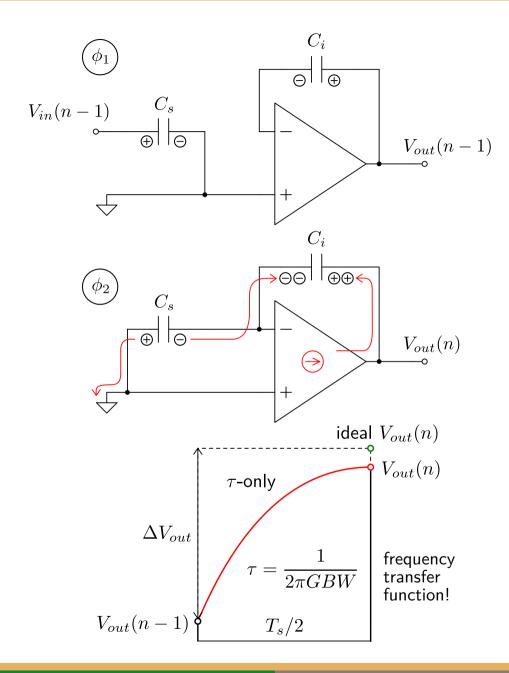

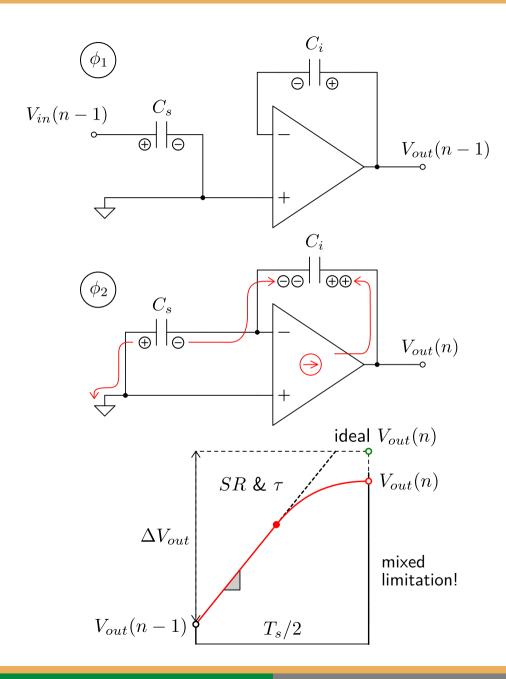

- ► Qualitative **case studies**:

- lacksquare if  $SR < rac{\Delta V_{out}}{T_s/2}$  : slewing only

$$V_{out}(n) = V_{out}(n-1) \pm SR \frac{T_s}{2}$$

# **OpAmp Slew-Rate and GBW**

- Qualitative case studies:

- if  $SR < \frac{\Delta V_{out}}{T_s/2}$  : slewing only  $V_{out}(n) = V_{out}(n-1) \pm SR \frac{T_s}{2}$

- if  $\left| \frac{\Delta V_{out}}{\tau} \right| < SR$  : settling only  $V_{out}(n) = V_{out}(n-1) + \Delta V_{out} \left(1 - e^{-\frac{T_s}{2\tau}}\right)$

# **OpAmp Slew-Rate and GBW**

- Qualitative case studies:

- if  $SR < \frac{\Delta V_{out}}{T_s/2}$  : slewing only  $V_{out}(n) = V_{out}(n-1) \pm SR\frac{T_s}{2}$

- $\begin{tabular}{l} \blacksquare & \mbox{if } \left| \frac{\Delta V_{out}}{\tau} \right| < SR: \mbox{ settling only} \\ \\ & V_{out}(n) = V_{out}(n-1) + \Delta V_{out} \left(1 e^{-\frac{T_s}{2\tau}}\right) \\ \end{tabular}$

else : slewing+slettling

$$V_{out}(n) = V_{out}(n-1) + \Delta V_{out} - SR\tau e^{-\left(\frac{T_s}{2\tau} - \frac{\Delta V_{out}}{\tau SR} + 1\right)}$$

**▼ Non-linear** errors = signal **distortion**

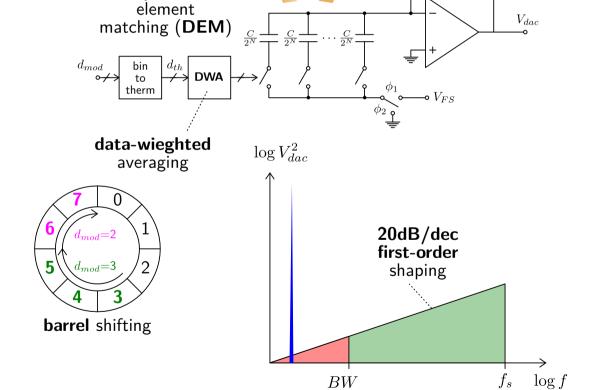

### Feedback DAC Non-Linearity

Only for **multi-bit** DSM architectures:

▼ How to get rid of feedback **flash DAC** non-linearity effects?

- Oversampling and Noise Shaping Principles

- Architecture Selection Based on Quantization Error

- Switched-Capacitor CMOS Implementations

- Modeling Circuit Second Order Effects

- Digitally Assisted Techniques

- Low-Power Circuit Topologies

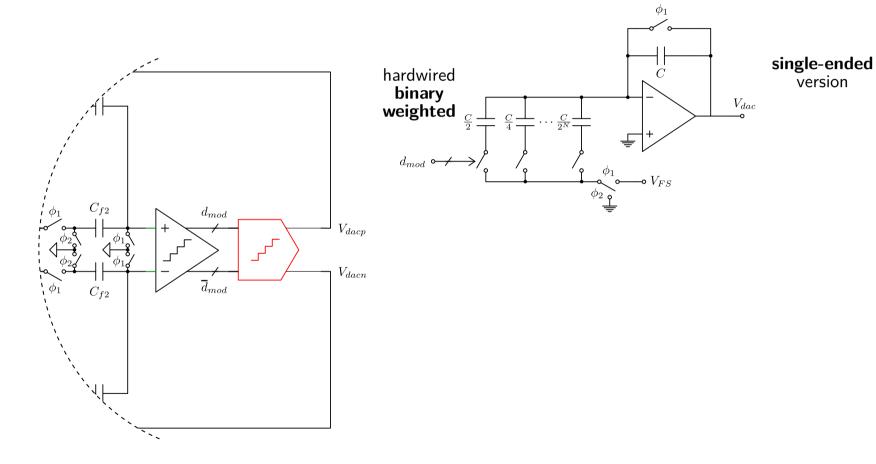

### Feedback DAC Mismatching

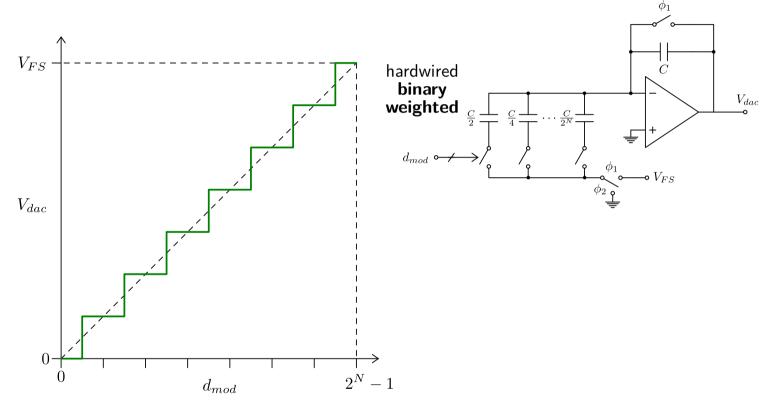

► Single-stage **multi-bit SC flash** architecture example:

36/47

version

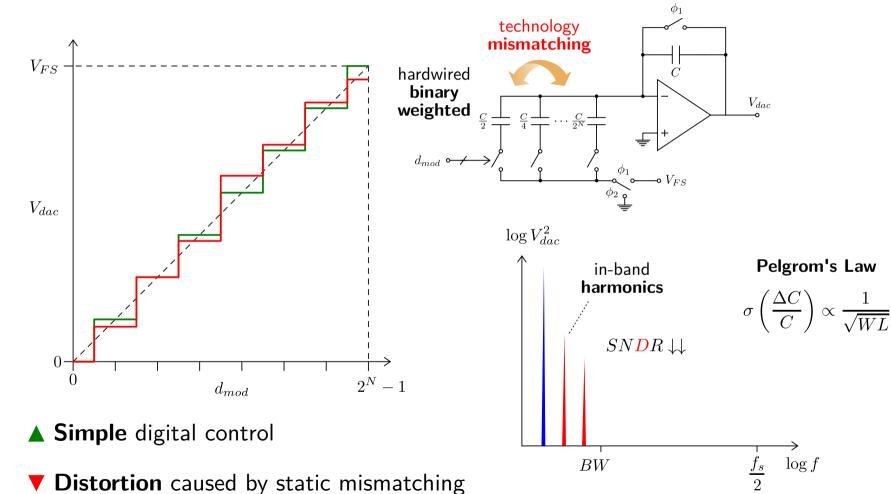

### Feedback DAC Mismatching

► Single-stage **multi-bit SC flash** architecture example:

▲ Simple digital control

### Feedback DAC Mismatching

► Single-stage **multi-bit SC flash** architecture example:

Delta-Sigma Modulators for ADC Basics Architectures SC Modeling Assisted Low-Power

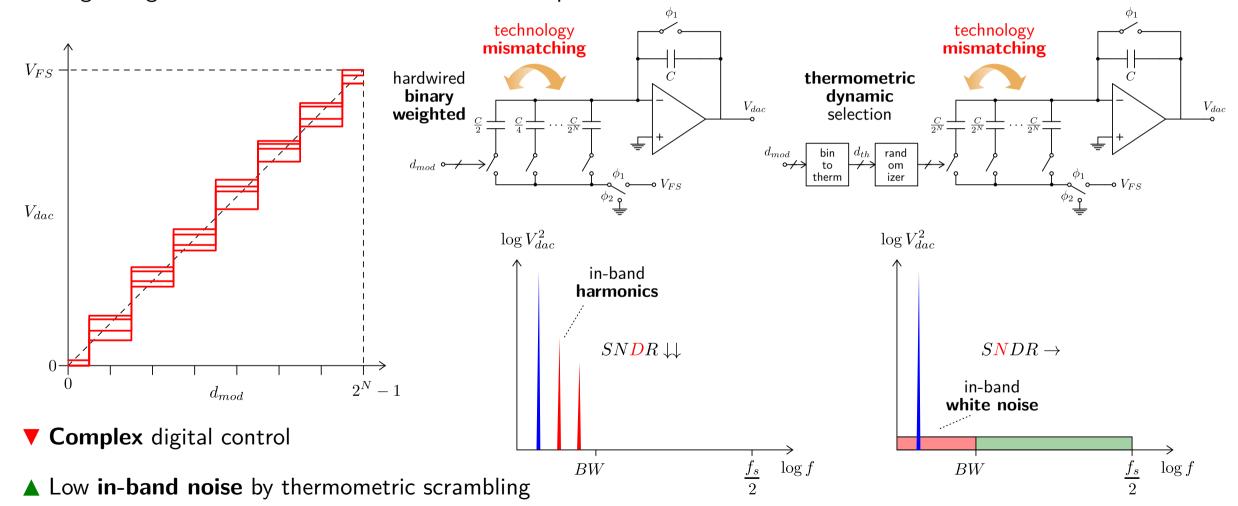

### Feedback DAC Mismatching

► Single-stage **multi-bit SC flash** architecture example:

Delta-Sigma Modulators for ADC Basics Architectures SC Modeling Assisted Low-Power

dynamic

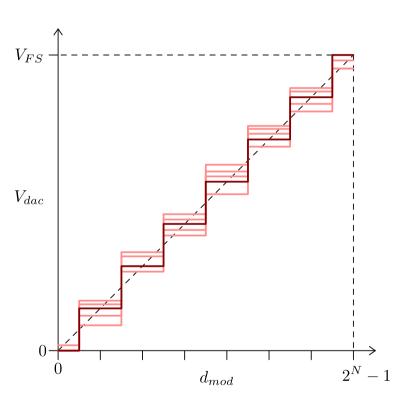

### Feedback DAC Mismatching

► Single-stage **multi-bit SC flash** architecture example:

technology mismatching

- **▼ Complex** digital control

- ▲ Mismatch shaping by equalizing long-term element selection

- 1 Oversampling and Noise Shaping Principles

- 2 Architecture Selection Based on Quantization Error

- 3 Switched-Capacitor CMOS Implementations

- 4 Modeling Circuit Second Order Effects

- 5 Digitally Assisted Techniques

- 6 Low-Power Circuit Topologies

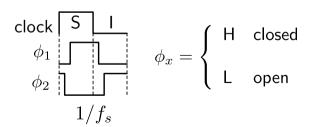

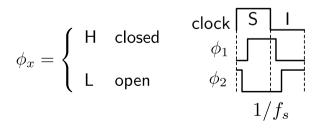

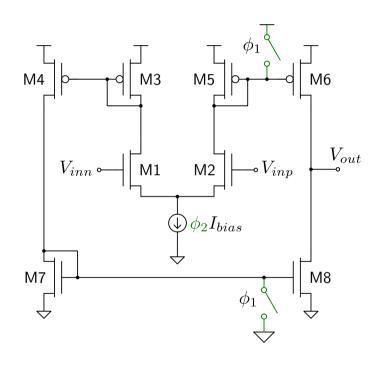

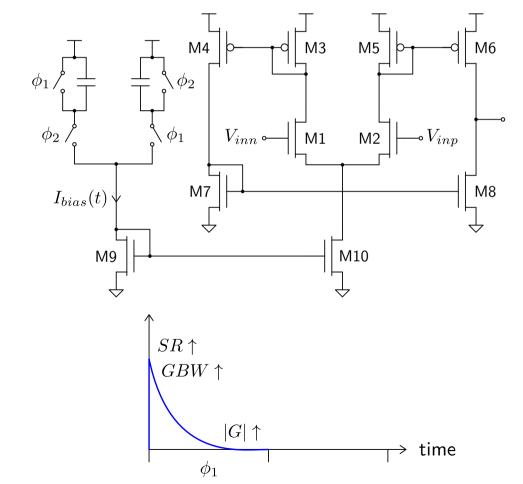

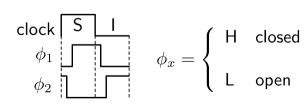

# Switched OpAmp (SOA)

▶ **Distortion** caused by signal-dependent switch on-resistance:

▼ How to make **on-resistance independent from signal** for these particular switches?

► Moving output switches into **OpAmp** blocks:

# Switched OpAmp (SOA)

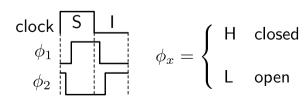

Moving output switches into **OpAmp** blocks:

$$\phi_x = \left\{ egin{array}{lll} \mathsf{H} & \mathsf{closed} & \mathsf{clock} & \mathsf{S} & \mathsf{I} \\ \mathsf{L} & \mathsf{open} & \phi_2 & \mathsf{I} & \mathsf{I} \end{array}

ight.$$

→ J. Crols and M. Steyaert Switched-OpAmp: An Approach to Realize Full CMOS Switched-Capacitor Circuits at Very Low Power Supply Voltages IEEE Journal of Solid-State Circuits 29(8):936-942, Aug 1994 doi.org/10.1109/4.297698

- ▲ **Constant** on-resistance for all switches

- ▲ Power savings due to 50% OpAmp **duty cycle**

- ▼ Each integrator stage operates in **alternative phases**

Delta-Sigma Modulators for ADC Basics Architectures SC Modeling Assisted Low-Power

# Switched OpAmp (SOA)

Moving output switches into **OpAmp** blocks:

**Example:** single-ended single-stage folded OpAmp

✓ J. Crols and M. Steyaert

Switched-OpAmp: An Approach to Realize Full CMOS Switched-Capacitor

Circuits at Very Low Power Supply Voltages

IEEE Journal of Solid-State Circuits 29(8):936–942, Aug 1994

doi.org/10.1109/4.297698

- ▲ Constant on-resistance for all switches

- ▲ Power savings due to 50% OpAmp **duty cycle**

- ▼ Each integrator stage operates in alternative phases

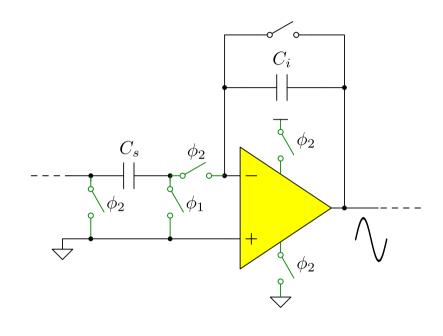

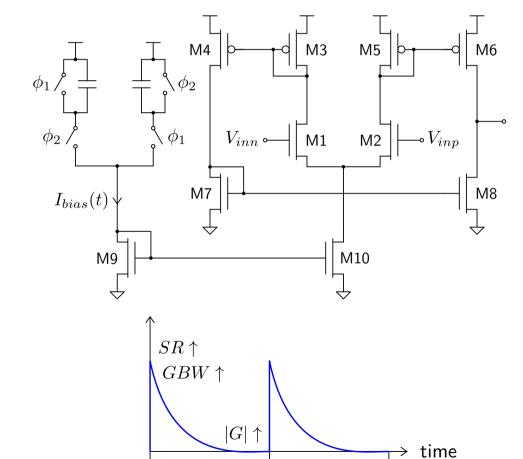

### **OpAmp Dynamic Biasing**

► Discrete time **dynamic biasing**:

→ B. J. Hosticka Dynamic CMOS amplifiers IEEE Journal of Solid-State Circuits 15(5):881-886, Oct 1980 doi.org/10.1109/JSSC.1980.1051488

Discrete time **dynamic biasing**:

$\phi_2$

$\phi_1$

- ▲ Synchronous **Class-AB** operation

- ▲ Static **power** savings

- **▼** OpAmp fast on/off recovery time required

- Biasing **peak** value is technology dependent

- **▼ Ripple** induced in the power rails (digital-like)

B. J. Hosticka Dynamic CMOS amplifiers IEEE Journal of Solid-State Circuits 15(5):881-886, Oct 1980 doi.org/10.1109/JSSC.1980.1051488