# 5. CMOS Operational Amplifiers

### Francesc Serra Graells

francesc.serra.graells@uab.cat

Departament de Microelectrònica i Sistemes Electrònics

Universitat Autònoma de Barcelona

paco.serra@imb-cnm.csic.es

Integrated Circuits and Systems

IMB-CNM(CSIC)

- 2 The Mono-Transistor Amplifier

- 3 Differential Circuits with CMFB

- 4 Folded Amplifiers

- Cascode Topologies

- 6 Gain Enhancement Techniques

- 7 Multi-Stage OpAmps

- 1 OpAmp Figures of Merit

- 2 The Mono-Transistor Amplifier

- 3 Differential Circuits with CMFB

- 4 Folded Amplifiers

- 5 Cascode Topologies

- 6 Gain Enhancement Techniques

- 7 Multi-Stage OpAmps

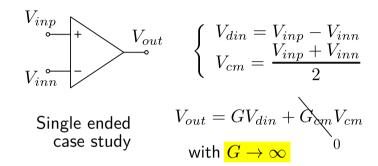

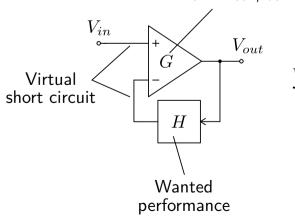

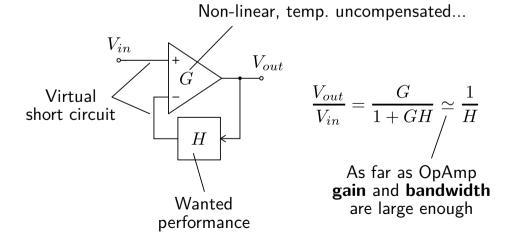

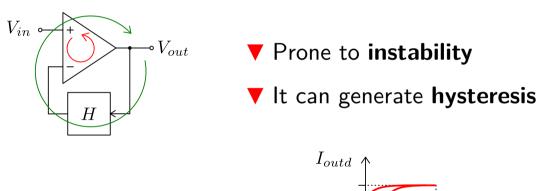

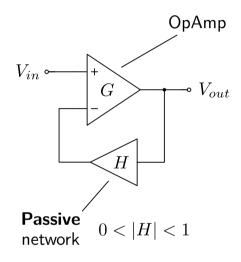

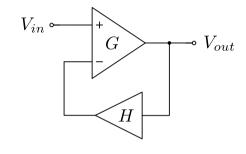

### **Universal Analog Building Block**

Operational voltage amplifier (OpAmp)

▲ Analog computing **operations** in closed loop:

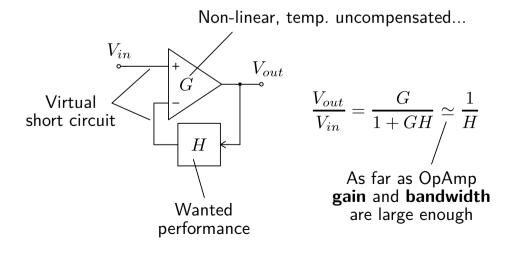

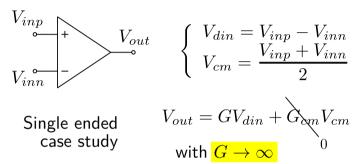

# **Universal Analog Building Block**

Operational voltage amplifier (OpAmp)

▲ Analog computing **operations** in closed loop:

Non-linear, temp. uncompensated...

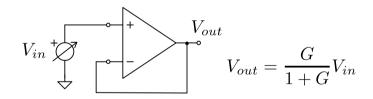

$$\frac{V_{out}}{V_{in}} = \frac{G}{1 + GH} \simeq \frac{1}{H}$$

As far as OpAmp **gain** and **bandwidth** are large enough

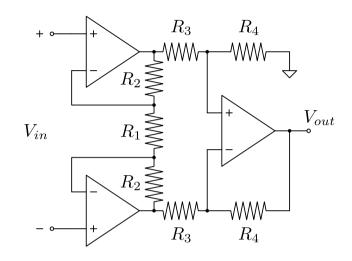

e.g. Instrumentation amplifier

$$\frac{V_{out}}{V_{in}} = \left(1 + \frac{2R_2}{R_1}\right) \frac{R_4}{R_3}$$

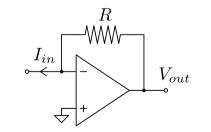

e.g. I/V converter

$$\frac{V_{out}}{I_{in}} = R$$

### **Universal Analog Building Block**

Operational voltage amplifier (OpAmp)

▲ Analog computing **operations** in closed loop:

► CMOS OpAmp known as operational transconductance amplifier (OTA)

OpAmp or OTA naming depends on the load conditions...

e.g. switched capacitor (SC) filters

CMOS Operational Amplifiers FoM Mono CMFB Folded Cascode Gain Multi-Stage

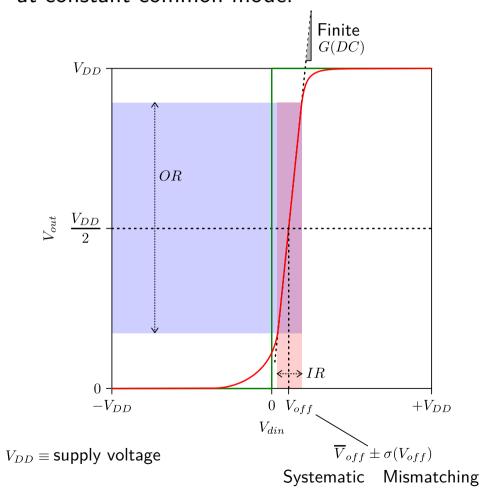

### **OpAmp Performance Parameters**

- **Large signal static** figures (ideal):

- Input range

$IR \quad (\rightarrow 0)$

Output range

$OR \quad (\rightarrow V_{DD})$

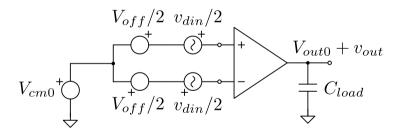

Equivalent input offset

- $V_{off} \quad (\to 0)$

- Open loop differential DC gain G(DC)  $(\to \infty)$

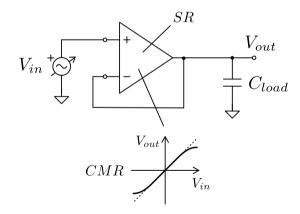

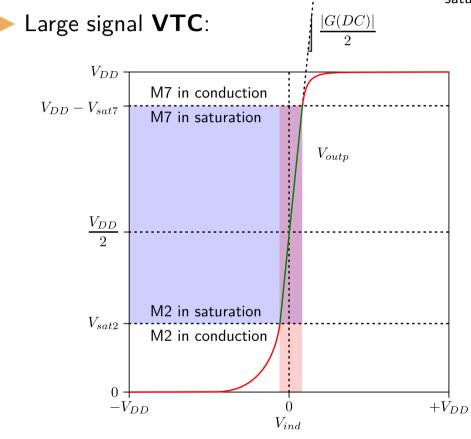

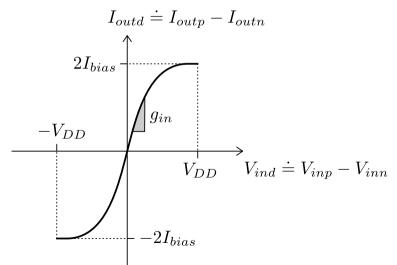

Open-loop differential DC voltage transfer curve (VTC) at constant common mode:

- ► Large signal static figures (ideal):

- Input range

$$IR \quad (\rightarrow 0)$$

Output range

$$OR \quad (\rightarrow V_{DD})$$

Equivalent input offset

$$V_{off} \quad (\to 0)$$

- Open loop differential DC gain G(DC)  $(\to \infty)$

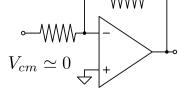

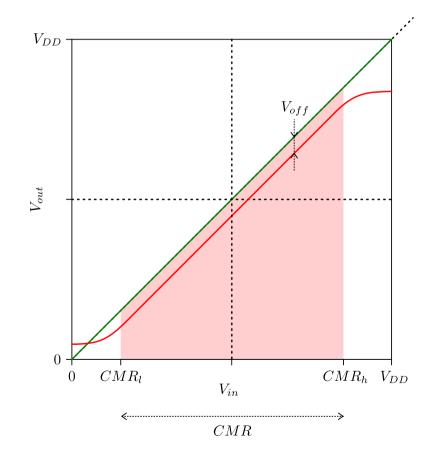

- Common mode range

$$CMR_{l,h} \quad (\to 0, V_{DD})$$

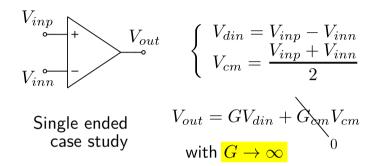

$$\begin{cases} V_{din} = V_{inp} - V_{inn} \\ V_{cm} = \frac{V_{inp} + V_{inn}}{2} \end{cases} V_{cm} = \frac{1}{2} \frac{1 + 2G}{1 + G} V_{in} \simeq V_{in}$$

Depending on feedback topology!

#### ► **Input common-mode** DC sweep:

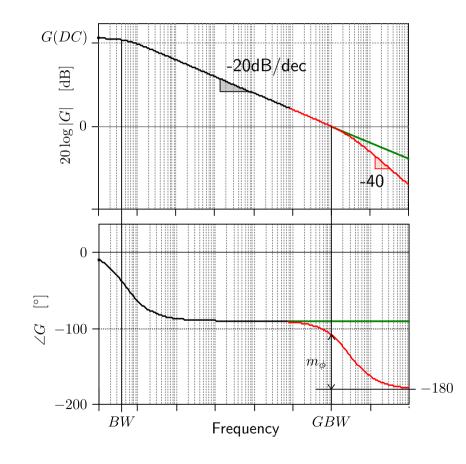

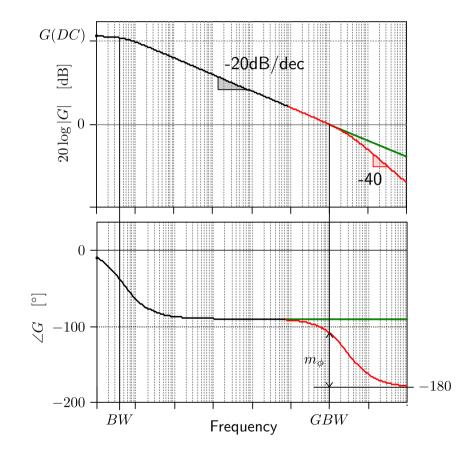

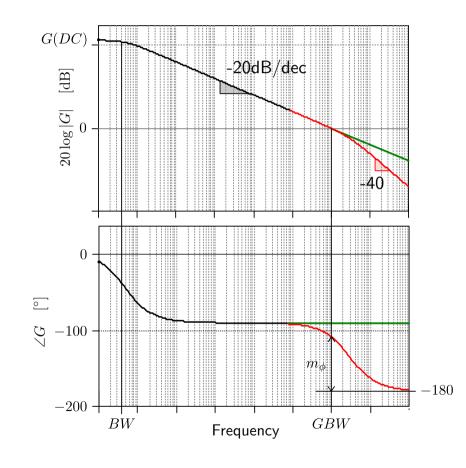

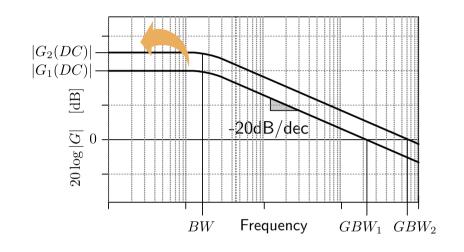

- ► Small signal dynamic figures (ideal):

- Open loop differential DC gain G(DC)  $(\to \infty)$

- $\qquad \qquad \mathsf{Bandwidth} \qquad \qquad BW \quad (\to \infty)$

- Gain-bandwidth product  $GBW \ (\to \infty)$

- Phase margin  $m_{\phi} \ (\rightarrow 90^{\circ})$

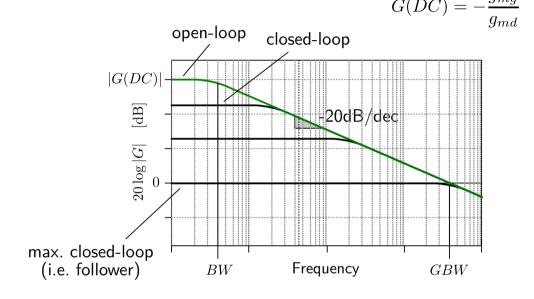

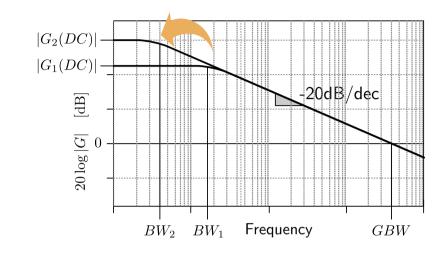

### ► **AC Bode** diagram:

### ► Small signal dynamic figures (ideal):

- Open loop differential DC gain G(DC)  $(\to \infty)$

- $\qquad \qquad \mathsf{Bandwidth} \qquad \qquad BW \quad (\to \infty)$

- Gain-bandwidth product  $GBW \ (\to \infty)$

- Phase margin  $m_{\phi} \ (\rightarrow 90^{\circ})$

- **Equivalent input noise**  $v_{neq} \quad (\rightarrow 0)$

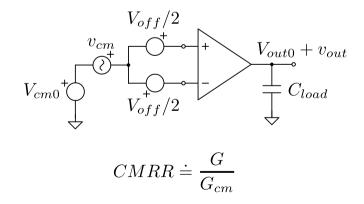

- Common mode rejection ratio CMRR  $(\rightarrow \infty)$

#### ► **AC Bode** diagram:

### Small signal dynamic figures (ideal):

- Open loop differential DC gain G(DC)  $(\to \infty)$

- lacksquare Bandwidth  $BW \ \ ( o \infty)$

- Gain-bandwidth product  $GBW \ \ (\to \infty)$

- Phase margin  $m_{\phi} \ (\rightarrow 90^{\circ})$

- **Equivalent input noise**  $v_{neq} \quad (\rightarrow 0)$

- Common mode rejection ratio CMRR  $(\rightarrow \infty)$

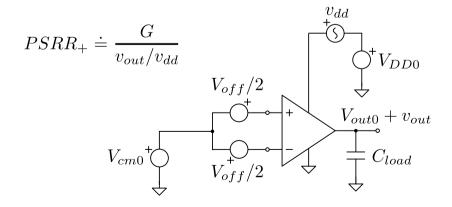

- Power supply rejection ratio  $PSRR_{+/-}(\to \infty)$

#### ► **AC Bode** diagram:

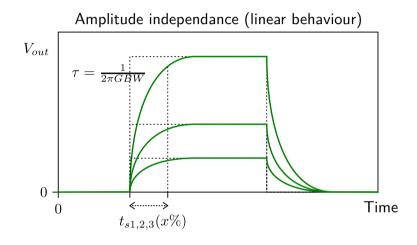

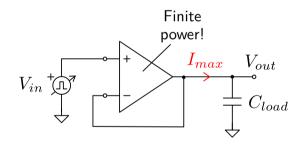

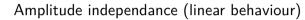

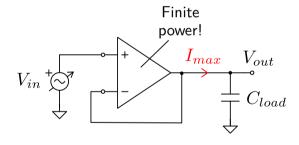

- ► Large signal dynamic figures (ideal)

- Settling time

$t_s(x\%) \quad (\to 0)$

► Transient **step response**:

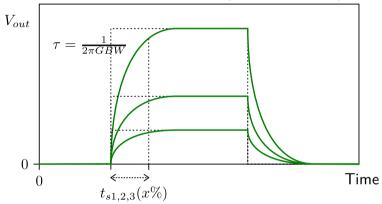

- ► Large signal dynamic figures (ideal)

- Settling time

$t_s(x\%) \quad (\to 0)$

Slew rate

$SR_{+/-} \quad (\to \infty)$

#### ► Transient **step response**:

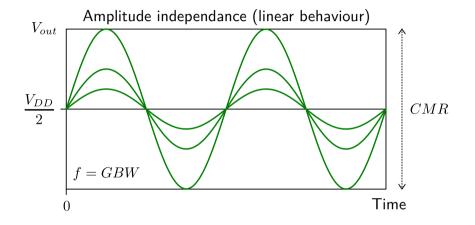

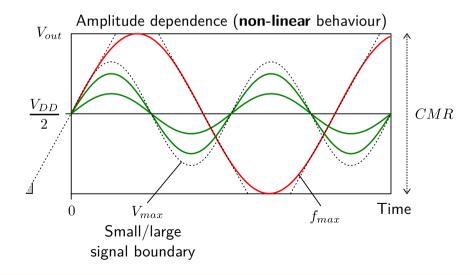

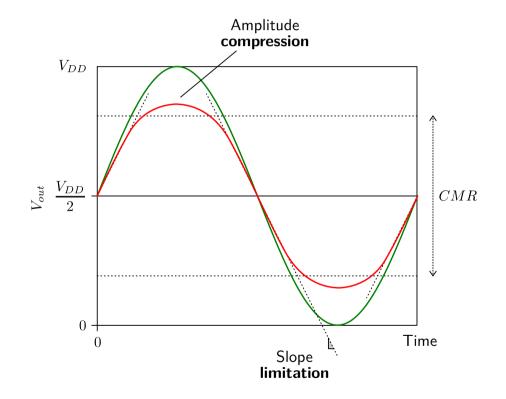

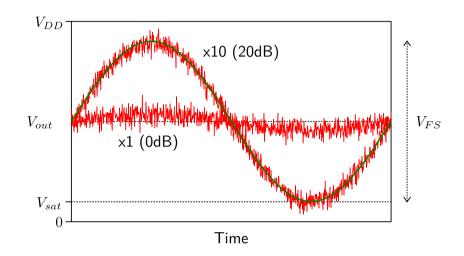

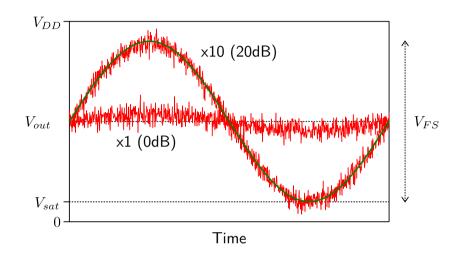

#### Amplitude dependence (non-linear behaviour)

- ► Large signal dynamic figures (ideal)

- Settling time

$$t_s(x\%) \quad (\to 0)$$

- Slew rate

- $SR_{+/-} \quad (\to \infty)$

- Maximum frequency  $f_{max} \quad (\to \infty)$

$$f_{max} = \frac{SR}{\pi CMR} \ll GBW$$

$$V_{max} = \frac{SR}{2\pi GRW} \ll CMR$$

$SR \doteq \min(SR_+, SR_-)$

#### ► Transient **harmonic response**:

### ► Large signal dynamic figures (ideal)

- Settling time

- $t_s(x\%) \quad (\to 0)$

- Slew rate

- $SR_{+/-} \quad (\to \infty)$

- Maximum frequency  $f_{max}$   $(\to \infty)$

- Total harmonic distortion  $THD \quad (\rightarrow 0)$

#### ► Transient **harmonic response**:

15/110

Both static and dynamic non-linearity = **signal distortion**

CMOS Operational Amplifiers FoM Mono CMFB Folded Cascode Gain Multi-Stage

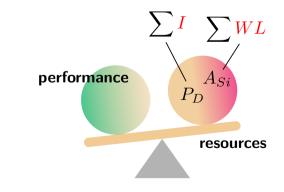

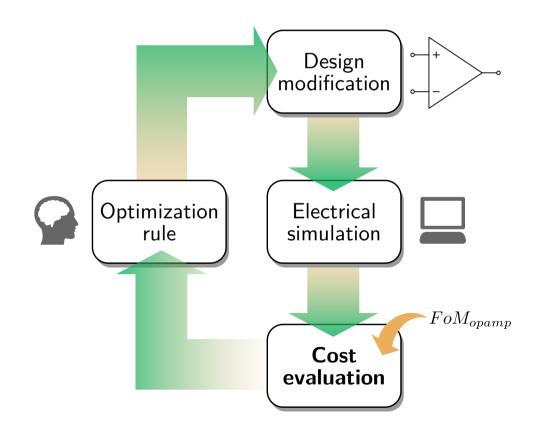

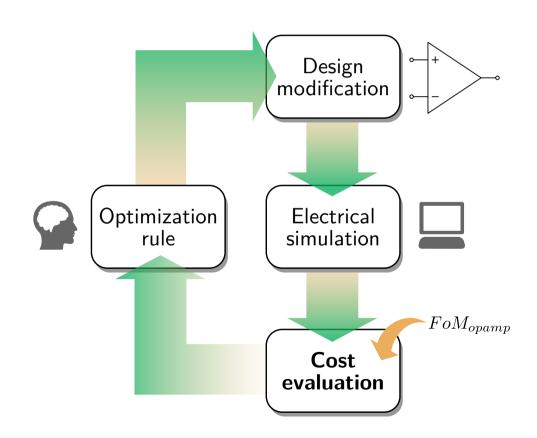

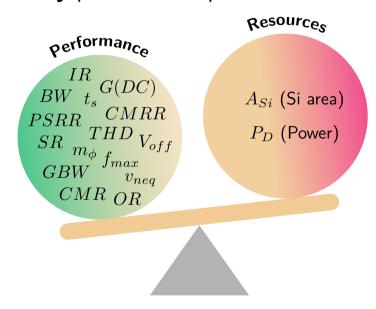

### **OpAmp FoMs**

- ▲ Quantitative design comparison

- ▲ Useful in circuit **optimization**:

### **OpAmp FoMs**

- ▲ Quantitative design comparison

- ▲ Useful in circuit **optimization**:

**▼ Too many** performance parameters!

▼ Application **specific** FoMs...

$$FoM_{opamp} \equiv \left\{ \begin{array}{ll} \frac{C_{load}SR}{P_D} & \text{e.g. line buffer} \\ \\ \frac{1}{P_Dv_{neq}^2A_{Si}} & \text{e.g. pre-amplifier} \\ \\ \frac{C_{load}GBW}{P_D} & \text{e.g. RF amplifier} \end{array} \right.$$

- 2 The Mono-Transistor Amplifier

- 3 Differential Circuits with CMFB

- 4 Folded Amplifiers

- 5 Cascode Topologies

- 6 Gain Enhancement Techniques

- 7 Multi-Stage OpAmps

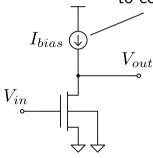

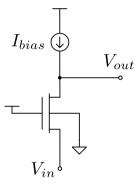

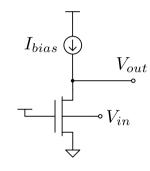

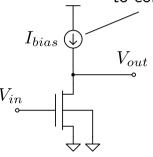

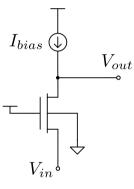

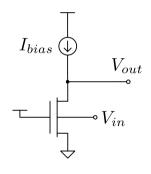

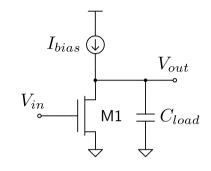

# **Single-Transistor Topologies**

► Operational voltage amplifier (**OpAmp**)?

**Current**-driven bias point to control circuit power

Common source

Common gate

Supposing **forward saturation**, **drain** is selected as output port due to its high impedance (CLM):

**Back** gate

# **Single-Transistor Topologies**

► Operational voltage amplifier (**OpAmp**)?

Current-driven bias point to control circuit power

Power efficiency

Common source

- ightharpoonup Moderate  $G_m/I_D$

- ▲ High input impedance

- ▲ **Inverting** amplifier

Common gate

- $\blacktriangle$  Highest  $G_m/I_D$

- **▼** Low input **impedance**

- **▼ Non-inverting** amplifier

Supposing forward saturation, drain is selected as output port due to its high impedance (CLM):

20/110

Back gate

- ▼ Lowest G<sub>m</sub>/I<sub>D</sub>

- **▼** Low input **impedance**

- ▲ **Inverting** amplifier

- **▼** Latchup

- **▼ Triple**-well required

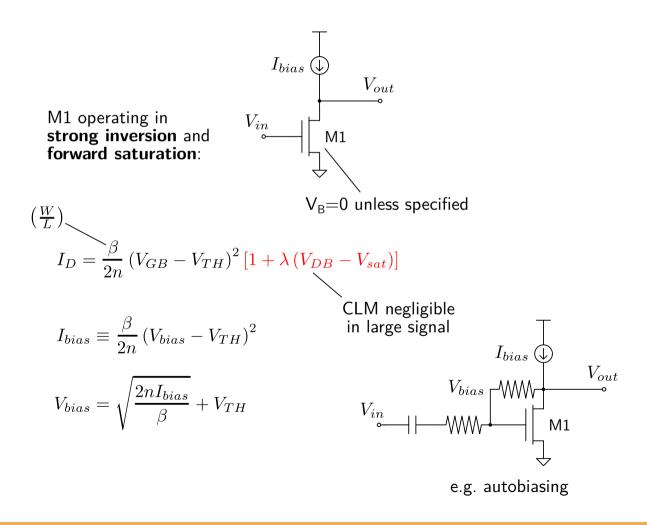

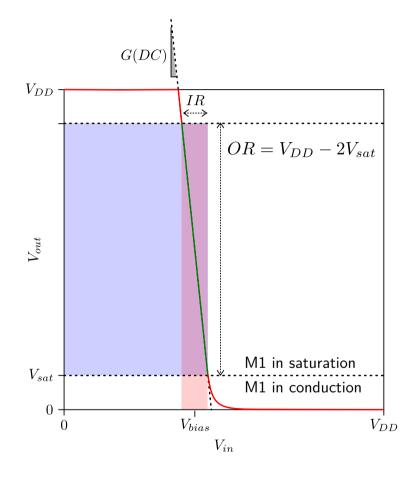

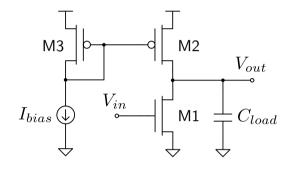

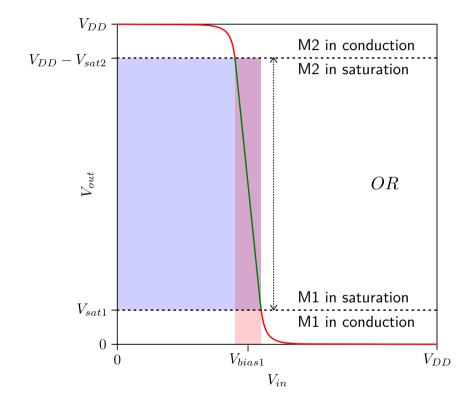

# **Voltage Transfer Curve**

► Large signal analysis of common source amplifier:

$$V_{sat} = \frac{V_{GB} - V_{TH}}{n} = \frac{V_{bias} - V_{TH}}{n} = \sqrt{\frac{2I_{bias}}{n\beta}}$$

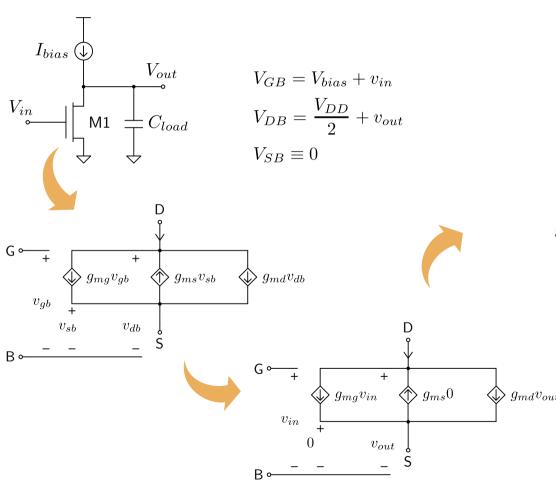

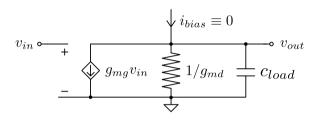

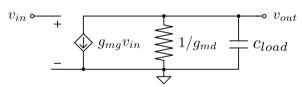

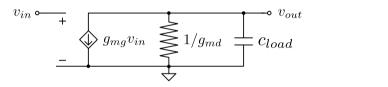

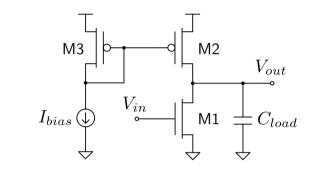

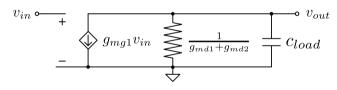

### **Gain and Frequency Response**

Common source small signal analysis:

► **Incremental** equivalent circuit:

M1 strong inversion and forward saturation bias point

$$I_{bias} \gg I_S = 2n\beta U_t^2$$

$V_{bias} \gg V_{TH}$

$V_{out} \gg V_{sat}$

$$\begin{cases} g_{mg} = \sqrt{\frac{2\beta I_D}{n}} \equiv \sqrt{\frac{2\beta I_{bias}}{n}} \\ g_{md} = \lambda I_D \equiv \lambda I_{bias} \end{cases}$$

# **Gain and Frequency Response**

► **Incremental** equivalent circuit:

M1 strong inversion and forward saturation bias point

$$\begin{cases} g_{mg} = \sqrt{\frac{2\beta I_D}{n}} \equiv \sqrt{\frac{2\beta I_{bias}}{n}} \\ g_{md} = \lambda I_D \equiv \lambda I_{bias} \\ \propto \frac{1}{L} \end{cases}$$

► DC voltage gain

$$G \doteq rac{v_{out}}{v_{in}}$$

$G(DC) = -rac{g_{mg}}{g_{md}}$   $rac{\left(rac{W}{L}

ight)\uparrow}{3 ext{dB/oct}}$   $G(DC) = -rac{1}{\lambda}\sqrt{rac{2eta}{nI_{bias}}}\uparrow$   $G(DC) = -rac{1}{\lambda}\sqrt{rac{2eta}{nI_{bias}}} + 3 ext{dB/oct}$

In general, for CMOS amplifiers:

### **Gain and Frequency Response**

► **Incremental** equivalent circuit:

M1 strong inversion and forward saturation bias point

$$\begin{cases} g_{mg} = \sqrt{\frac{2\beta I_D}{n}} \equiv \sqrt{\frac{2\beta I_{bias}}{n}} \\ g_{md} = \lambda I_D \equiv \lambda I_{bias} \\ \propto \frac{1}{L} \end{cases}$$

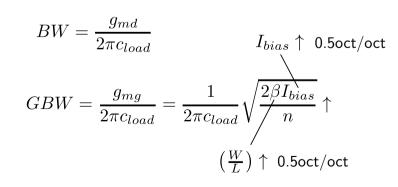

### ► Spectral **bandwidth**

# **Dynamic Range**

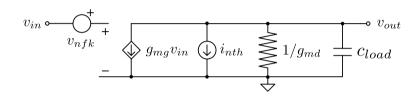

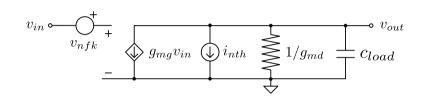

► **Noise** equivalent circuit:

$$\frac{dv_{nfk}^2}{df} = \frac{K_{fk}}{WL} \frac{1}{f} \qquad \frac{di_{nth}^2}{df} = \frac{8}{3} KT n g_{mg}$$

Uncorrelated phenomena and low-frequency:

$$\frac{|G(DC)|^2}{df} = \frac{8}{3}KTn\frac{g_{mg}}{g_{md}^2} + \frac{K_{fk}}{WL} \left(\frac{g_{mg}}{g_{md}}\right)^2 \frac{1}{f}$$

$$v_{nout}^2 = \frac{8}{3}KTn\frac{g_{mg}}{g_{md}^2}\underbrace{(f_2 - f_1)}_{BW} + \frac{K_{fk}}{WL}\left(\frac{g_{mg}}{g_{md}}\right)^2 \ln\frac{f_2}{f_1}$$

► **Thermal** noise contribution only (f > flicker corner):

Equivalent input noise:

$$v_{out} = v_{nout} + G(v_{in} - v_{out})$$

$$v_{out} = \frac{Gv_{in} + v_{nout}}{1 + G} \simeq v_{in} + \underbrace{\frac{v_{nout}}{G}}_{v_{nin}}$$

► **Noise** equivalent circuit:

$$\frac{dv_{nfk}^2}{df} = \frac{K_{fk}}{WL} \frac{1}{f} \qquad \frac{di_{nth}^2}{df} = \frac{8}{3} KT n g_{mg}$$

$$v_{nout}^2 = \frac{8}{3}KTn\frac{g_{mg}}{g_{md}^2}\underbrace{(f_2 - f_1)}_{BW} + \frac{K_{fk}}{WL}\left(\frac{g_{mg}}{g_{md}}\right)^2 \ln\frac{f_2}{f_1}$$

**Thermal** noise contribution only (f > flicker corner):

$$v_{nin}^2 \doteq \frac{v_{nout}^2}{|G(DC)|^2} = \frac{8}{3} \frac{KTn}{g_{mg}} BW = \frac{8}{3} \frac{KTn^{3/2}}{\sqrt{2\beta}} \frac{BW}{\sqrt{I_{bias}}}$$

$$DR = \left(\frac{V_{FS}/2\sqrt{2}}{v_{nin}}\right)^2 = \frac{3\sqrt{2}}{64} \frac{(V_{DD} - 2V_{sat})^2}{KTBW} \sqrt{\frac{\beta I_{bias}}{n^3}} \uparrow$$

$$T \downarrow 3\text{dB/oct}$$

► Similar performance analysis:

All operating in **strong inversion** and forward **saturation** bias points:

$$V_{sat1} = \sqrt{\frac{2I_{bias}}{n\beta_1}}$$

$V_{sat2} = \sqrt{\frac{2I_{bias}}{n\beta_2}}$   $\left(\frac{W}{L}\right)_2$

► Large signal **VTC**:

$$OR = V_{DD} - V_{sat1} - V_{sat2}$$

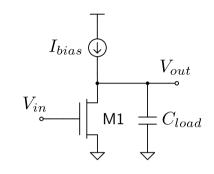

### **Full CMOS Circuit**

► Similar performance analysis:

All operating in **strong inversion** and forward **saturation** bias points:

$$\left(\frac{W}{L}\right)_x \begin{cases} g_{mgx} = \sqrt{\frac{2\beta_x I_{bias}}{n}} \\ L_x \end{cases}$$

$$g_{mdx} = \lambda_x I_{bias}$$

► Small signal **gain** and **bandwidth**:

$$G(DC) = -\frac{g_{mg1}}{g_{md1} + g_{md2}} \qquad \left(\frac{W}{L}\right)_1 \uparrow 3 \text{dB/oct}$$

$$G(DC) = -\frac{1}{\lambda_1 + \lambda_2} \sqrt{\frac{2\beta_1'}{nI_{bias}}} \uparrow$$

$$6 \text{dB/oct } L_{1,2} \uparrow \qquad I_{bias} \uparrow 3 \text{dB/oct}$$

$$BW=rac{g_{md1}+g_{md2}}{2\pi c_{load}}$$

$I_{bias}\uparrow 0.5$ oct/oct  $GBW=rac{g_{mg1}}{2\pi c_{load}}=rac{1}{2\pi c_{load}}\sqrt{rac{2eta_1 I_{bias}}{n}}\uparrow \left(rac{W}{L}

ight)_1\uparrow 0.5$ oct/oct

- 1 OpAmp Figures of Merit

- 2 The Mono-Transistor Amplifier

- 3 Differential Circuits with CMFB

- 4 Folded Amplifiers

- 5 Cascode Topologies

- 6 Gain Enhancement Techniques

- 7 Multi-Stage OpAmps

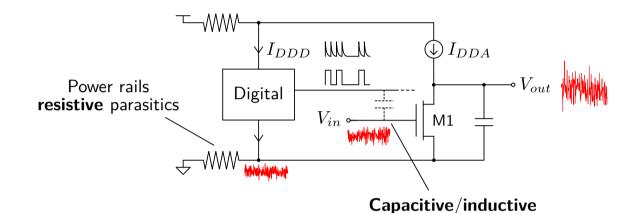

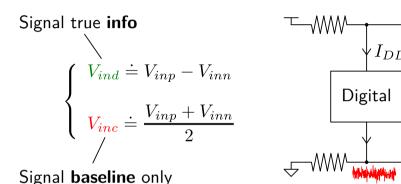

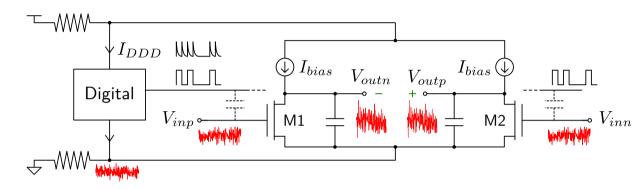

**Single-ended** OpAmps:

- ▲ Compact **area** and **power**

- **▼** Poor **signal integrity**

- Dynamic sources of **interference**:

- Large signals (e.g. digital states)

- Power supply currents

- EM fields

coupling parasitics

- Temperature gradients

- Mechanical stress

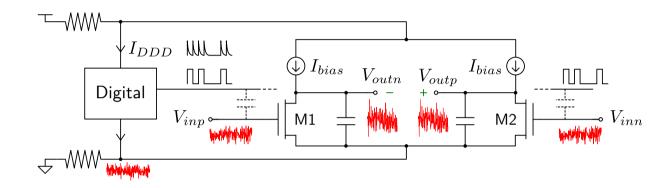

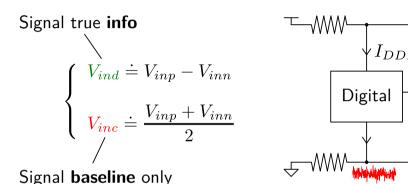

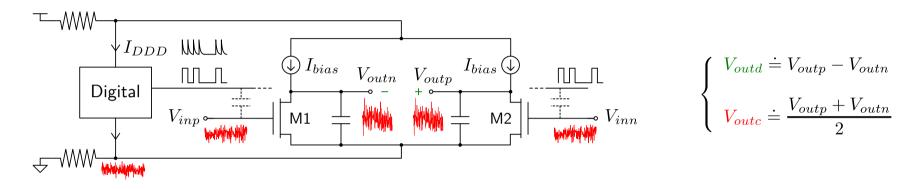

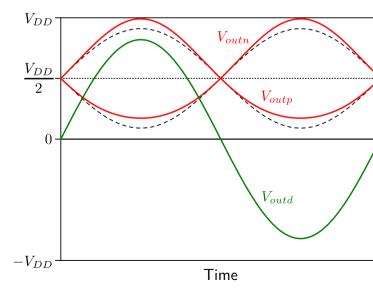

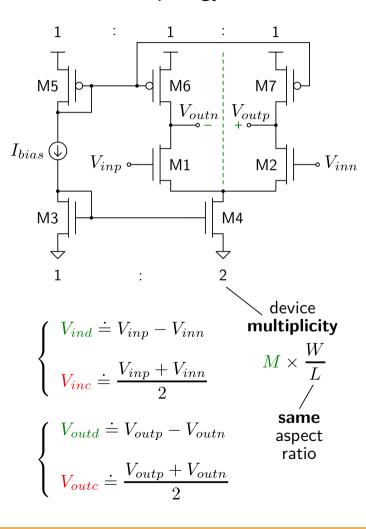

**▶ Pseudo-differential** OpAmps:

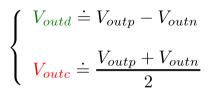

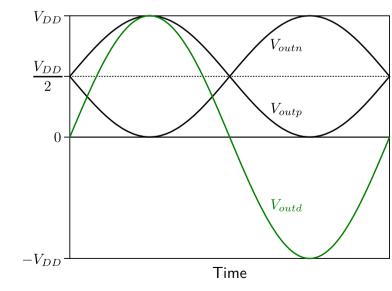

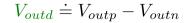

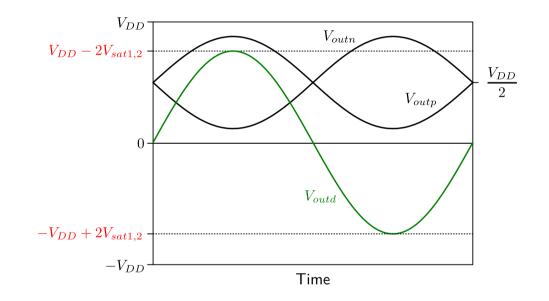

$$\begin{cases} V_{outd} \doteq V_{outp} - V_{outn} \\ V_{outc} \doteq \frac{V_{outp} + V_{outn}}{2} \end{cases}$$

- ▲ Interference **rejection**

- **▼ Area** and **power** overheads (x2)

#### **Pseudo-differential** OpAmps:

- ▲ Interference rejection

- **▼ Area** and **power** overheads (x2)

- ▲ Full-scale extension (+6dB)

▼ Noise increase (+3dB)

#### **▶ Pseudo-differential** OpAmps:

$$V_{out} = V_{out} + V_{out}$$

$V_{out} = V_{out} + V_{out}$

$V_{out} = V_{out} + V_{out}$

- ▲ Interference rejection

- **▼ Area** and **power** overheads (x2)

- ▲ Full-scale extension (+6dB) SNR

▼ Noise increase (+3dB) (+3dB)

- ▲ **Distortion** cancellation (even harm.)

- ▼ Limited by device matching

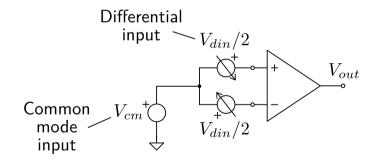

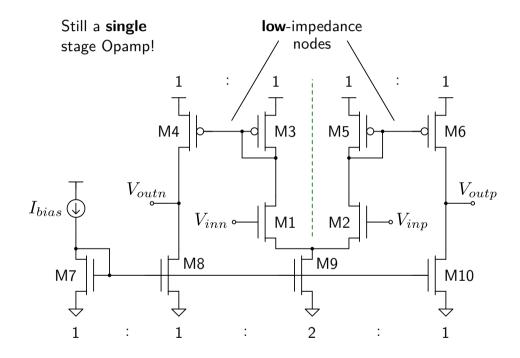

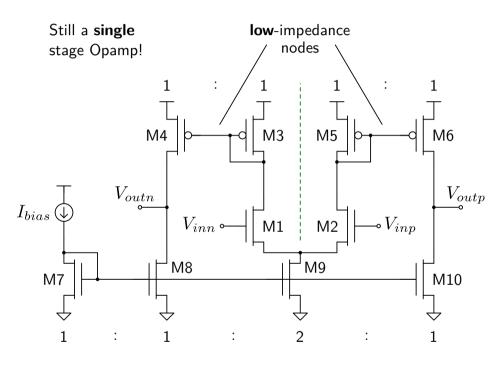

### Fully-Differential OpAmps

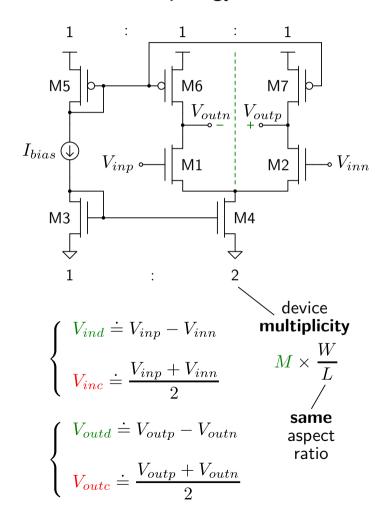

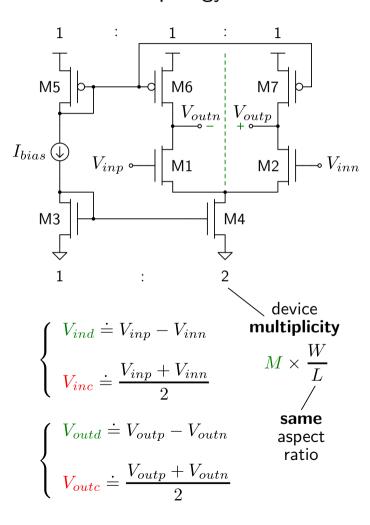

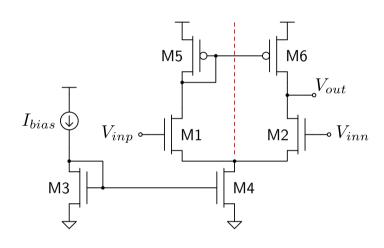

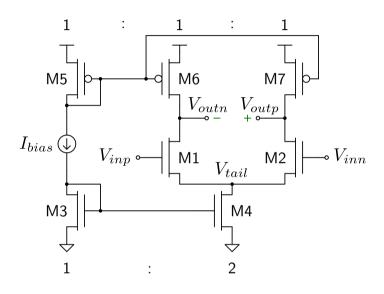

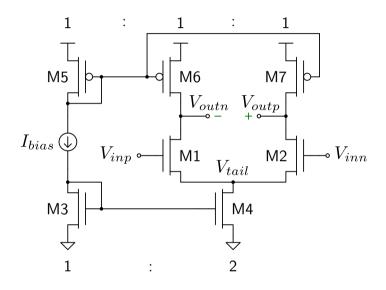

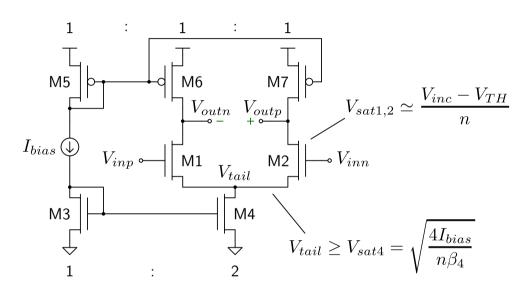

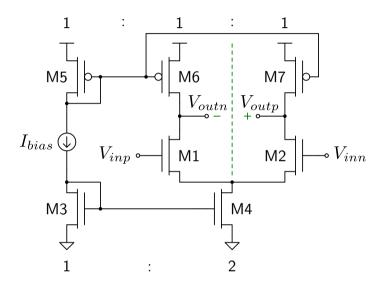

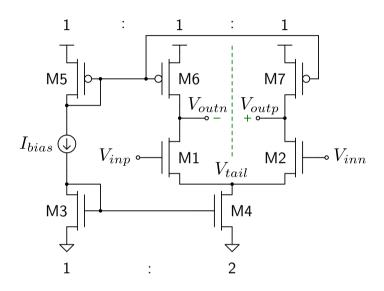

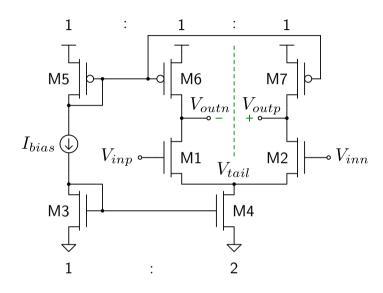

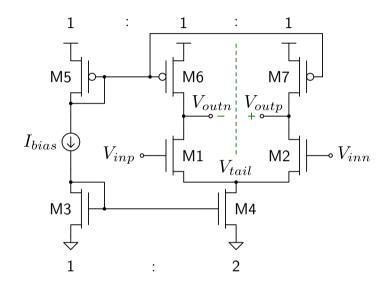

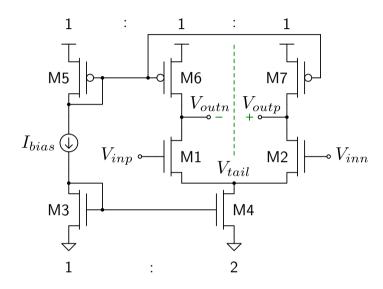

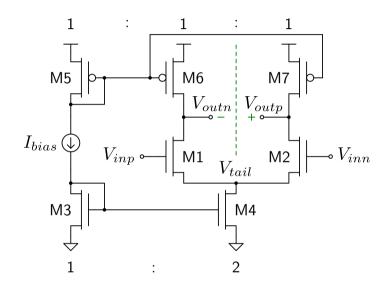

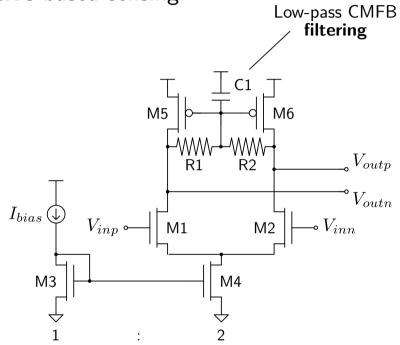

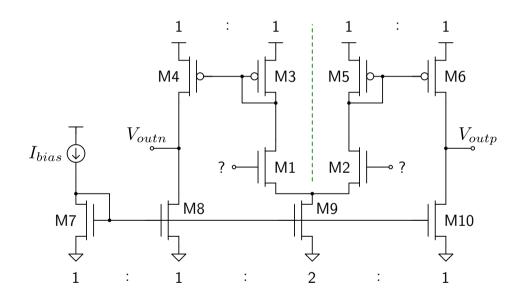

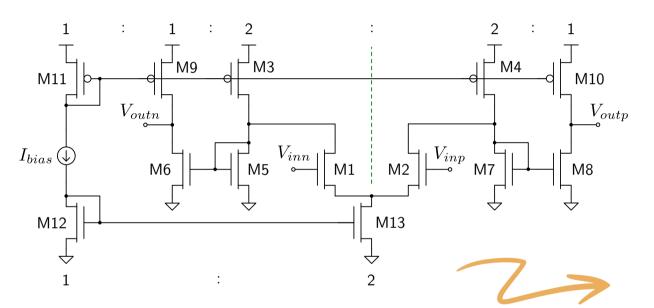

► **Basic** CMOS topology:

# **Fully-Differential OpAmps**

► **Basic** CMOS topology:

Differential input only:

► Basic CMOS topology:

Differential input only:

- ▼ M5-6 current mirror asymmetry

- ▼ Not full **cancellation** of unwanted terms

- ▲ Mostly used for **single-ended** signaling

▶ Basic CMOS topology:

$$\left\{egin{array}{l} V_{ind} \doteq V_{inp} - V_{inn} \ & V_{inc} \doteq rac{V_{inp} + V_{inn}}{2} \ & V_{outd} \doteq V_{outp} - V_{outn} \ & V_{outc} \doteq rac{V_{outp} + V_{outn}}{2} \end{array}

ight.$$

All operating in strong inversion saturation + neglecting CLM

37/110

$$V_{sat7} = \sqrt{\frac{2I_{bias}}{n\beta_7}}$$

$V_{sat2} \simeq \frac{V_{inc} - V_{TH}}{n}$

F. Serra Graells

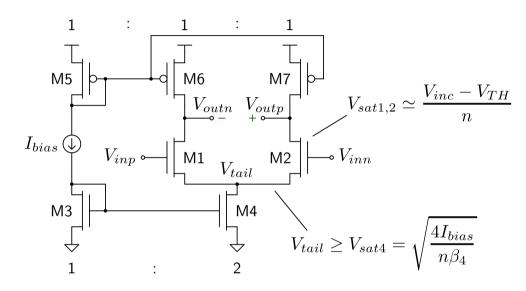

**▶ Basic** CMOS topology:

▼ Reduced **output range**

$$OR = 2V_{DD} - 4V_{sat1,2}$$

$V_{sat1,2} \simeq \frac{V_{inc} - V_{TH}}{n}$

All operating in strong inversion saturation + neglecting CLM

**▶ Basic** CMOS topology:

#### ▼ Reduced **output range**

$$OR = 2V_{DD} - 4V_{sat1.2}$$

$$I_{bias} = \frac{\beta_{1,2}}{2n} \left( V_{inc} - V_{TH} - nV_{tail} \right)^2$$

All operating in strong inversion saturation + neglecting CLM

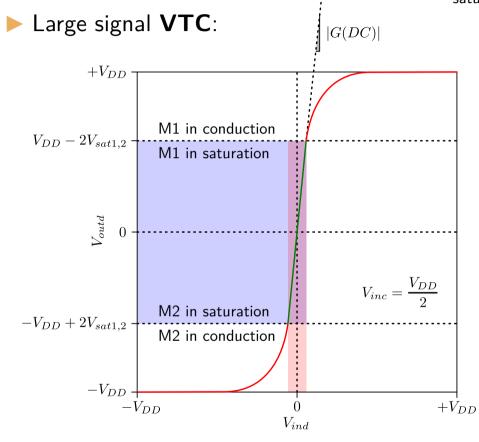

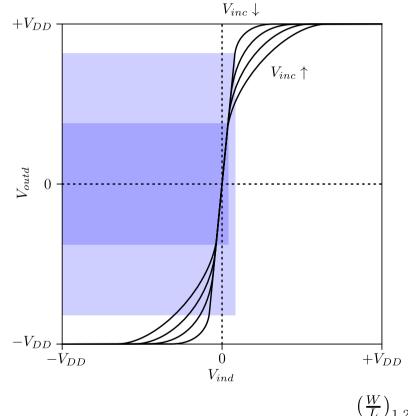

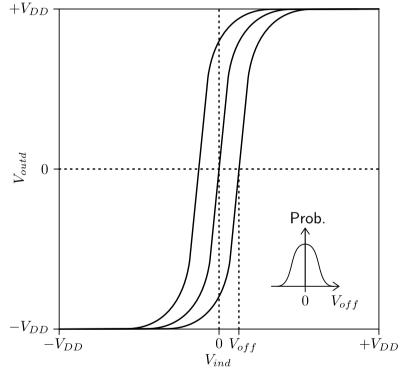

Large signal **VTC**:

► Basic CMOS topology:

#### ▼ Reduced **output range**

$$OR = 2V_{DD} - 4V_{sat1,2}$$

$$I_{bias} = \frac{\beta_{1,2}}{2n} \left( V_{inc} - V_{TH} - nV_{tail} \right)^2$$

$$V_{sat1,2} = \sqrt{\frac{2I_{bias}}{n\beta_{1,2}}} + V_{sat4}$$

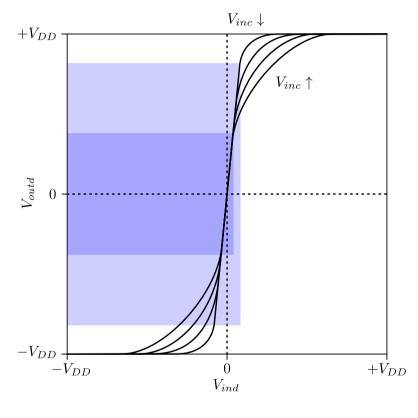

### ► Large signal **VTC**:

40/110

All operating in strong inversion saturation + neglecting CLM

$$OR = 2V_{DD} - 4\sqrt{\frac{2I_{bias}}{n\beta_{un}}} \left[ \sqrt{\left(\frac{L}{W}\right)_{1,2}} + \sqrt{2\left(\frac{L}{W}\right)_{4}} \right] \uparrow \left(\frac{\frac{W}{L}}{L}\right)_{4} \uparrow$$

Basic CMOS topology:

- ▼ Reduced **output range**

- ▼ More **offset** contributions

$$\sigma^{2}(V_{off}) = \sigma^{2}(\Delta V_{TH1,2}) + \left(\frac{g_{mg3,4}}{g_{mg1,2}}\right)^{2} \sigma^{2}(\Delta V_{TH6,7}) = \frac{A_{VTHN}^{2}}{(WL)_{1,2}} + \underbrace{\frac{\beta_{up}}{\beta_{un}} \frac{(W/L)_{6,7}}{(W/L)_{1,2}} \frac{A_{VTHP}^{2}}{(WL)_{6,7}}}_{(WL)_{6,7}} \quad \downarrow \quad (WL)_{1,2}$$

All operating in strong inversion saturation + neglecting CLM

Large signal **VTC**:

► Basic CMOS topology:

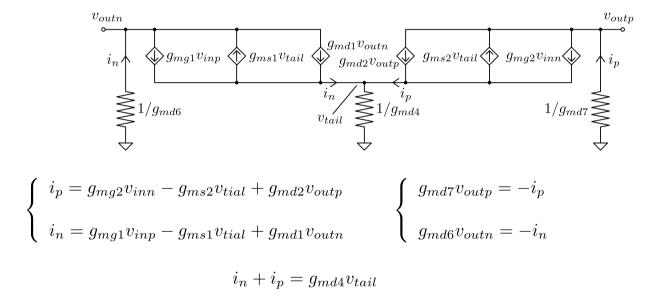

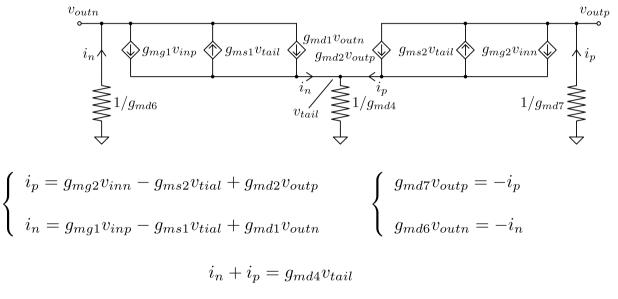

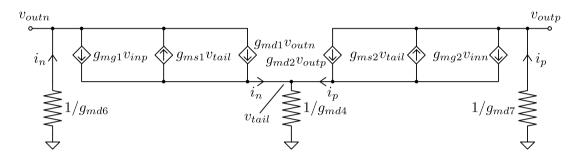

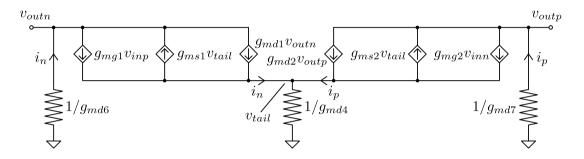

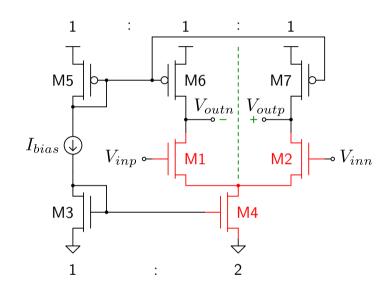

► Small signal **differential** and **common** DC gains:

$$\begin{split} (g_{md7} + g_{md2})v_{outp} - (g_{md6} + g_{md1})v_{outn} + \frac{g_{ms1} - g_{ms2}}{g_{ms1} + g_{ms2} + g_{md4}}(g_{md2}v_{outp} + g_{md1}v_{outn}) = \\ & = g_{mg1}v_{inp} - g_{mg2}v_{inn} + \frac{g_{ms2} - g_{ms1}}{g_{ms1} + g_{ms2} + g_{md4}}(g_{mg1}v_{inp} + g_{mg2}v_{inn}) \end{split}$$

► Basic CMOS topology:

► Small signal **differential** and **common** DC gains:

$$\begin{array}{c} \textbf{differential output} \\ v_{outd} \\ (g_{md7} + g_{md2})v_{outp} - (g_{md6} + g_{md1})v_{outn} + \frac{g_{ms1} - g_{ms2}}{g_{ms1} + g_{ms2} + g_{md4}} (g_{md2}v_{outp} + g_{md1}v_{outn}) = \\ \\ = g_{mg1}v_{inp} - g_{mg2}v_{inn} + \frac{g_{ms2} - g_{ms1}}{g_{ms1} + g_{ms2} + g_{md4}} (g_{mg1}v_{inp} + g_{mg2}v_{inn}) \\ \\ v_{ind} \\ \\ \textbf{differential input} \\ \end{array}$$

**▶ Basic** CMOS topology:

Small signal differential and common DC gains:

▲ Perfect matching (M1=M2 and M6=M7):

$$G_d \doteq \frac{v_{outd}}{v_{ind}} = \frac{g_{mg1,2}}{g_{md1,2} + g_{md6,7}}$$

$$G_c \doteq \frac{v_{outd}}{v_{inc}} \equiv 0$$

$$CMRR \doteq \frac{G_d}{G_c} = \infty$$

$$(g_{md7}+g_{md2})v_{outp}-(g_{md6}+g_{md1})v_{outn}+\frac{g_{ms1}+g_{ms2}}{g_{ms1}+g_{ms2}+g_{md4}}(g_{md2}v_{outp}+g_{md1}v_{outn})=\\ =g_{mg1}v_{inp}-g_{mg2}v_{inn}+\frac{g_{ms2}+g_{md1}}{g_{ms1}+g_{ms2}+g_{md4}}(g_{mg1}v_{inp}+g_{mg2}v_{inn})\\ v_{ind}\\ \textbf{differential input}$$

Basic CMOS topology:

**Teal matching** (e.g.  $V_{TH1} \neq V_{TH2}$ ):

$$\begin{cases} g_{mg1,2} = \frac{g_{mg1} + g_{mg2}}{2} \\ \Delta g_{mg1,2} = \frac{g_{mg1} - g_{mg2}}{2} \\ \Delta g_{mg1,2} = \frac{g_{mg1} - g_{mg2}}{2} \end{cases} \qquad CMRR = \frac{g_{mg1,2}}{2\Delta g_{mg1,2}} \left(\frac{2ng_{mg1,2}}{g_{md4}} + 1\right)$$

$$CMRR = \frac{g_{mg1,2}}{2\Delta g_{mg1,2}} \left(\frac{2ng_{mg1,2}}{g_{md4}} + 1\right)$$

Small signal differential and common DC gains:

▲ **Perfect matching** (M1=M2 and M6=M7):

$$G_d \doteq \frac{v_{outd}}{v_{ind}} = \frac{g_{mg1,2}}{g_{md1,2} + g_{md6,7}}$$

$$G_c \doteq \frac{v_{outd}}{v_{inc}} \equiv 0$$

$$CMRR \doteq \frac{G_d}{G_c} = \infty$$

$$CMRR = \frac{g_{mg1,2}}{2\Delta g_{mg1,2}} \left(\frac{2ng_{mg1,2}}{g_{md4}} + 1\right) \quad \uparrow$$

$$\text{Matching} \uparrow \qquad \text{Tail current sink impedance} \uparrow$$

$$\frac{2\Delta g_{mg1,2}}{g_{mg1,2}+g_{md4}/n}(2g_{mg1,2}v_{inc}+\Delta g_{mg1,2}v_{ind})$$

**▶ Basic** CMOS topology:

- ▼ Reduced **output range**

- **▼ Matching** is critical

#### ► Summary of **design guidelines**:

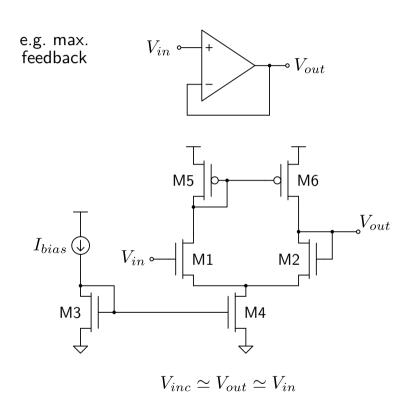

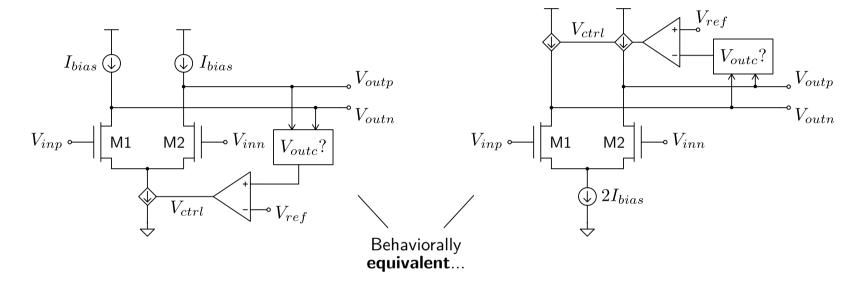

## **Common-Mode Output Issue**

► **Single-ended** differential OpAmps:

▲ Well-defined and stable common-mode level

► Fully-differential OpAmps:

▼ Specific auxiliary **control circuitry** is needed in practice...

### **Common-Mode Output Issue**

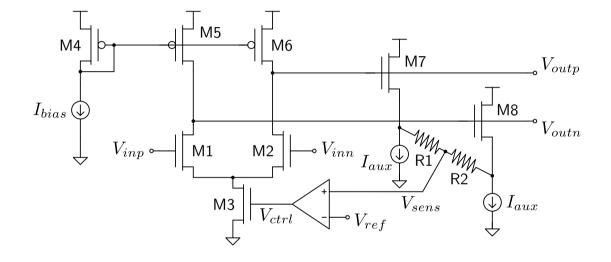

► Common-mode feedback (**CMFB**) loop:

- CMFB control functionality:

- **Sensing** common-mode output

- Computing error according to reference level

- Applying needed common-mode correction

- Not to be confused with CMRR!

- Multi-stage OpAmps require one CMFB loops for each stage

- CMFB control design?

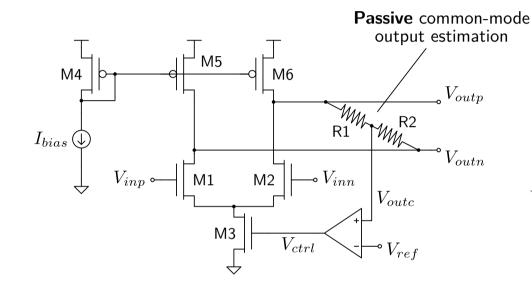

► **Resistive**-based sensing:

$$V_{outc} = \frac{R_2}{R_1 + R_2} V_{outp} + \frac{R_1}{R_1 + R_2} V_{outn}$$

$$V_{outc}|_{R_1 \equiv R_2} = \frac{V_{outp} + V_{outn}}{2}$$

► **Resistive**-based sensing:

$$V_{outc} = \frac{R_2}{R_1 + R_2} V_{outp} + \frac{R_1}{R_1 + R_2} V_{outn}$$

$$V_{outc}|_{R_1 \equiv R_2} = \frac{V_{outp} + V_{outn}}{2}$$

- ▲ OpAmp original **OR** is preserved

- **▼** Resistive **extra loading**...

...or limited CMFB **bandwidth**

► **Resistive**-based sensing:

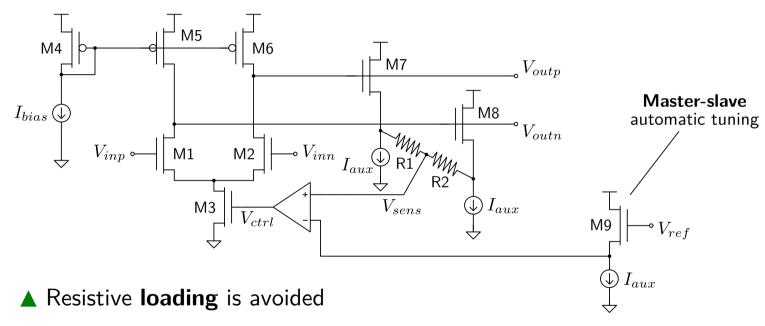

- ▲ Resistive **loading** is avoided

- **▼ OR** severe reduction

- **▼ Power** consumption overhead

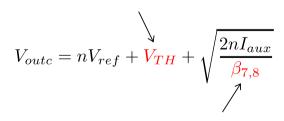

- ▼ Common-mode output level is **technology** dependent!

**Resistive**-based sensing:

- **▼ OR** severe reduction

- **▼ Power** consumption overhead

- **▼** Common-mode output level is **technology** dependent!

$V_{outc} \equiv V_{ref}$

► **Resistive**-based sensing:

$$V_{outc} = V_{DD} - V_{TH} - \sqrt{\frac{2nI_{bias}}{eta_{5,6}}}$$

- ▲ Compact circuit solution

- ▲ No **power** consumption overhead

- ▼ Common-mode output defined by **technology**

- ▼ Strong **OR** reduction

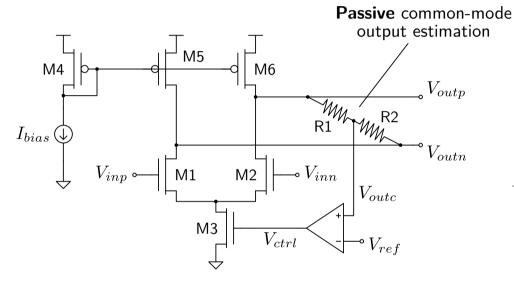

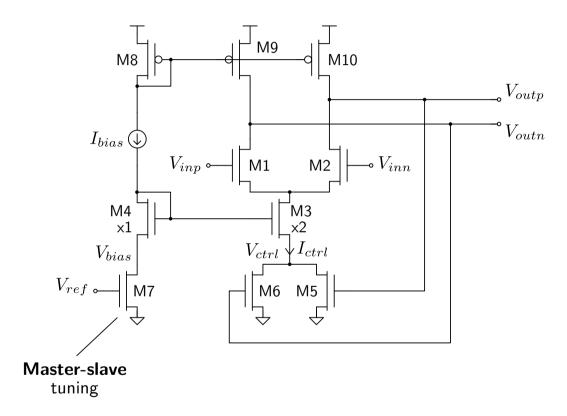

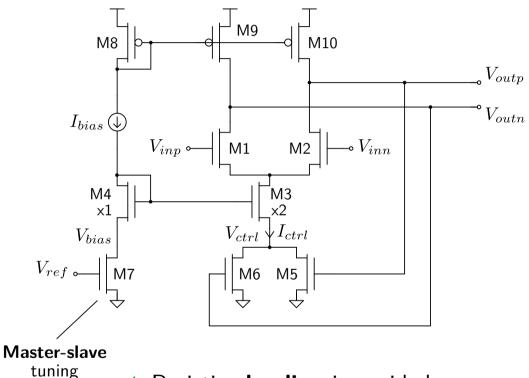

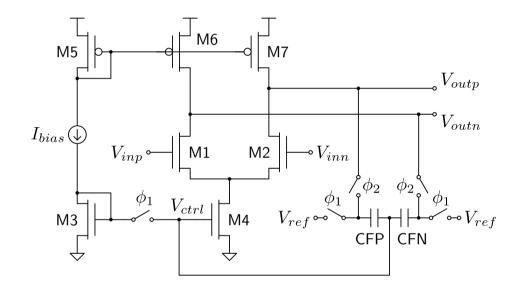

► MOS-based sensing:

Supposing M5, M6 and M7 working in deep conduction:

$$I_{ctrl} = \beta_5 \left( V_{outp} - V_{TH} + n \frac{V_{ctrl}}{2} \right) V_{ctrl} +$$

$$\beta_6 \left( V_{outn} - V_{TH} + n \frac{V_{ctrl}}{2} \right) V_{ctrl}$$

By **CMFB symmetry** (M5=M6):

$$I_{ctrl} = f(\underbrace{V_{outp} + V_{outn}}_{\propto V_{outd}})$$

$$\frac{dI_{ctrl}}{dV_{outd}} \equiv 0$$

By bias symmetry (M5|6=M7 and M3=M4):

$$V_{ctrl} \equiv V_{bias}$$

$I_{ctrl} \equiv 2I_{bias}$   $V_{outc} \equiv V_{ref}$

► MOS-based sensing:

- ▲ Resistive **loading** is avoided

- ▲ No **power** consumption overhead

Supposing M5, M6 and M7 working in deep conduction:

$$I_{ctrl} = \beta_5 \left( V_{outp} - V_{TH} + n \frac{V_{ctrl}}{2} \right) V_{ctrl} +$$

$$\beta_6 \left( V_{outn} - V_{TH} + n \frac{V_{ctrl}}{2} \right) V_{ctrl}$$

By **CMFB symmetry** (M5=M6):

$$I_{ctrl} = f(\underbrace{V_{outp} + V_{outn}}_{\propto V_{outd}})$$

$$\frac{dI_{ctrl}}{dV_{outd}} \equiv 0$$

By bias symmetry (M5|6=M7 and M3=M4):

$$V_{ctrl} \equiv V_{bias}$$

$I_{ctrl} \equiv 2I_{bias}$   $V_{outc} \equiv V_{ref}$

- ▲ Negligible **OR** reduction

- ▲ **Technology** compensation

- ▼ Gain non-linearity

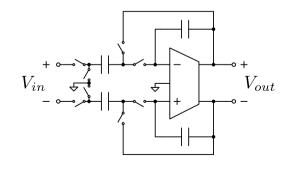

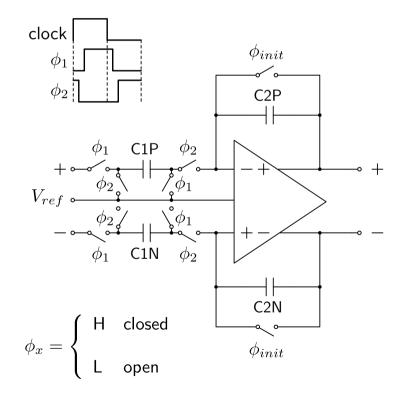

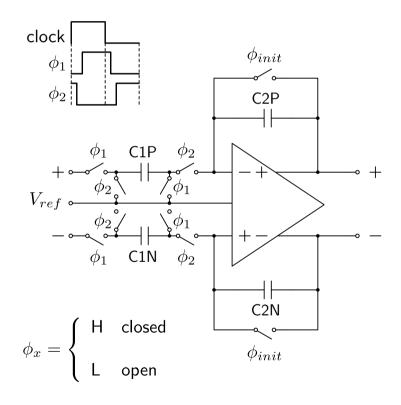

### **Discrete-Time CMFB**

► Switched-capacitor (**SC**) implementation:

e.g. fully-differential **integrator** stage

### **Discrete-Time CMFB**

► Switched-capacitor (**SC**) implementation:

e.g. fully-differential integrator stage

- ► Capacitive CMFB sensing

- ▲ Reduced **power** overheads

- ▼ Low loop-gain

- 2 The Mono-Transistor Amplifier

- 3 Differential Circuits with CMFB

- 4 Folded Amplifiers

- 5 Cascode Topologies

- 6 Gain Enhancement Techniques

- 7 Multi-Stage OpAmps

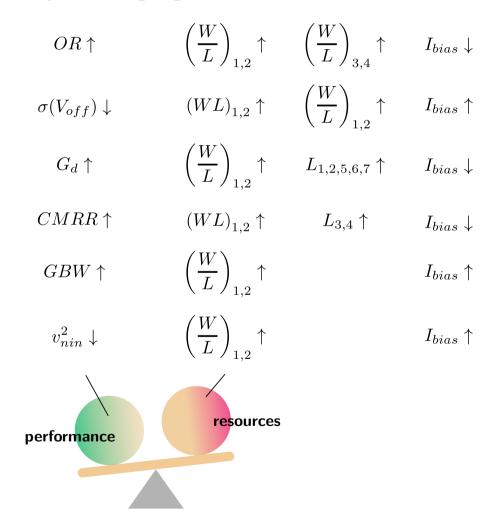

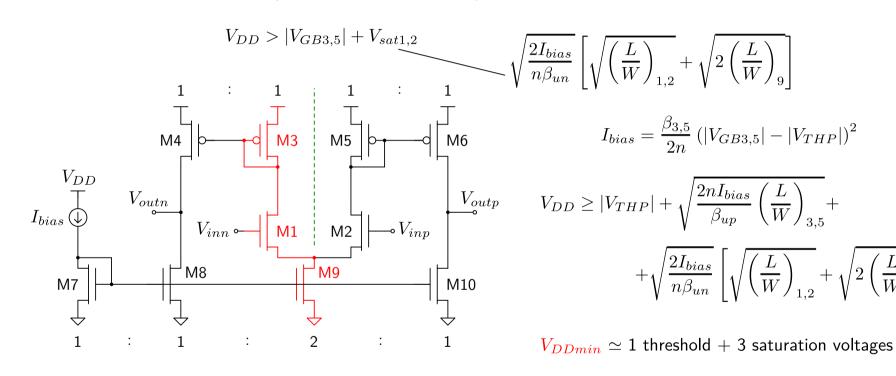

### **Output Range Issue**

▶ **Basic** fully-differential topology (not showing CMFB):

- ▼ **OR** improvement requires very large aspect ratios!

- ▼ Not compatible with other optimization rules (e.g. CMRR)

$$OR = 2V_{DD} - 4\sqrt{\frac{2I_{bias}}{n\beta_{un}}} \left[ \sqrt{\left(\frac{L}{W}\right)_{1,2}} + \sqrt{2\left(\frac{L}{W}\right)_{4}} \right] \uparrow \qquad \left(\frac{W}{L}\right)_{1,2} \uparrow \qquad \left(\frac{W}{L}\right)_{4} \uparrow$$

# **Folded Topologies**

► Fully-differential **folded** OpAmp (not showing CMFB):

### **Folded Topologies**

► Fully-differential **folded** OpAmp (not showing CMFB):

- ▼ Static **power** consumption (x2)

- **▼** Device silicon **area** (x2)

All operating in strong inversion saturation + neglecting CLM

► Fully-differential **folded** OpAmp (not showing CMFB):

All operating in strong inversion saturation + neglecting CLM

$$V_{sat10} < V_{outp} < V_{DD} - V_{sat6}$$

$$V_{sat10} = \sqrt{\frac{2I_{bias}}{n\beta_{10}}} \qquad V_{sat6} = \sqrt{\frac{2I_{bias}}{n\beta_{6}}}$$

$$V_{outd} \doteq V_{outp} - V_{outn}$$

$$OR = 2V_{DD} - 4\sqrt{\frac{2I_{bias}}{n \min\left(\beta_{un} \left(\frac{W}{L}\right)_{8,10}, \beta_{up} \left(\frac{W}{L}\right)_{4,6}\right)}}$$

- $\blacksquare$  Static **power** consumption (x2)

- **▼** Device silicon **area** (x2)

▲ Full-scale **OR** optimization

► Fully-differential **folded** OpAmp (not showing CMFB):

All operating in strong inversion saturation + neglecting CLM

- **▼** Static **power** consumption (x2)

- **▼** Device silicon **area** (x2)

- ▲ Full-scale **OR** optimization

- ▼ High **supply voltage** needed...

### **Folded Topologies**

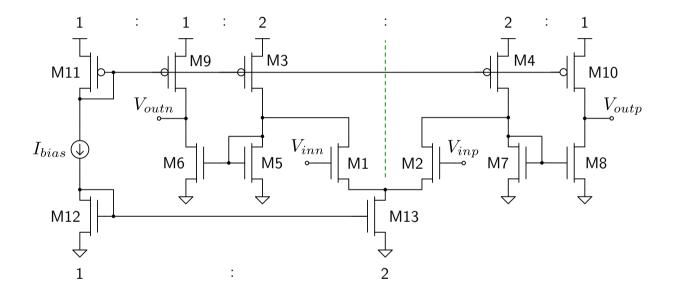

► Fully-differential **dual folded** OpAmp (not showing CMFB):

- ▼ Static **power** consumption (x3)

- **▼** Device silicon **area** (x3)

► Fully-differential **dual folded** OpAmp (not showing CMFB):

All operating in strong inversion saturation + neglecting CLM

$V_{DDmin} \simeq 1$  threshold + 2 saturation voltages

- **▼** Static **power** consumption (x3)

- **▼** Device silicon **area** (x3)

- ▲ Same **OR** optimization

- ▲ Compatible with low **supply voltage**

### **Folded Topologies**

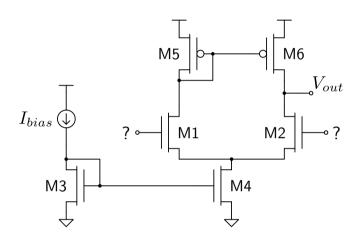

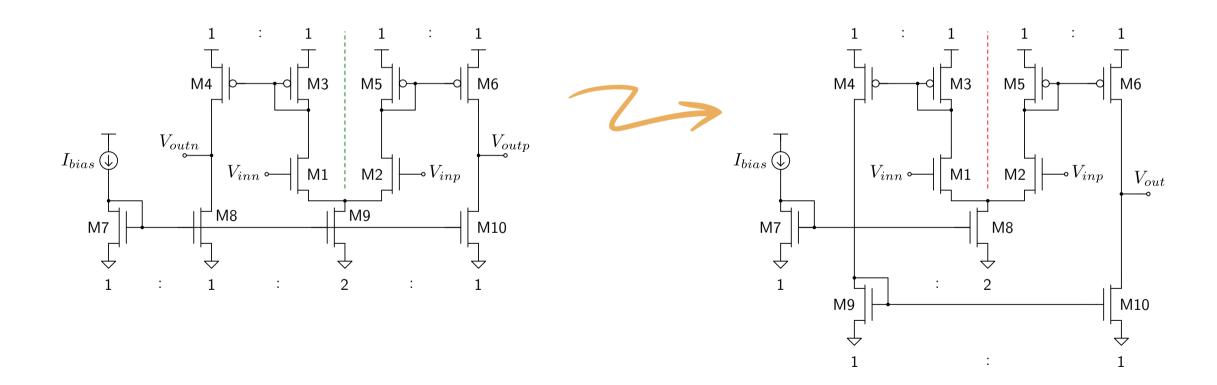

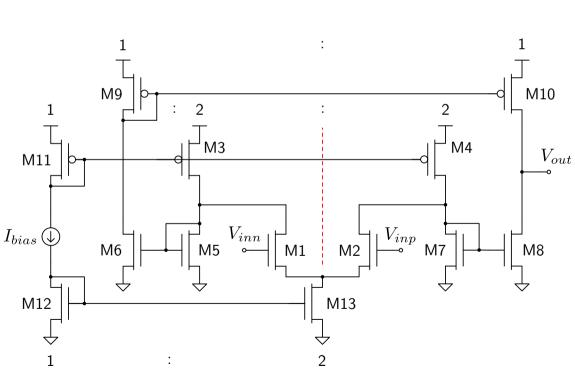

**Single-ended folded** OpAmp counterparts:

# **Folded Topologies**

**► Single-ended folded** OpAmp counterparts:

- 2 The Mono-Transistor Amplifier

- 3 Differential Circuits with CMFB

- 4 Folded Amplifiers

- 5 Cascode Topologies

- 6 Gain Enhancement Techniques

- 7 Multi-Stage OpAmps

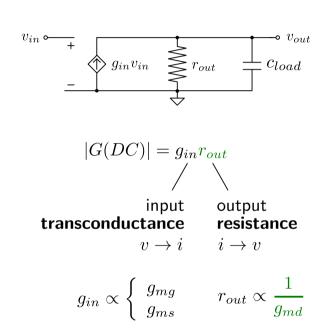

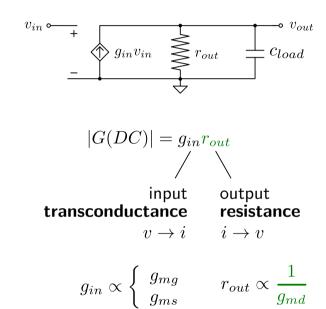

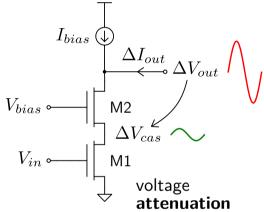

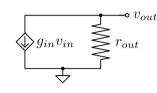

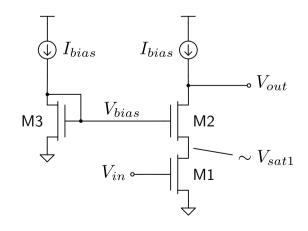

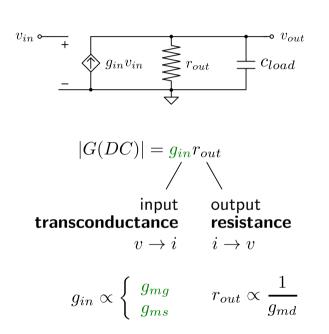

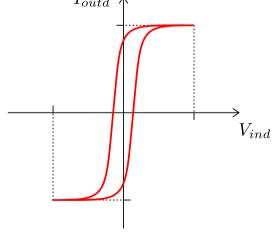

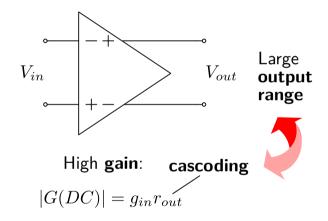

# **Principle Basis**

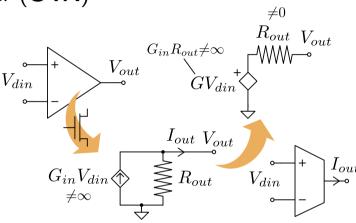

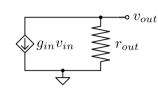

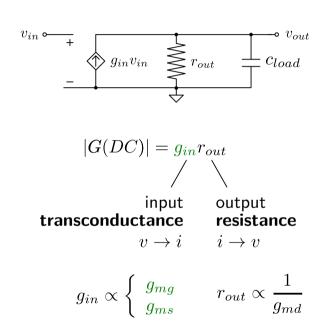

► CMOS OpAmp general **linear model**:

► Enhancement by increasing MOSFET **output impedance**?

# **Principle Basis**

► CMOS OpAmp general **linear model**:

► Enhancement by increasing MOSFET **output impedance**?

$$BW = \frac{1}{2\pi r_{out} c_{load}} \qquad GBW = \frac{g_{in}}{2\pi c_{load}}$$

- ▲ **Gain** improvement:

- Accurate **feedback** functions

- Lower equivalent input **noise**

- ▼ No speed enhancement (GBW)

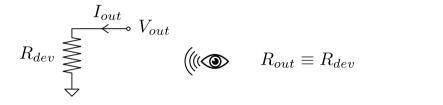

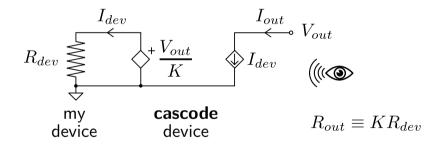

### **Principle of Operation**

Output impedance multiplier:

► Introducing cascoding in **OpAmps**:

71/110

Aplicable to most analog basic building **blocks** (e.g. current mirror, voltage differential pair...)

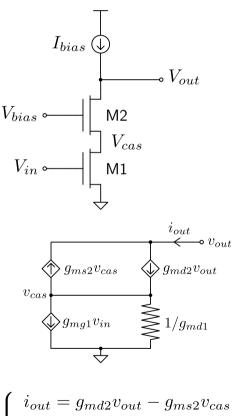

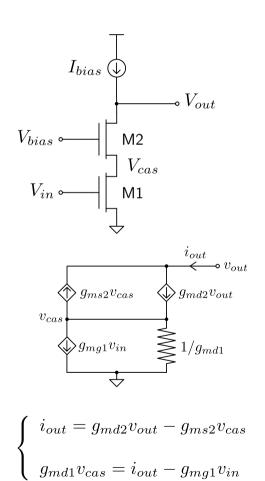

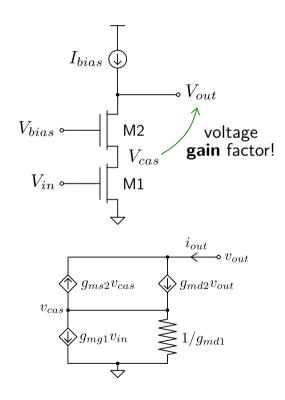

## **Basic Cascode OpAmp**

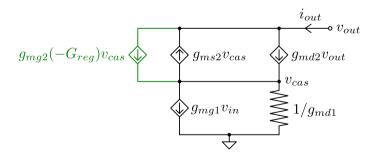

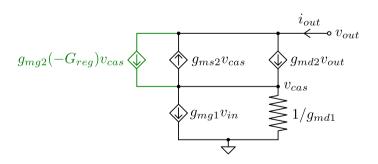

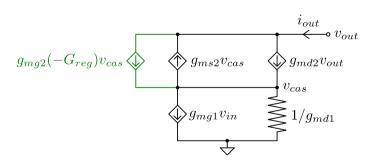

Low-frequency small-signal analysis:

$$\begin{cases} i_{out} = g_{md2}v_{out} - g_{ms2}v_{cas} \\ g_{md1}v_{cas} = i_{out} - g_{mg1}v_{in} \end{cases}$$

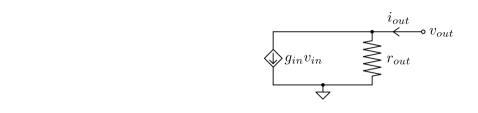

► CMOS OpAmp **model**:

Low-frequency **small-signal** analysis:

► CMOS OpAmp **model**:

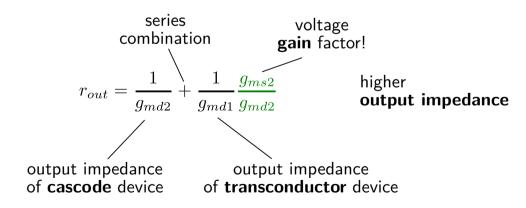

$$g_{in} \doteq \frac{i_{out}}{v_{in}} = g_{mg1} \frac{g_{ms2}}{g_{ms2} + g_{md1}}$$

$r_{out} \doteq \frac{v_{out}}{i_{out}} = \frac{1}{g_{md2}} + \frac{1}{g_{md1}} \frac{g_{ms2}}{g_{md2}}$

## Basic Cascode OpAmp

Low-frequency small-signal analysis:

► CMOS OpAmp **model**:

$$g_{in} = g_{mg1} rac{g_{ms2}}{g_{ms2} + g_{md1}} \simeq rac{g_{mg1}}{ ext{transconductance}}$$

similar transconductance

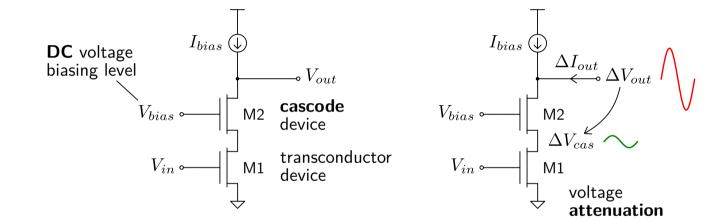

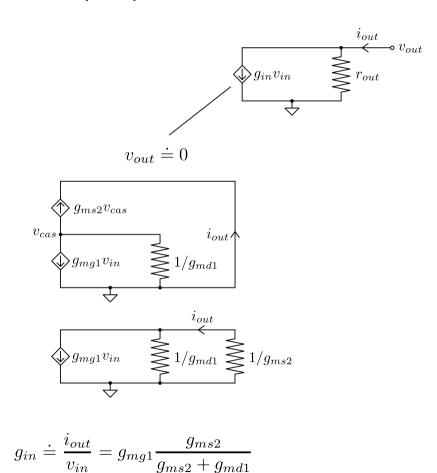

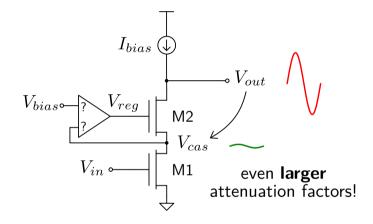

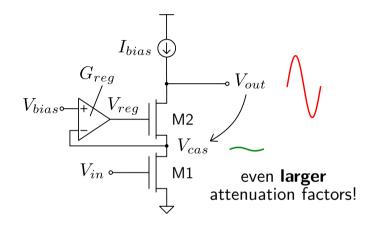

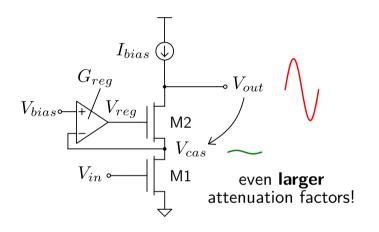

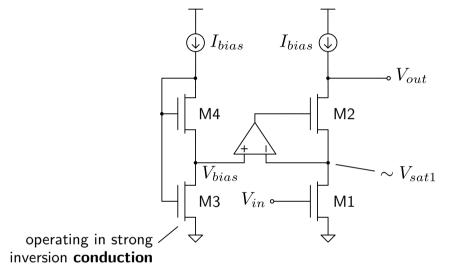

## Regulated Cascode OpAmp

Low-frequency **small-signal** analysis:

# Regulated Cascode OpAmp

Low-frequency **small-signal** analysis:

CMOS OpAmp model:

$$g_{in} = g_{mg1} \frac{g_{ms2} + g_{mg2}G_{reg}}{g_{ms2} + g_{mg2}G_{reg} + g_{md1}} \simeq g_{mg1}$$

$$r_{out} = \frac{1}{g_{md2}} + \frac{1}{g_{md1}} \frac{g_{ms2} + g_{mg2}G_{reg}}{g_{md2}} \simeq \frac{1}{g_{md1}} \frac{g_{mg2}}{g_{md2}} G_{reg}$$

# Regulated Cascode OpAmp

Low-frequency small-signal analysis:

► CMOS OpAmp **model**:

$$g_{in} = g_{mg1} \frac{g_{ms2} + g_{mg2}G_{reg}}{g_{ms2} + g_{mg2}G_{reg} + g_{md1}} \simeq g_{mg1}$$

$$r_{out} = \frac{1}{g_{md2}} + \frac{1}{g_{md1}} \frac{g_{ms2} + g_{mg2}G_{reg}}{g_{md2}} \simeq \frac{1}{g_{md1}} \frac{g_{mg2}}{g_{md2}} G_{reg}$$

► Minimalist implementation:

$$G_{reg} \equiv \frac{g_{mg3}}{g_{md3}}$$

$$I_{bias2} \longrightarrow V_{out}$$

$$M_2 \longrightarrow W_{1}$$

$$|G(DC)| \simeq \frac{g_{mg1}}{g_{md1}} \frac{g_{mg2}}{g_{md3}} \frac{g_{mg3}}{g_{md3}}$$

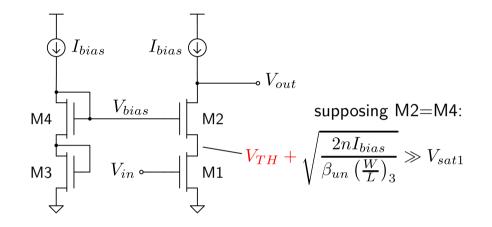

All operating in strong inversion saturation + neglecting CLM

78/110

**Basic** cascode DC biasing:

alternative low-voltage approach:

► **Regulated** cascode DC biasing:

$\begin{cases} I_{bias} = \beta_3 \left( V_{GB3,4} - V_{TH} + \frac{n}{2} V_{bias} \right) V_{bias} \\ I_{bias} = \frac{\beta_4}{2n} \left( V_{GB3,4} - V_{TH} - n V_{bias} \right)^2 \end{cases}$

$$V_{bias} \equiv V_{sat1}$$

:

$$\sqrt{\frac{2}{(W/L)_4}} = \sqrt{\frac{1}{2(W/L)_3} \frac{(W/L)_1}{(W/L)_3}} - 3\sqrt{\frac{1}{2(W/L)_1}}$$

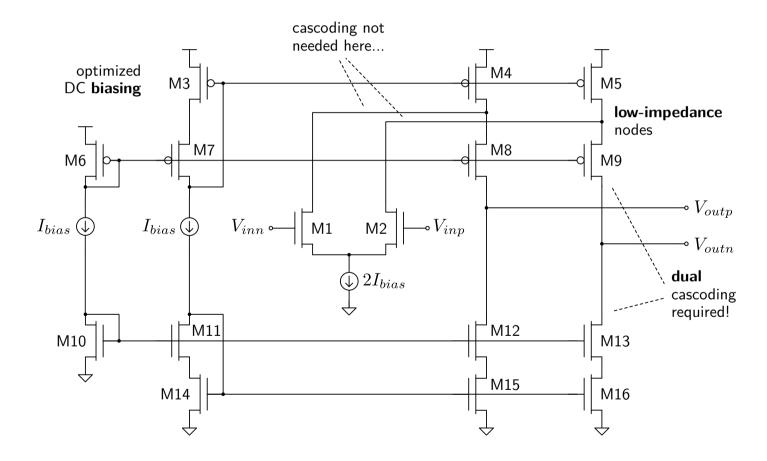

## **Practical Cascode OpAmps**

► Fully differential + folded + cascode topology example:

- 1 OpAmp Figures of Merit

- 2 The Mono-Transistor Amplifier

- 3 Differential Circuits with CMFB

- 4 Folded Amplifiers

- 5 Cascode Topologies

- 6 Gain Enhancement Techniques

- 7 Multi-Stage OpAmps

## **Principle Basis**

► CMOS OpAmp general **linear model**:

► Enhancement by increasing MOSFET input transconductance?

# **Principle Basis**

► CMOS OpAmp general **linear model**:

► Enhancement by increasing MOSFET input transconductance?

$$BW = \frac{1}{2\pi r_{out} c_{load}} \qquad GBW = \frac{g_{in}}{2\pi c_{load}}$$

- ▲ **Gain** improvement:

- Accurate **feedback** functions

- Lower equivalent input **noise**

- ▲ **Speed** enhancement (GBW)

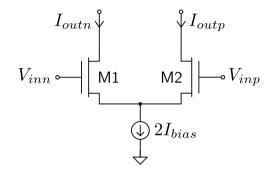

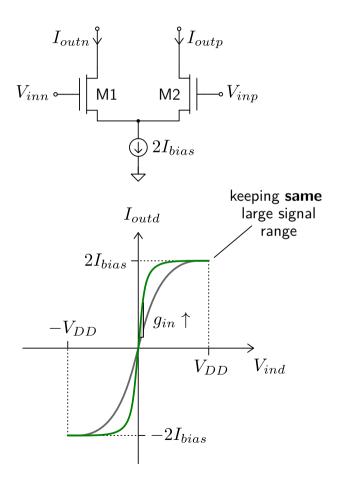

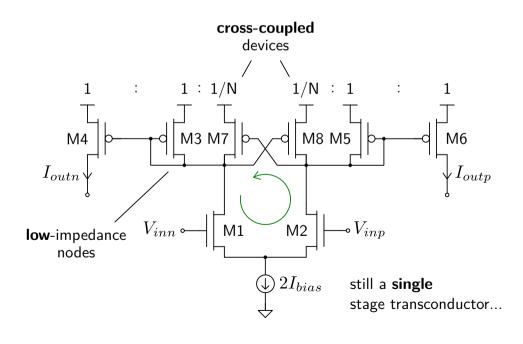

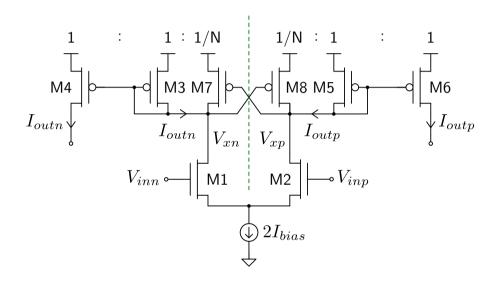

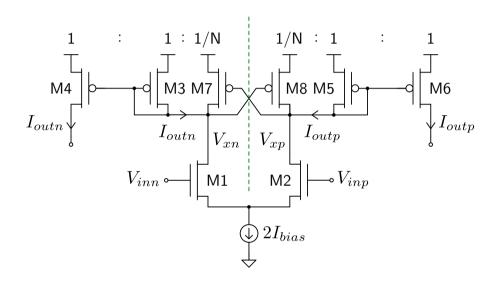

**▶ Basic** differential transconductor:

**▶ Basic** differential transconductor:

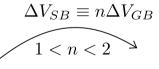

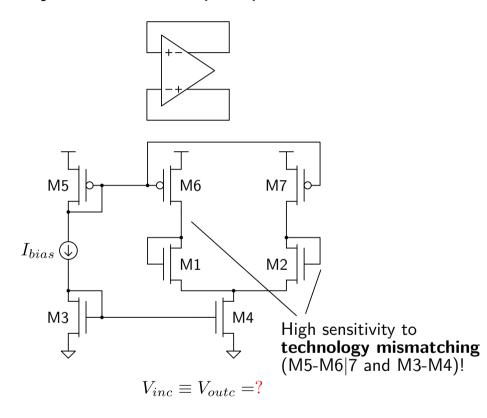

- ► Introducing **local positive** feedback:

- Folded structure

- Cross-coupled pair

- Partial feedback design by sizing ratio

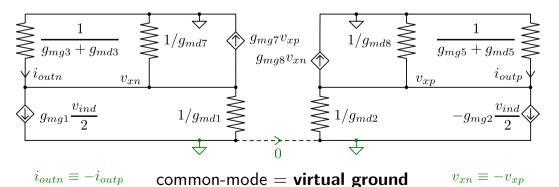

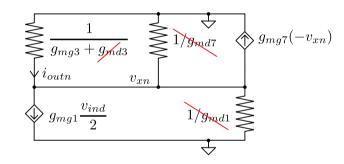

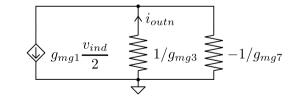

► Small signal **transconductance**:

► Small signal **transconductance**:

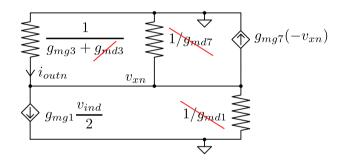

#### ► **Half-circuit** analysis:

- Perfect symmetry (no mismatching)

- Infinite tail sink resistance

- Purely differential input

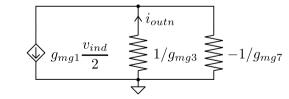

$$g_{inp} \doteq \frac{i_{outd}}{v_{ind}}$$

$$i_{outd} \doteq i_{outp} - i_{outn} \equiv |2i_{outn}|$$

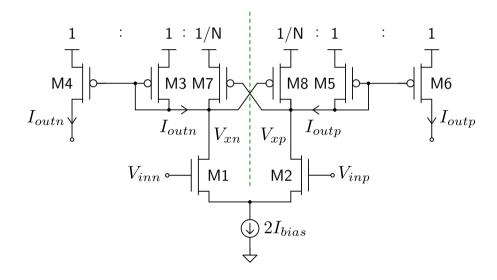

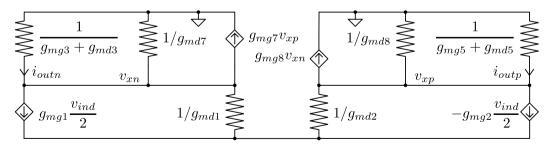

► Small signal **transconductance**:

$$i_{outn} = g_{mg1} \frac{v_{ind}}{2} \frac{g_{mg3}}{g_{mg3} - g_{mg7}}$$

$$g_{inp} = g_{mg1,2} \frac{g_{mg3,5}}{g_{mg3,5} - g_{mg7,8}} \uparrow \begin{cases} g_{mg1,2} & N \gg 1 \\ \infty & N \equiv 1 \\ 0 & N \ll 1 \end{cases}$$

#### ► Half-circuit analysis:

- Perfect symmetry (no mismatching)

- Infinite tail sink resistance

- Purely differential input

$$g_{inp} \doteq \frac{i_{outd}}{v_{ind}}$$

$$i_{outd} \doteq i_{outp} - i_{outn} \equiv |2i_{outn}|$$

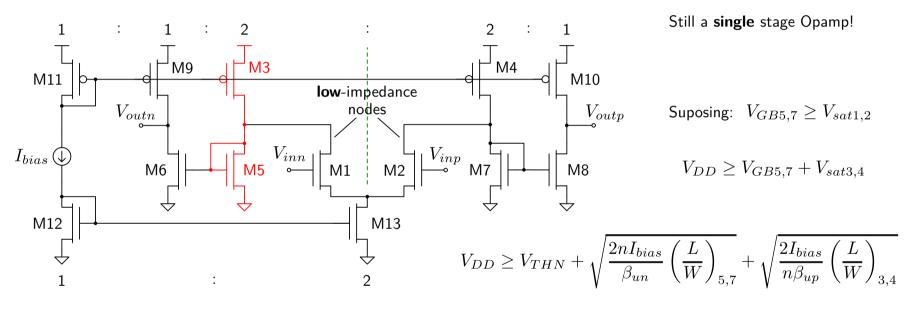

## Practical Gain Enhanced OpAmp

► Single-ended + folded + cross-coupled example:

- ▲ Larger gain and GBW

- ▲ Compatible with **folding** and **cascoding**

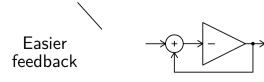

Local **positive** feedback **vs** global **negative** feedback:

- 2 The Mono-Transistor Amplifier

- 3 Differential Circuits with CMFB

- 4 Folded Amplifiers

- 5 Cascode Topologies

- 6 Gain Enhancement Techniques

- 7 Multi-Stage OpAmps

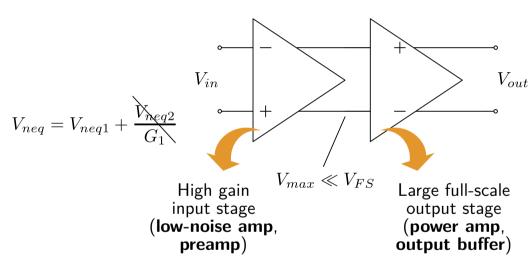

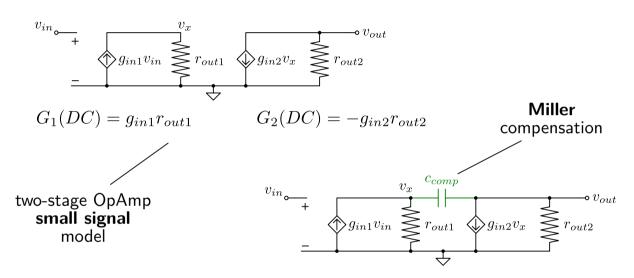

## **Splitting Functions**

**▼ Single** stage CMOS OpAmp limitations:

# **Splitting Functions**

**▼ Single** stage CMOS OpAmp limitations:

► Introducing **two-stage** architectures:

$$G = G_1 G_2$$

$$|G_1(DC)| = g_{in1} r_{out1} \qquad |G_2(DC)| = g_{in2} r_{out2}$$

- ▲ Improved **dynamic range** performance

- ▼ Area and power overheads...

- **▼ Frequency compensation** required!

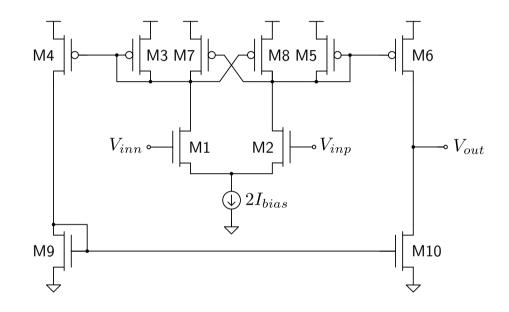

## **Practical Example**

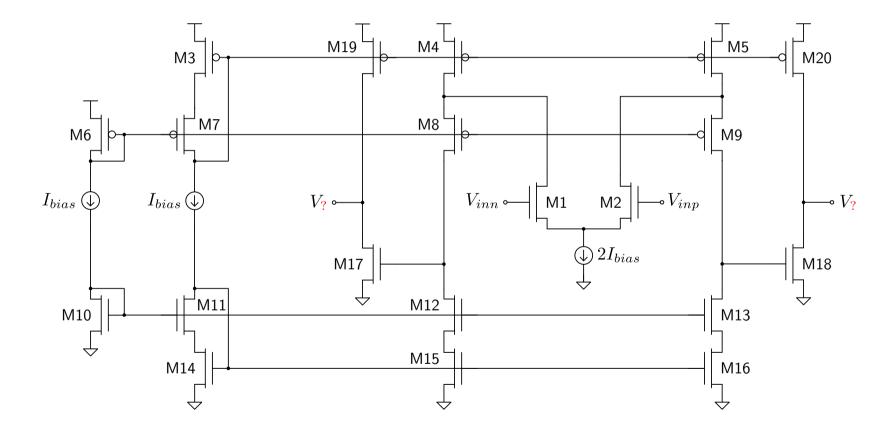

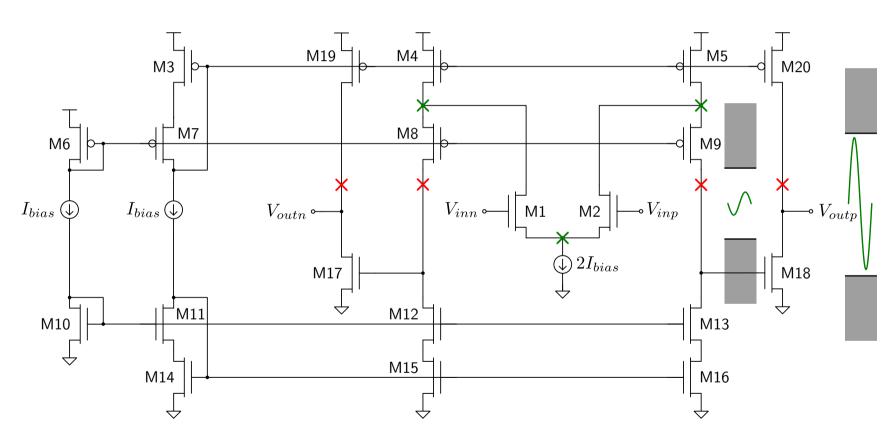

► **Two-stage** fully differential folded cascode OpAmp topology:

## **Practical Example**

► **Two-stage** fully differential folded cascode OpAmp topology:

high-impedance nodes with dynamic signals

▼ Frequency compensation strategy is needed under **feedback** (closed loop) operation...

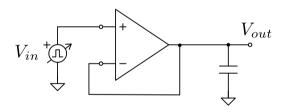

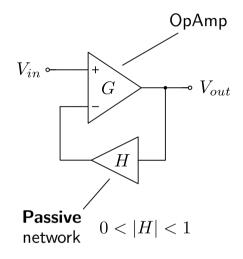

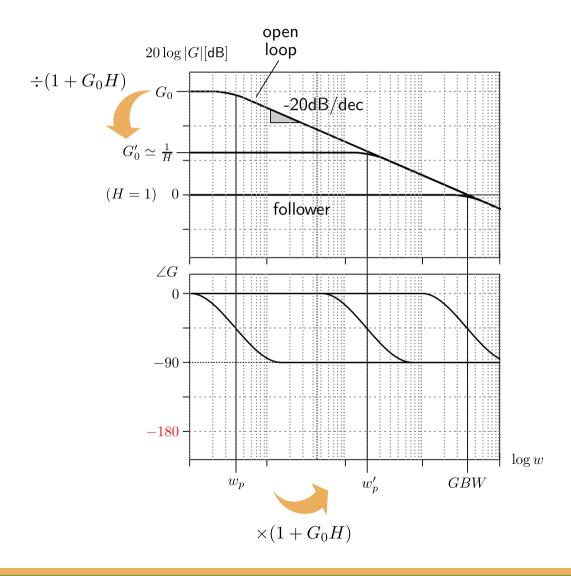

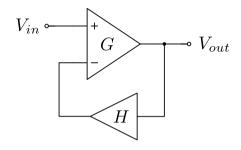

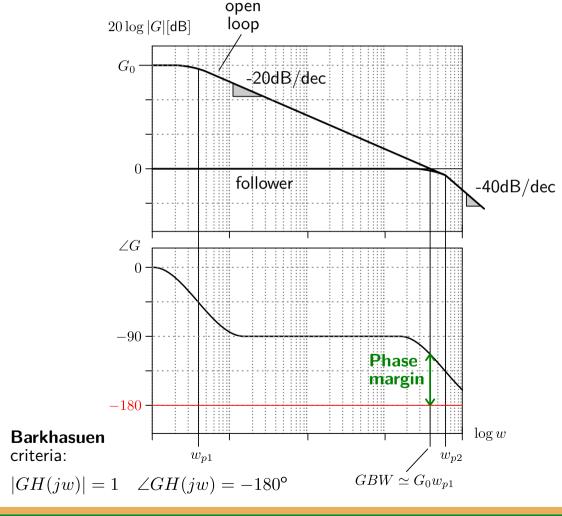

# **Single Stage OpAmp Case**

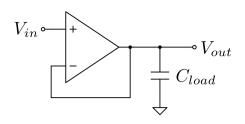

► Basic **control** theory:

$$|H| = \begin{cases} 0 & \text{open loop} \\ 1 & \text{follower} \end{cases}$$

$$\frac{V_{out}}{V_{in}} = \frac{G}{1 + GH} \simeq \frac{1}{H}$$

$$G \to \infty$$

# **Single Stage OpAmp Case**

► Basic **control** theory:

$$|H| = \begin{cases} 0 & \text{open loop} \\ 1 & \text{follower} \end{cases}$$

$$\frac{V_{out}}{V_{in}} = \frac{G}{1 + GH} \simeq \frac{1}{H}$$

$$G \to \infty$$

► Single pole amplifier:

$$G(s) = \frac{G_0}{1 + \frac{s}{w_p}}$$

$$\frac{V_{out}}{V_{in}}(s) = \frac{\frac{G_0}{1 + \frac{s}{w_p}}}{1 + \frac{G_0}{1 + \frac{s}{w_p}}H} = \frac{G_0}{1 + \frac{s}{w_p} + G_0H}$$

$$\frac{V_{out}}{V_{in}}(s) = \underbrace{\frac{G_0}{1 + G_0 H}}_{G'_0} \underbrace{\frac{1}{1 + \underbrace{\frac{s}{w_p(1 + G_0 H)}}_{w'_p}}}_{1 + \underbrace{\frac{s}{w_p(1 + G_0 H)}}_{w'_p}}$$

$$\frac{G_0'}{G_0} = \frac{1}{1 + G_0 H} \qquad \frac{w_p'}{w_p} = 1 + G_0 H$$

## **Single Stage OpAmp Case**

#### ► **Single pole** amplifier:

$$\frac{V_{out}}{V_{in}}(s) = \underbrace{\frac{G_0}{1 + G_0 H}}_{G'_0} \underbrace{\frac{1}{1 + \underbrace{\frac{s}{w_p(1 + G_0 H)}}_{w'_p}}}_{G'_0}$$

$$\frac{G'_0}{H} = \underbrace{\frac{1}{1 + G_0 H}}_{G'_0} \underbrace{\frac{w'_p}{w_p}}_{F} = 1 + G_0 H$$

#### Barkhasuen criteria:

$$|GH(jw)| = 1$$

$\angle GH(jw) = -180^{\circ}$

▲ Intrinsically **stable**!

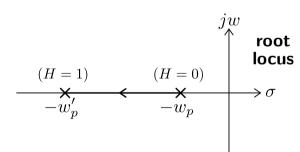

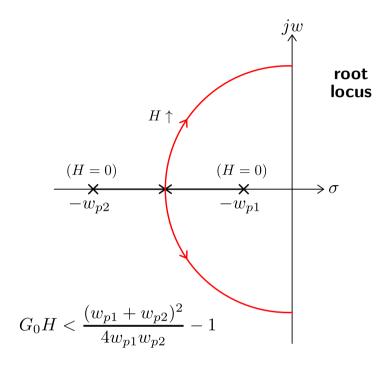

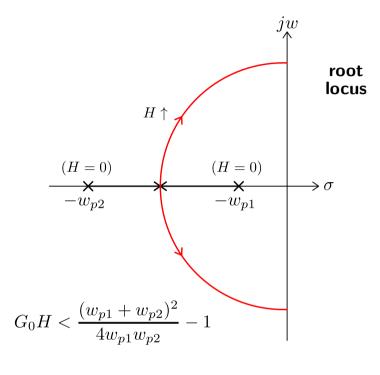

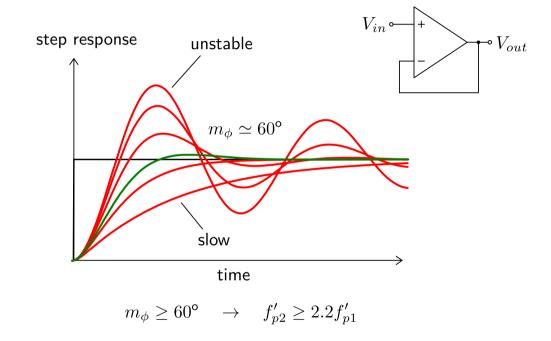

## **Two-Stage OpAmp Case**

**Double pole** analysis:

$$G(s) = \frac{G_0}{\left(1 + \frac{s}{w_{p1}}\right)\left(1 + \frac{s}{w_{p2}}\right)}$$

$$\frac{V_{out}}{V_{in}}(s) = \frac{G_0}{\left(1 + \frac{s}{w_{p1}}\right)\left(1 + \frac{s}{w_{p2}}\right) + G_0 H}$$

$$w'_{p1,2} = -\frac{w_{p1} + w_{p2}}{2} \pm \frac{1}{2} \sqrt{(w_{p1} + w_{p2})^2 - 4(1 + G_0 H)w_{p1}w_{p2}}$$

# Two-Stage OpAmp Case

**▶ Double pole** analysis:

$$G(s) = \frac{G_0}{\left(1 + \frac{s}{w_{p1}}\right)\left(1 + \frac{s}{w_{p2}}\right)}$$

$$\frac{V_{out}}{V_{in}}(s) = \frac{G_0}{\left(1 + \frac{s}{w_{p1}}\right)\left(1 + \frac{s}{w_{p2}}\right) + G_0 H}$$

$$w'_{p1,2} = -\frac{w_{p1} + w_{p2}}{2} \pm \frac{1}{2} \sqrt{(w_{p1} + w_{p2})^2 - 4(1 + G_0 H)w_{p1}w_{p2}}$$

$$H<\frac{1}{4G_0}(\frac{w_{p1}}{w_{p2}}+\frac{w_{p2}}{w_{p1}}-2)\uparrow \quad \text{in order to cover up to } \mathbf{H=1}$$

$\begin{array}{ccc} \textbf{dominant} & & & \\ \text{pole splitting} & & \frac{w_{p2}}{G_0w_{p1}} \uparrow & \text{or} & \frac{w_{p1}}{G_0w_{p2}} \uparrow \end{array}$  is required!

## Two-Stage OpAmp Case

**Double pole** analysis:

$$H<\frac{1}{4G_0}(\frac{w_{p1}}{w_{p2}}+\frac{w_{p2}}{w_{p1}}-2)\uparrow \quad \text{in order to cover up to } \mathbf{H=1}$$

$$\begin{array}{ll} \textbf{dominant} & \\ \text{pole splitting} & \\ \text{is required!} & \\ \hline G_0w_{p1} \uparrow & \text{or} & \\ \hline G_0w_{p2} \uparrow \\ \end{array} \uparrow$$

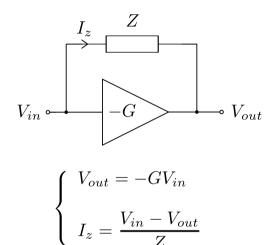

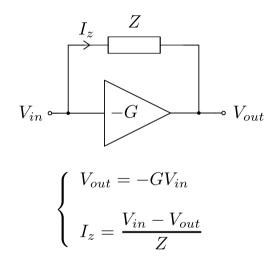

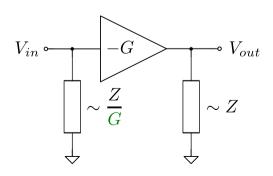

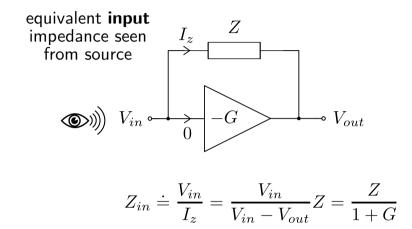

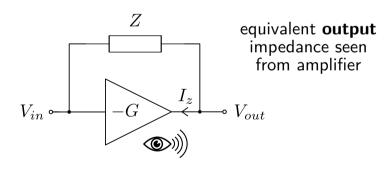

## **Principle of Operation**

► **Transimpedance** amplifier:

# **Principle of Operation**

► **Transimpedance** amplifier:

► **Miller** effect:

$$Z_{out} \doteq \frac{V_{out}}{-I_z} = \frac{V_{out}}{V_{out} - V_{in}} Z = \frac{G}{1 + G} Z$$

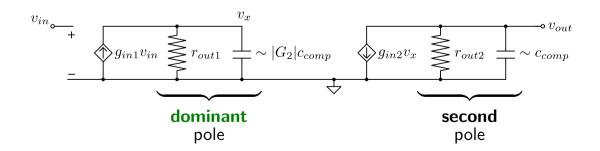

# **Pole Adjustment**

► **Transcapacitive** impedance case:

$$Z(s) \doteq \frac{1}{C_{comp}s}$$

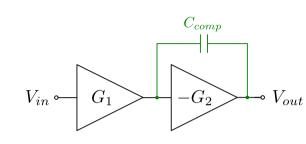

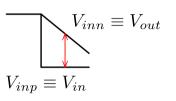

## **Practical Example**

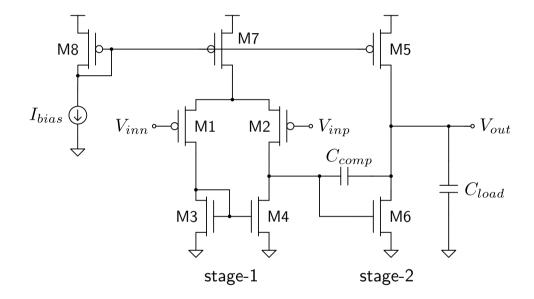

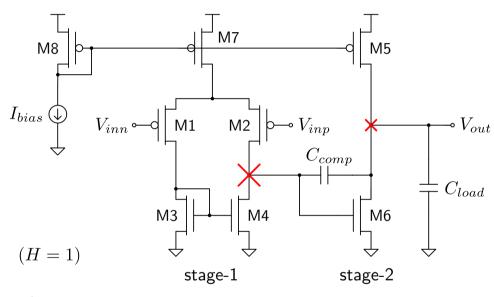

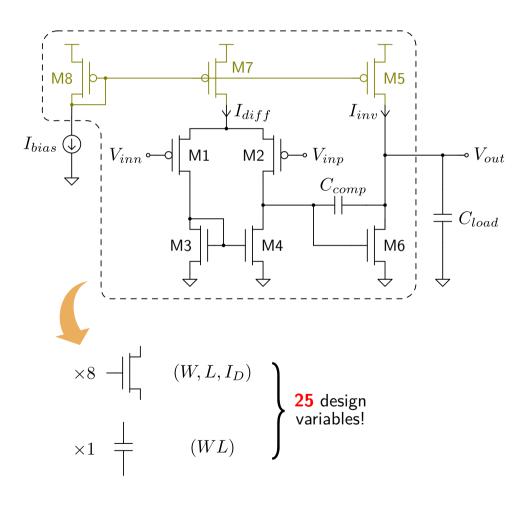

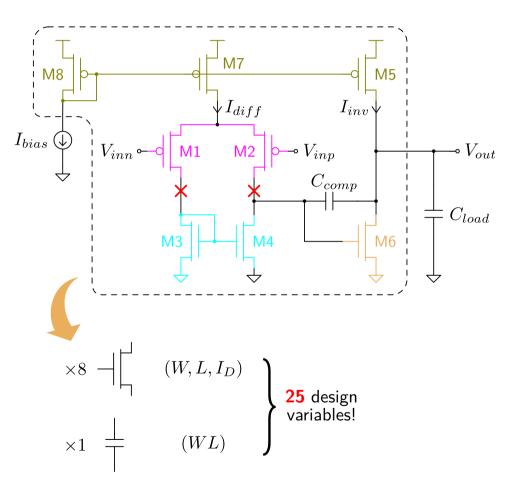

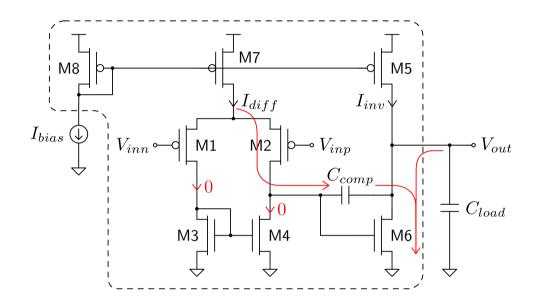

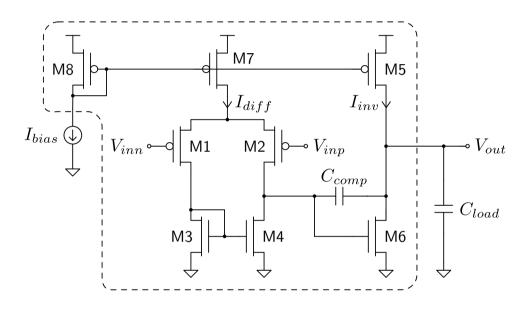

► **Two-stage** single-ended **Miller-compensated** OpAmp topology:

## **Practical Example**

► **Two-stage** single-ended **Miller-compensated** OpAmp topology:

$$f'_{p1} \simeq GBW$$

$$GBW = (g_{in1}r_{out1})(g_{in2}r_{out2})\frac{1}{2\pi}\frac{1}{r_{out1}c_{comp}(g_{in2}r_{out2})}$$

$$GBW = \frac{g_{mg1,2}}{2\pi c_{comp}}$$

Miller

$$f'_{p2} = \frac{g_{mg6}}{2\pi(c_{load} + c_{comp})}$$

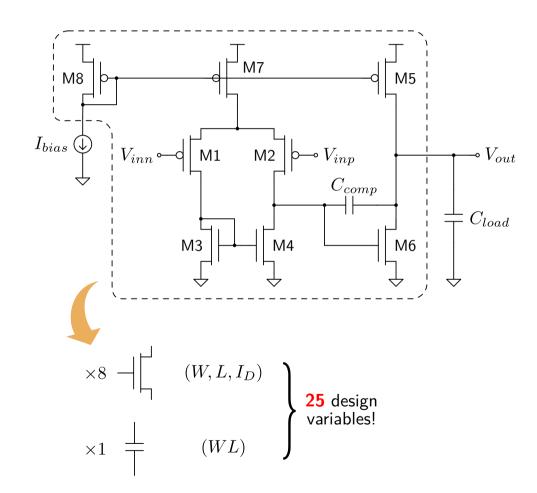

# **Design Variables**

► Single-ended **Miller** OpAmp example:

# **Design Variables**

► Single-ended **Miller** OpAmp example:

- ► Device **matching** groups:

- Current **biasing**

$$I_{diff} \doteq \underbrace{\frac{(W/L)_7}{(W/L)_8}}_{m_{diff}} I_{bias} \quad I_{inv} \doteq \underbrace{\frac{(W/L)_5}{(W/L)_8}}_{m_{inv}} I_{bias}$$

## **Design Variables**

► Single-ended **Miller** OpAmp example:

- ► Device **matching** groups:

- Current **biasing**

$$I_{diff} \doteq \underbrace{\frac{(W/L)_7}{(W/L)_8}}_{m_{diff}} I_{bias} \quad I_{inv} \doteq \underbrace{\frac{(W/L)_5}{(W/L)_8}}_{m_{inv}} I_{bias}$$

■ Null systematic **offset**

$$\begin{pmatrix} \frac{W}{L} \end{pmatrix}_1 \equiv \begin{pmatrix} \frac{W}{L} \end{pmatrix}_2 \doteq \begin{pmatrix} \frac{W}{L} \end{pmatrix}_{diff}$$

$$\begin{pmatrix} \frac{W}{L} \end{pmatrix}_3 \equiv \begin{pmatrix} \frac{W}{L} \end{pmatrix}_4 \doteq \begin{pmatrix} \frac{W}{L} \end{pmatrix}_{sing}$$

$$\frac{I_{diff}/2}{I_{inv}} \equiv \frac{(W/L)_3}{(W/L)_6}$$

8 design variables!

$$\begin{pmatrix} \frac{W}{L} \end{pmatrix}_{diff} \begin{pmatrix} \frac{W}{L} \end{pmatrix}_{sing} \begin{pmatrix} \frac{W}{L} \end{pmatrix}_{inv}$$

$$I_{bias} I_{diff} I_{inv} C_{comp} L$$

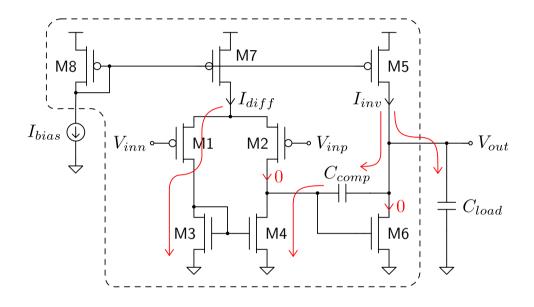

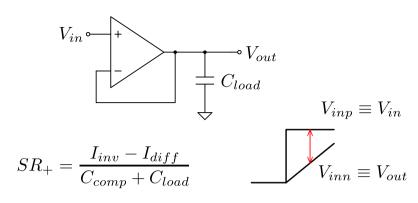

# **Design Equations**

► Single-ended **Miller** OpAmp example:

## **Design Equations**

► Single-ended **Miller** OpAmp example:

$$SR_{+} = \frac{I_{inv} - I_{diff}}{C_{comp} + C_{load}}$$

## **Design Equations**

Single-ended Miller OpAmp example:

$$GBW = \frac{g_{mg1,2}}{2\pi C_{comp}} = \frac{1}{2\pi C_{comp}} \sqrt{\frac{\beta_P}{n} \left(\frac{W}{L}\right)_{diff}} I_{diff}$$

$$G(DC) = \frac{g_{mg1,2}}{g_{md1,2} + g_{md3,4}} \frac{g_{mg6}}{g_{md5} + g_{md6}} = \frac{2}{n(\lambda_N + \lambda_P)^2} \sqrt{\frac{2\beta_P \beta_N \left(\frac{W}{L}\right)_{diff} \left(\frac{W}{L}\right)_{inv}}{I_{diff} I_{inv}}}$$

strong inversion forward saturation for all transistors

$$SR_{+} = \frac{I_{inv} - I_{diff}}{C_{comp} + C_{load}}$$

$$SR_{-} = \frac{I_{diff}}{C_{comp}}$$

$$m_{\phi} \ge 60^{\circ}: \quad \frac{g_{mg6}}{g_{mg1,2}} \ge 2.2 \left(1 + \frac{C_{load}}{C_{comp}}\right)$$

$$\sqrt{2\frac{\beta_N}{\beta_P}\frac{(W/L)_{inv}}{(W/L)_{diff}}\frac{I_{inv}}{I_{diff}}} \ge 2.2\left(1 + \frac{C_{load}}{C_{comp}}\right)$$

$$\frac{I_{diff}/2}{I_{inv}} \equiv \frac{(W/L)_{sing}}{(W/L)_{inv}}$$