# A Freeware EDA Framework for Teaching Mixed-Mode Full-Custom VLSI Design

J. Pallarès<sup>1</sup>, F. Vila<sup>1</sup>, S. Sutula<sup>1</sup>, K. Sabine<sup>2</sup>, L. Terés<sup>1,3</sup> and <u>F. Serra-Graells<sup>1,3</sup></u>

paco.serra@imb-cnm.csic.es

<sup>1</sup>Institut de Microelectrònica de Barcelona, IMB-CNM(CSIC)

<sup>2</sup>Peardrop Design Systems Ltd

<sup>3</sup>Dept. of Microelectronics and Electronic Systems Universitat Autònoma de Barcelona

Nov 2014

- **1** Introduction

- 2 Schematic Entry

- 3 Mixed-Mode HDL Simulation

- 4 Automatic Circuit Optimization

- **5** Full-Custom Layout Design and Verification

# Motivation and Objectives

**Problems** teaching VLSI design at lab:

- Professional EDA tools costs (licenses, hardware, administration)

- Technology confidentiality

- Limited lab session time

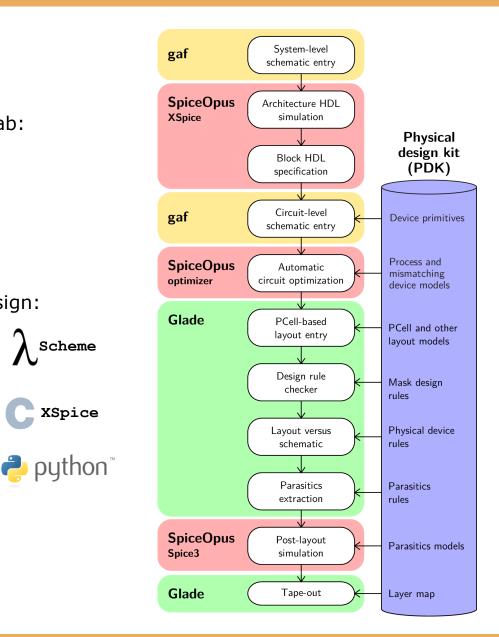

#### EDA environment proposal for mixed-mode full-custom ASIC design:

**gaf** (gschem and friends) for schematic edition and netlisting

**SpiceOpus** (SPICE with integrated optimization utilities) for analogdigital & HDL-electrical simulation

**Glade** (GDS, LEF and DEF editor) for layout design and verification

# Freeware, available for 🎥

**PDK** development

#### CUUS

Scheme

XSpice

## Case Study

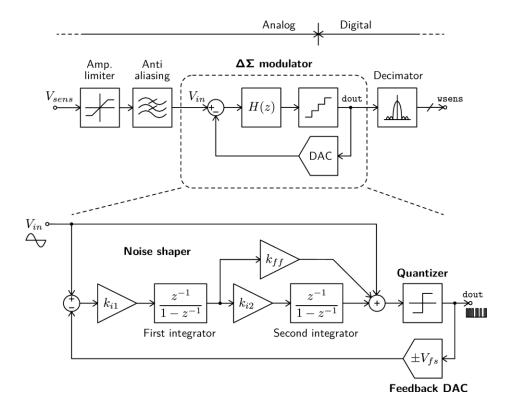

- 14bit 8kHz 2V<sub>dp</sub> A/D ΔΣM design

- Mixed analog-digital signal domains

- HDL modeling required due to oversampling

- 2P2M 2.5µm CMOS (CNM25) target technology

- Reduced DRC rule set

- Simple device modeling

- Easy PDK development

- Students easily get familiar with

...but it can be extended to modern CMOS technologies as well.

- **1** Introduction

- 2 Schematic Entry

- **3** Mixed-Mode HDL Simulation

- **4** Automatic Circuit Optimization

- **5** Full-Custom Layout Design and Verification

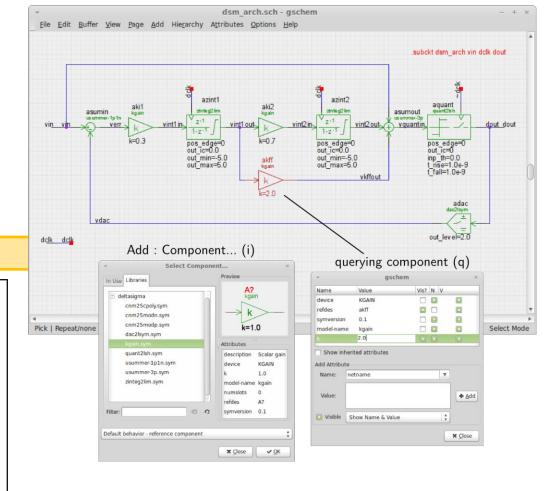

### Schematic Entry

gschem features customizable symbols, library browsing, net and pin labeling, hierarchical navigation, instance annotation and automatic rewiring...

**gnetlist** allows programmable **netlisting rules** for both native SPICE devices and custom XSpice code models

#### ເພື່ອມູ່ເບັນ

- **1** Introduction

- **2** Schematic Entry

- 3 Mixed-Mode HDL Simulation

- **4** Automatic Circuit Optimization

- **5** Full-Custom Layout Design and Verification

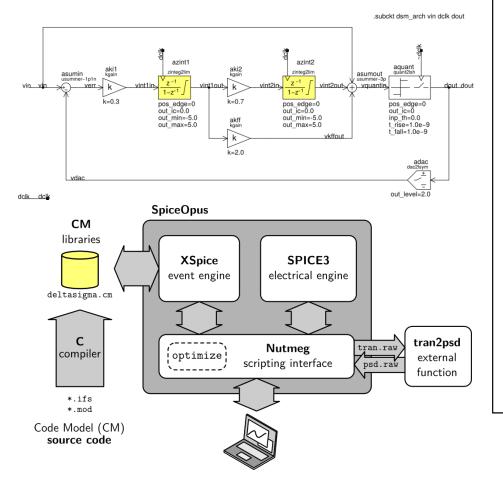

#### Architecture HDL Simulation

Students can code in C their own mixed-mode XSpice HDL models

e.g. Z-domain integrator with built-in limiter XSpice **code model (CM)**

ເພື່ອກູ

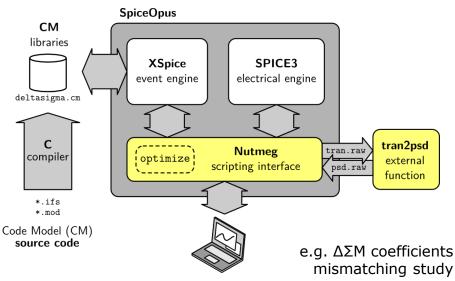

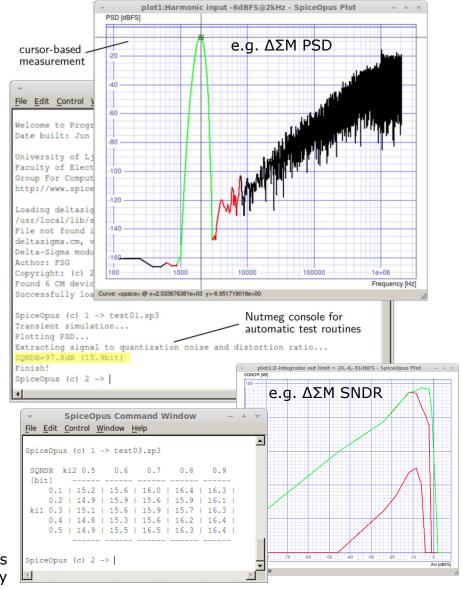

## Architecture HDL Simulation

- Students can code in C their own mixed-mode XSpice HDL models

- SPICE3 Nutmeg scripting allows to manage several circuits and analysis at the same time

- Auxiliary external programs may be also combined...

CUU

ገባና

# **Block HDL Specification**

#### XSpice modeling of circuit non-idealities and system re-simulation

|                                                                                                | zinte                    | eq2sc.ifs              |                                                    |                                |

|------------------------------------------------------------------------------------------------|--------------------------|------------------------|----------------------------------------------------|--------------------------------|

| NAME_TABLE:<br>Spice_Model_Name:<br>C_Function_Name:<br>Description:                           | zinteg2s                 | c<br>g2sc              |                                                    |                                |

| PORT_TABLE:<br>Port_Name:<br>Description:<br>Direction:<br>Default_Type:                       | in                       | "clock"<br>in          |                                                    |                                |

| PARAMETER_TABLE:<br>Parameter_Name:<br>Description:<br>Data_Type:<br>Default_Value:<br>Limits: | "DC OL ga<br>real<br>1e3 | ain" "GB<br>rea<br>1e6 | SR<br>WW" "slew-rat<br>1 real<br>5 1e6<br>-] [0 -] | - plot1:SQNI<br>PSD (dBFS/bin) |

| <br>PARAMETER_TABLE:<br>Parameter_Name:<br>Description:<br>Data_Type:<br>Default_Value:        | "lower of<br>real        | ut limit"              | out_max<br>"upper out<br>real<br>1.0               | -40                            |

|                                                                                                |                          |                        |                                                    | -100                           |

File Edit Buffer View Page Add Hierarchy Attributes Options Help subokt dsm\_so vin dolk dout. 췽 azint2 azint1 aquant quant2lsh asumout asumin zinteg2sc zinteg2sc Z-1 vint1out vquantir dout dout ven 1-z-1 pos\_edge=0 out\_ic=0 pos\_edge=0 out\_ic=0.0 out\_min=? out\_max=? kgain=0.3 G=10e3 SR=20e6 GBW=40e6 pos\_edge=0 out\_ic=0.0 out\_min=? out\_max=? kgain=0.7 inp\_th=0.0 t\_rise=1.0e-9 t\_fal⊨1.0e-9 G=10e3 SR=20e6 GBW=40e6 akff vkffout k=2.0 adac out\_level=2.0 dclk dclk SC OpAmp parameters :SONDR=94.24dB (15.36bit) for G=10000 (80dB) SR=20V/us GBW=40MHz plot1:SQNDR=57.13dB (9.2bit) for G=1000 (60dB) SR=8V/us GBW=20MHz PSD [dBFS/bin G=60dB G=80dB SR=20V/µs SR=8V/µs GBW=40MHz GBW=20MHz 100 120

1000

Curve: <space> @

10000

dsm\_sc.sch - gschem

e.g. OpAmp specification study

1e+06

Frequency [Hz]

100000

1000

10000

1e+06

Frequency [Hz]

100000

- -

- **1** Introduction

- **2** Schematic Entry

- **3** Mixed-Mode HDL Simulation

- 4 Automatic Circuit Optimization

- **5** Full-Custom Layout Design and Verification

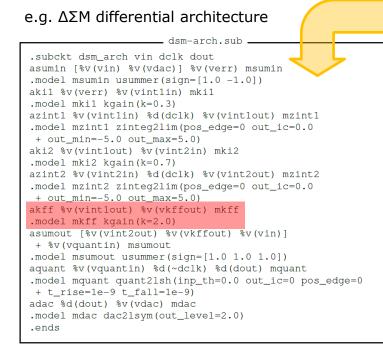

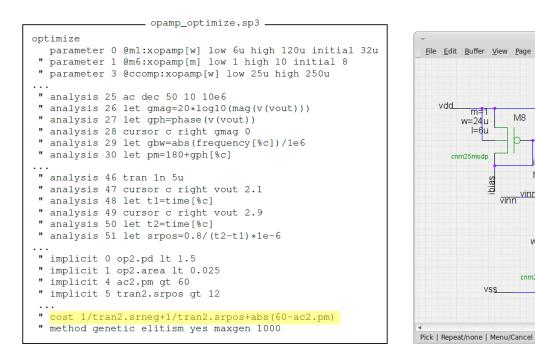

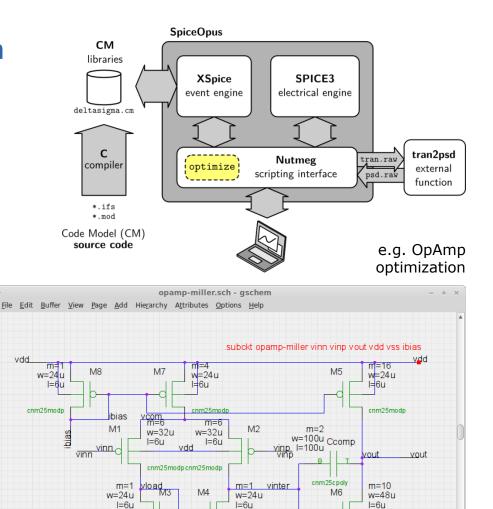

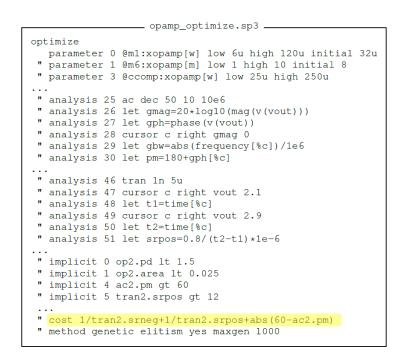

#### Automatic Circuit Optimization

- Routine scripting:

- Design parameters

- Figures-of-merit (FOMs)

- Implicit **rules** for discarding solutions

- **Cost function** to score candidates

- Optimization algorithm selection

cnm25modn

#### rns

VSS

cnm25modr

Grid(100, 100)

crm25modn

VSS

Select Mode

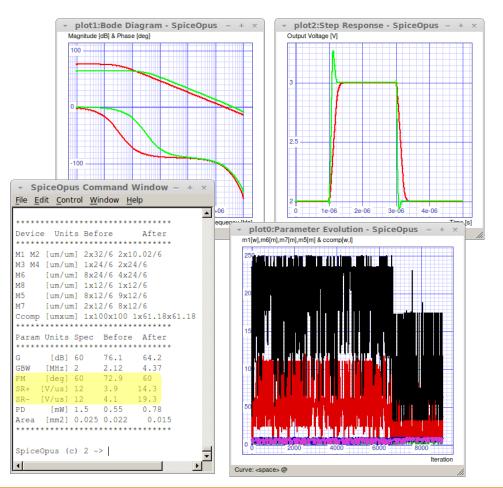

# Automatic Circuit Optimization

- Routine scripting:

- Design parameters

- Figures-of-merit (FOMs)

- Implicit rules for discarding solutions

- Cost function to score candidates

- Optimization algorithm selection

Students can customize all steps and review results:

#### ເພື່ອງເພີ

- **1** Introduction

- **2** Schematic Entry

- **3** Mixed-Mode HDL Simulation

- **4** Automatic Circuit Optimization

- **5** Full-Custom Layout Design and Verification

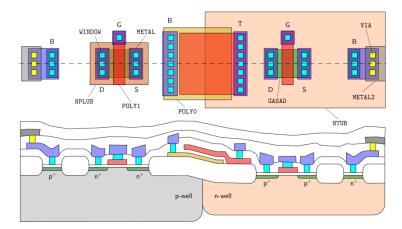

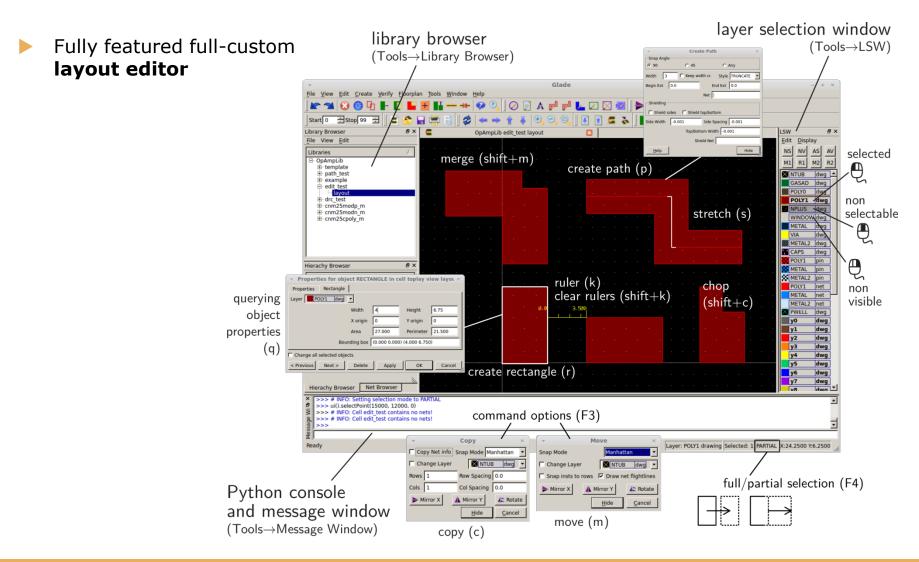

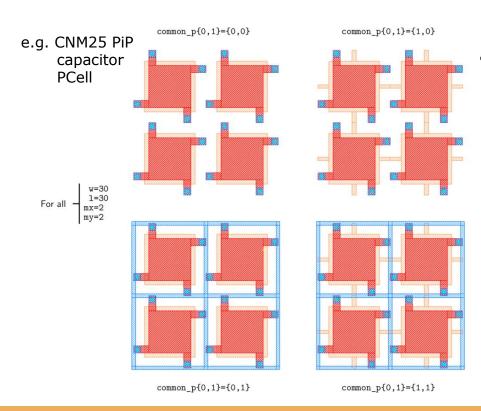

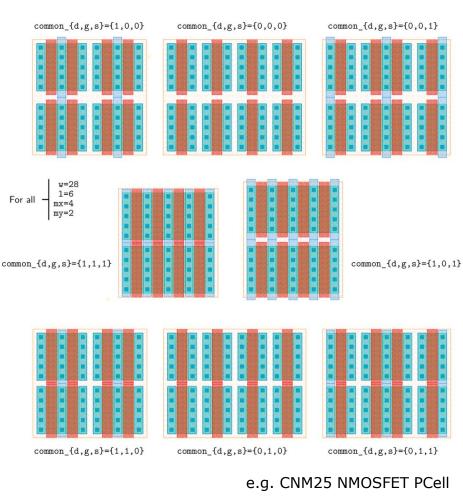

# PCell-Based Layout Design

# PCell-Based Layout Design

- Fully featured full-custom

layout editor

- Parameterized cells (PCells) developed in Python

Students can design analog layout faster while still preserving matching rules

## ເພີ່ອ

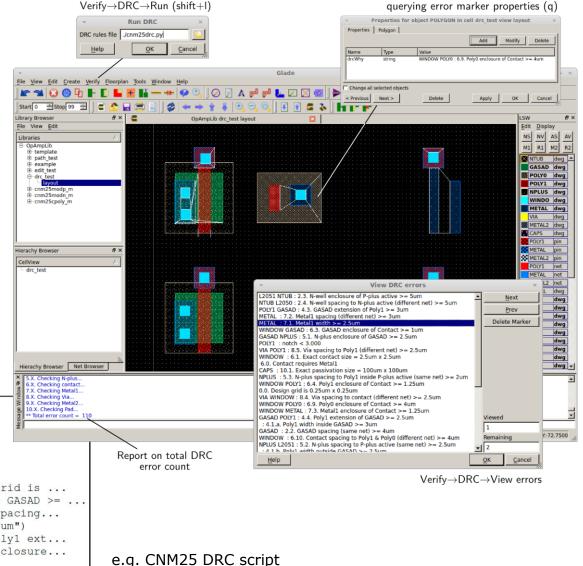

#### Design Rule Checker

- User friendly interface for debugging DRC errors

- Design rules set entirely scripted in Python

- Students can learn how a DRC is programmed (boolean operations, derived layers, geometrical concepts)

CUU (

ILUZ

derived layers boolean operations 5.X. Checking N-plu cnm25drc.py 8.X. Checking Via... active = geomGetShapes("GASAD", drawing") = geomGetShapes("POLY1", "drawing") polygate = geomGetShapes("POLY0", /"drawing") polycap = geomAnd(polygate, active) gate = geomAnd(polygate, polycap) cpoly geomOffGrid(polygate, 0.25, 1, "0.0. Design grid is ... geomWidth(gate, 3, "4.1.a. Poly1 width inside GASAD >= ... geomSpace(polygate, 3, diffnet, "4.2. Poly1 spacing... geomNotch(polygate, 3, "4.2. Poly1 notch >= 3um") geomExtension(polygate, active, 2.5, "4.4. Poly1 ext... geomEnclose (polycap, cpoly, 3, "4.6. Poly0 enclosure...

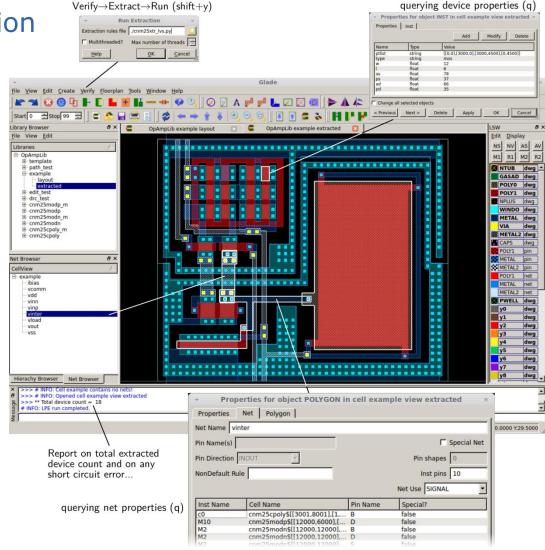

## LVS and Parasitics Extraction

- User friendly interface for debugging ERC errors

- Extraction rules set entirely scripted in Python

#### e.g. CNM25 extraction script

cnm25xtr.py ... geomLabel(polygate, "POLY1", "pin", 1) geomLabel(polygate, "POLY1", "net", 0) geomConnect([ [cont, ndiff, polff, polygate, polycap, metal1], [via12, metal1, metal2]...]) extractMOS("cnm25modn", ngate, polygate, ndiff, pwell) extractParasitic3(pdiff, metal2, cmetal2diff, 0, [metal1, polygate, polycap]) ...

#### e.g. OpAmp layout extraction

#### **CUU**® JCUS

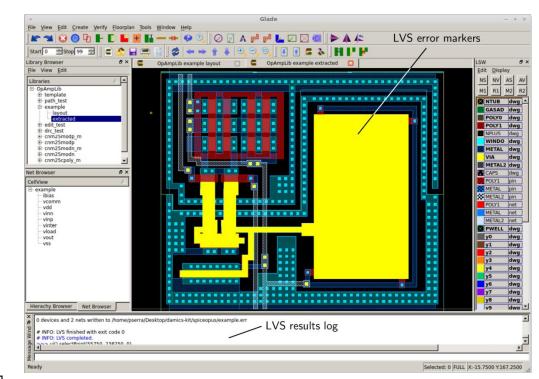

# LVS and Parasitics Extraction

e.g. OpAmp with LVS errors

- User friendly interface for debugging ERC errors

- Extraction rules set entirely scripted in Python

- Gemini-based layout

versus schematic (LVS)

- Extraction of SPICE netlists with parasitic capacitors for postlayout simulation

- e.g. OpAmp extracted netlist

.SUBCKT opamp vinn vinp vout vdd vss ibias MM0 vdd ibias vdd vdd cnm25modp w=1.2e-05 l=6e-06 as=... MM1 vdd ibias vout vdd cnm25modp w=1.2e-05 l=6e-06 as=... Cc0 vinter vout cnm25cpoly w=6.42928e-05 l=0.000156207 MM8 vout ibias vdd vdd cnm25modp w=1.2e-05 l=6e-06 as=... ... CP1 vinter vss C=3.8582e-13 CP2 vout ibias C=3.33692e-15 CP3 vinp vss C=1.85938e-15 CP4 vout vcomm C=2.0918e-15 ... .ENDS

- Students can debug circuit connectivity or device size matching errors in the same environment

- Students can evaluate losses in circuit performance due to layout parasitics

## ເກີພາວເອ

- **1** Introduction

- **2** Schematic Entry

- **3** Mixed-Mode HDL Simulation

- **4** Automatic Circuit Optimization

- **5** Full-Custom Layout Design and Verification

EDA environment for practicing mixed-mode full-custom VLSI design not only at lab but also at home

#### Students can gain hands-on experience on:

- Schematic entry

- HDL mixed system simulation

- HDL block specification

- Automatic circuit optimization

- DRC and LVS

- PCell-based layout

- Parasitics extraction

- Post-layout electrical simulation

#### A Practical A/D ΔΣM circuit design case in simple CMOS technology

102726: Design of Analog and Mixed Integrated Circuits and Systems http://www.cnm.es/~pserra/uab/damics

42838: Integrated Heterogeneous Systems Design http://www.cnm.es/~pserra/uab/ihsd

#### Thanks for your attention!

Jofre Pallarès et al. DCIS 2014