# 6. OpAmp Application Examples

#### Francesc Serra Graells

francesc.serra.graells@uab.cat Departament de Microelectrònica i Sistemes Electrònics Universitat Autònoma de Barcelona

> paco.serra@imb-cnm.csic.es Integrated Circuits and Systems IMB-CNM(CSIC)

**Pre-Amplification**

- **MRC-Amplifiers for AGC**

- Continuous-Time Gm-C Filters 3

- - Switched-Capacitor Filters

#### 1 Pre-Amplification

- 2 MRC-Amplifiers for AGC

- 3 Continuous-Time Gm-C Filters

- 4 Switched-Capacitor Filters

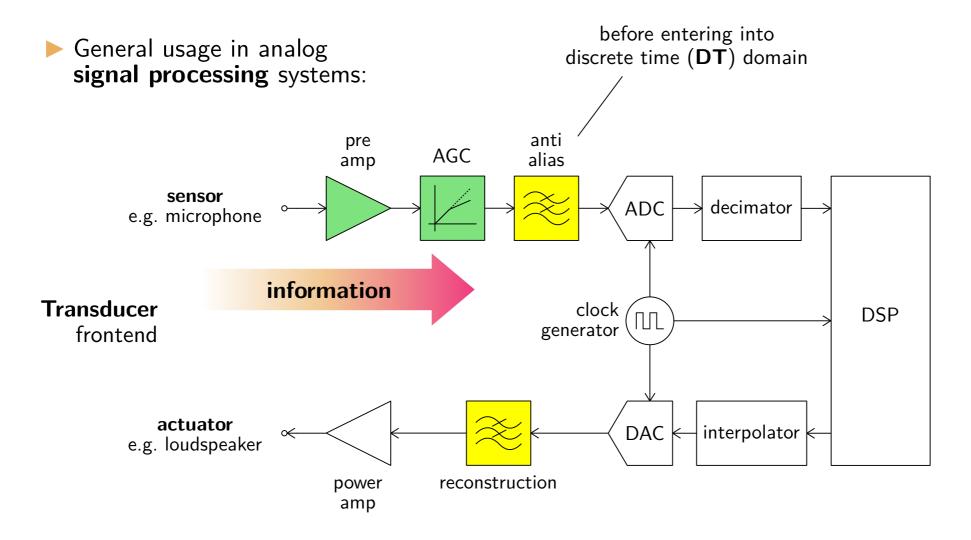

### **Pre-Amplification Stages**

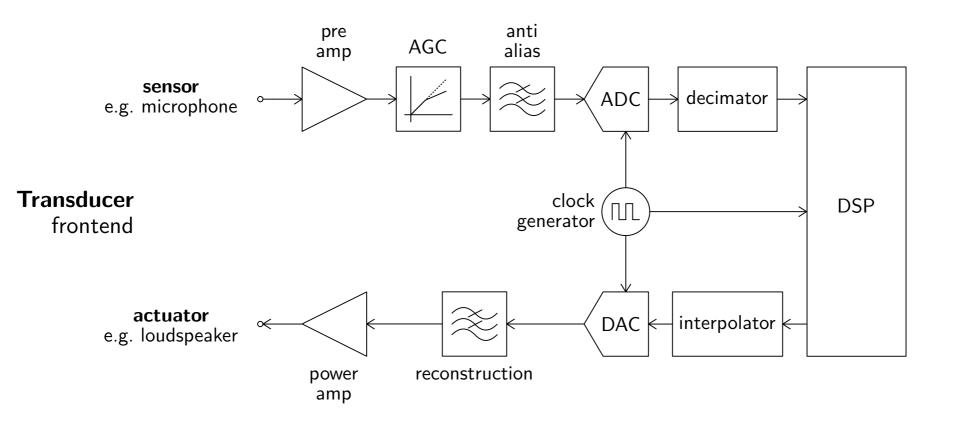

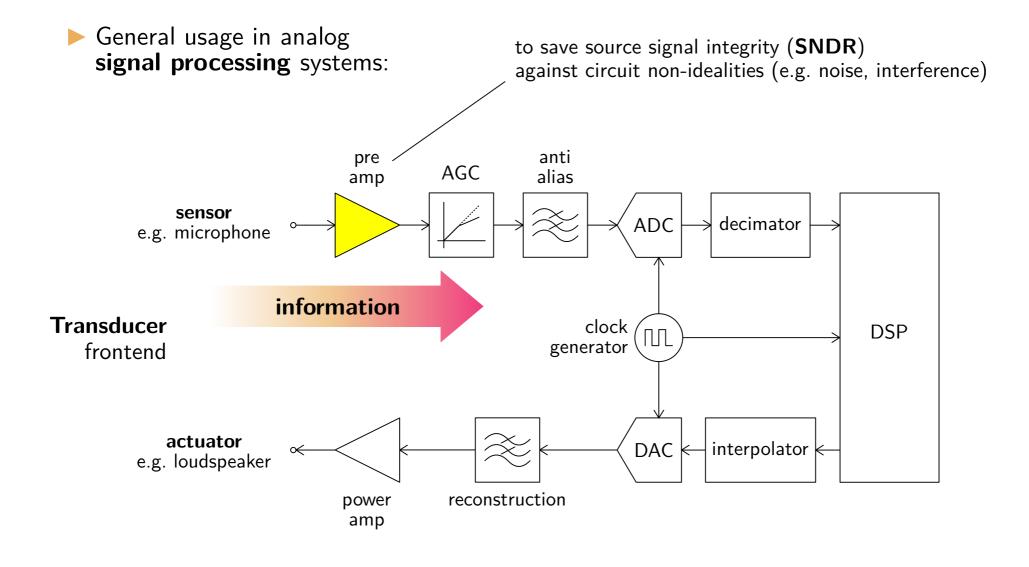

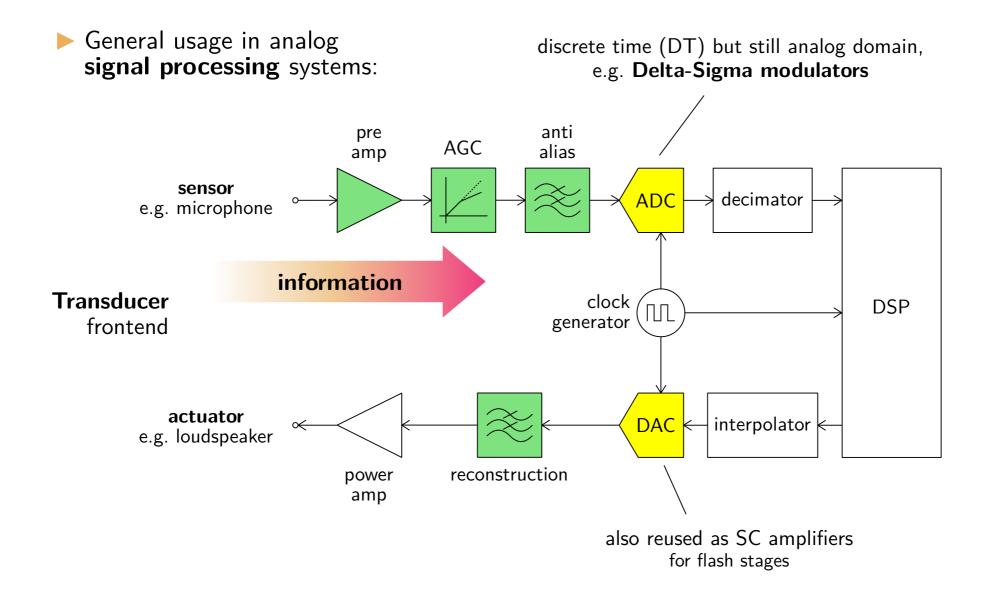

General usage in analog signal processing systems:

### **Pre-Amplification Stages**

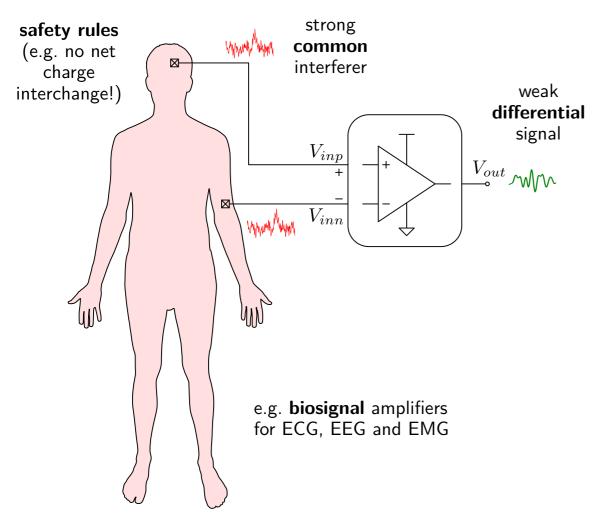

#### **Instrumentation Amplifiers**

#### OpAmp requirements for sensor read-out fronteds:

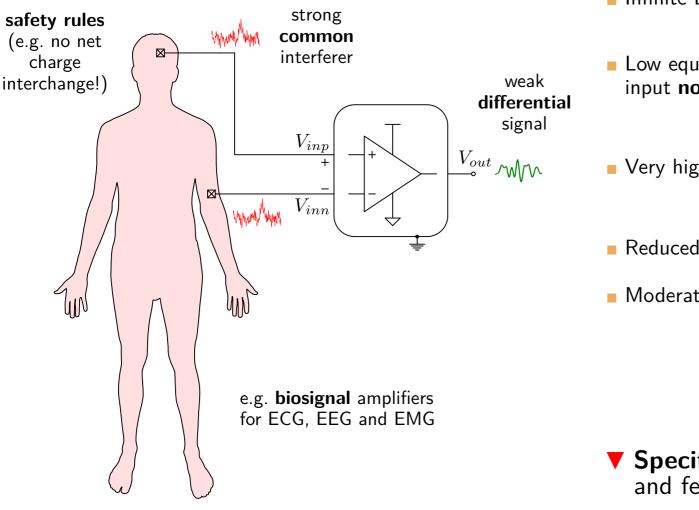

### **Instrumentation Amplifiers**

#### OpAmp requirements for sensor read-out fronteds:

- Shielding and floating supply for external interference rejection

- Infinite DC input impedance

$$\begin{array}{c} \text{Low equivalent} \\ \text{input noise} \end{array} \begin{cases} \begin{array}{c} \text{thermal } I_{bias} \uparrow \\ \\ \text{flicker} \end{array} & WL \uparrow \end{array} \\ \\ \text{Very high CMRR} \end{array} & \begin{array}{c} V_{ind} \sim \mu \mathsf{V} \\ \\ V_{inc} \sim \mathsf{V} \end{array} \end{cases} 120 \mathsf{dB!} \end{cases}$$

- Reduced bandwidth (typ. kHz-range)

- Moderate output full scale

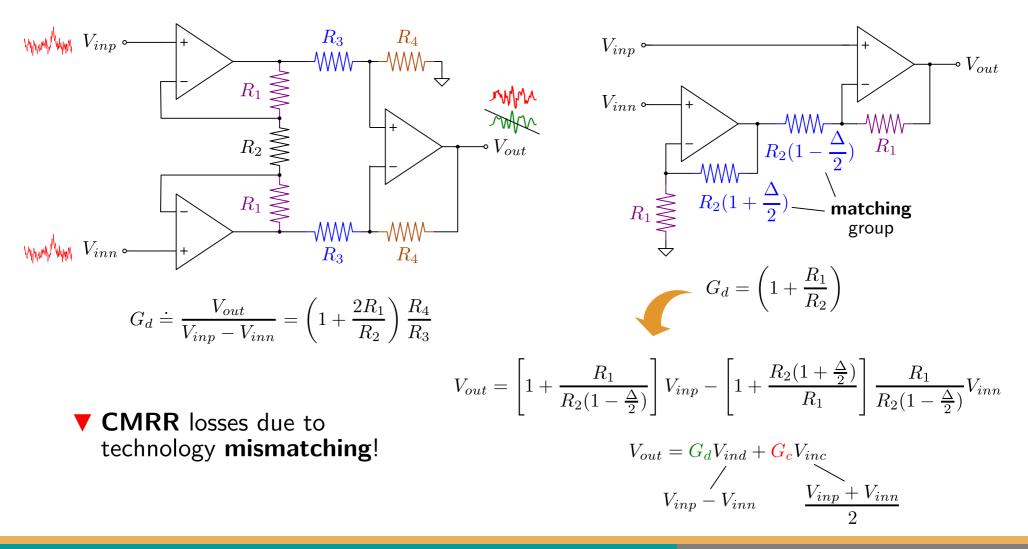

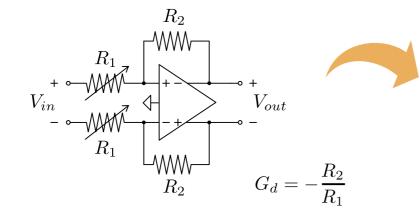

### **Classic Differential Preamplifiers**

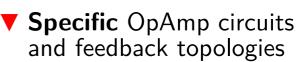

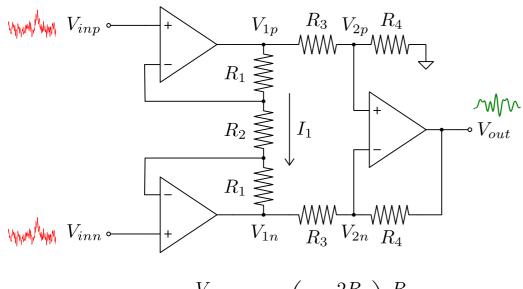

**3-OpAmp** topology:

$$G_d \doteq \frac{V_{out}}{V_{inp} - V_{inn}} = \left(1 + \frac{2R_1}{R_2}\right) \frac{R_4}{R_3}$$

first stage:

$$I_{1} = \frac{V_{inp} - V_{inn}}{R_{2}}$$

$$\begin{cases}

V_{1p} = V_{inp} + R_{1}I_{1} = \left(1 + \frac{R_{1}}{R_{2}}\right)V_{inp} - \frac{R_{1}}{R_{2}}V_{inn} \\

V_{1n} = V_{inn} - R_{1}I_{1} = \left(1 + \frac{R_{1}}{R_{2}}\right)V_{inn} - \frac{R_{1}}{R_{2}}V_{inp} \\

V_{1p} - V_{1n} \equiv \left(1 + \frac{2R_{1}}{R_{2}}\right)(V_{inp} - V_{inn})

\end{cases}$$

second stage:

$$V_{2p} \simeq V_{2n}$$

$$\frac{R_4}{R_3 + R_4} V_{1p} \simeq \frac{1}{R_3 + R_4} \left( R_4 V_{1n} + R_3 V_{out} \right)$$

$$V_{out} \simeq \frac{R_4}{R_3} \left( V_{1p} - V_{1n} \right)$$

### **Classic Differential Preamplifiers**

**3-OpAmp** topology:

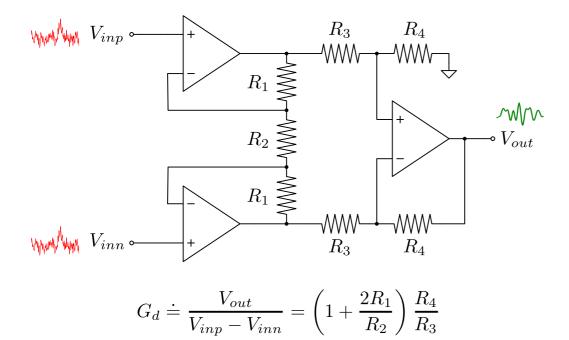

• 2-OpAmp circuit:

### **Classic Differential Preamplifiers**

**3-OpAmp** topology:

• 2-OpAmp circuit:

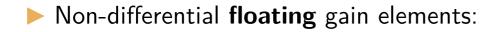

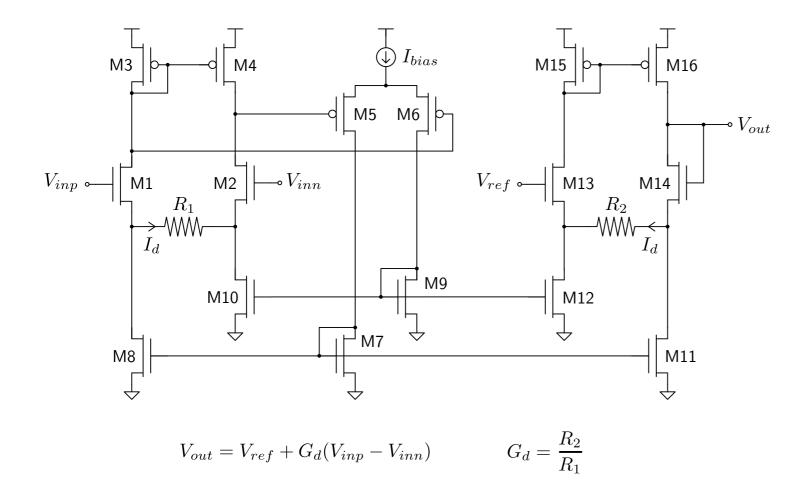

## **Specific OpAmps for Preamplifiers**

## **Specific OpAmps for Preamplifiers**

Non-differential **floating** gain elements:

- 2 MRC-Amplifiers for AGC

- 3 Continuous-Time Gm-C Filters

- 4 Switched-Capacitor Filters

## Automatic Gain Control

Also known as programmable/variable gain amplifier (**PGA**/**VGA**)

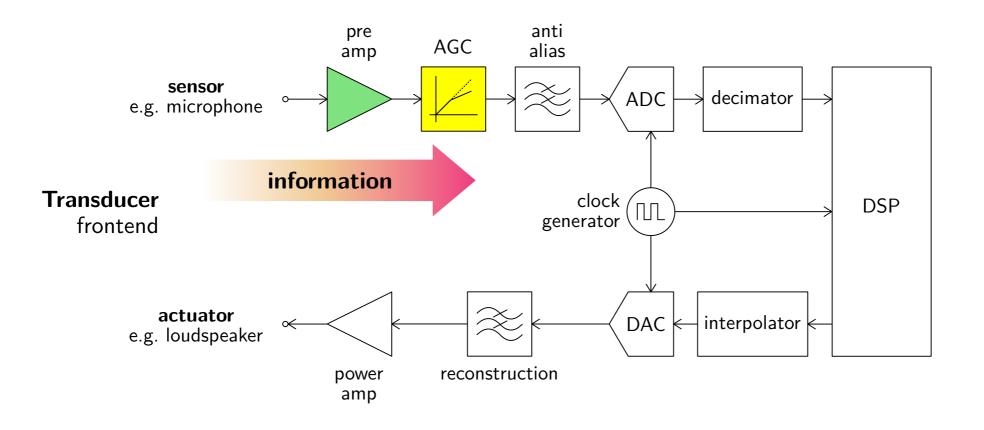

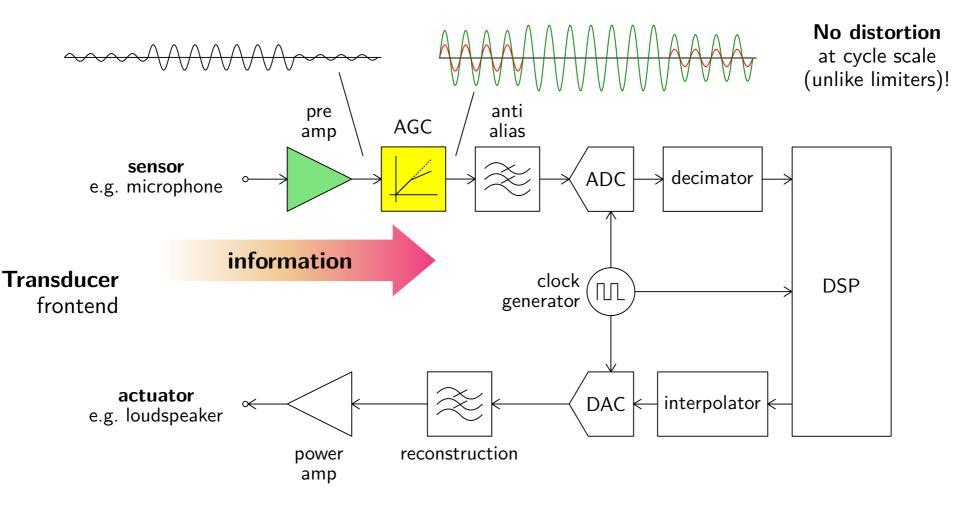

General usage in analog signal processing systems:

## Automatic Gain Control

Also known as programmable/variable gain amplifier (**PGA/VGA**)

General usage in analog signal processing systems:

Amplitude matching with **ADC full-scale**:

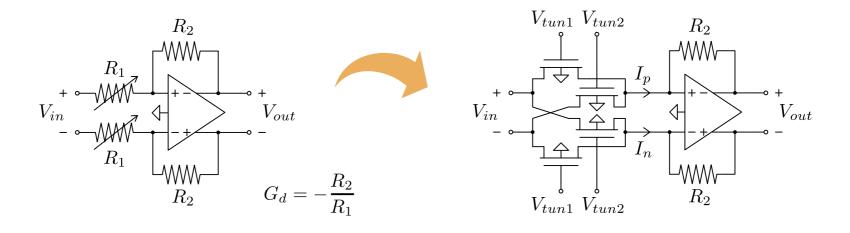

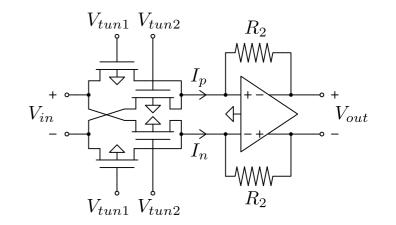

#### **Programmable Gain**

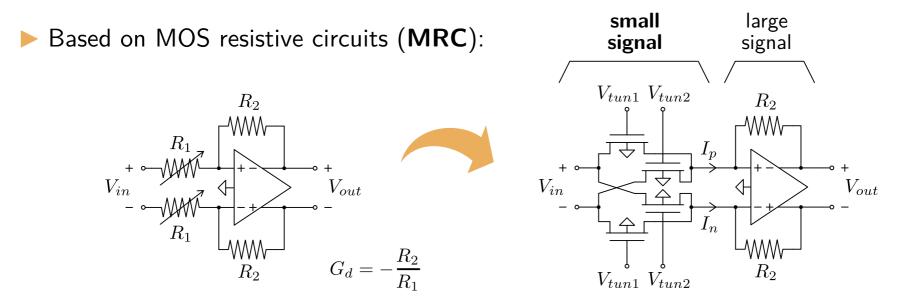

Based on MOS resistive circuits (MRC):

#### **Programmable Gain**

matched devices operating in strong inversion conduction (non-saturation):

$$I_{p} = \beta \left[ V_{tun1} - V_{TH} - \frac{n}{2} \left( \frac{V_{in}}{2} \right) \right] \left( \frac{V_{in}}{2} \right) + \beta \left[ V_{tun2} - V_{TH} - \frac{n}{2} \left( -\frac{V_{in}}{2} \right) \right] \left( -\frac{V_{in}}{2} \right)$$

$$I_{p} = \beta \left( V_{tun1} - V_{tun2} - n \frac{V_{in}}{2} \right) \frac{V_{in}}{2}$$

$$I_{a} = \beta \left( V_{tun2} - V_{tun1} - n \frac{V_{in}}{2} \right) \frac{V_{in}}{2}$$

$$I_{d} = I_{p} - I_{n} = \beta \left( V_{tun1} - V_{tun2} \right) V_{in}$$

$$R_{1} \equiv \frac{1}{2\beta \left( V_{tun1} - V_{tun2} \right)}$$

### **Programmable Gain**

Based on MOS resistive circuits (MRC):

- ▲ Compact area

- ▲ Electronically tunable gain

- ▼ Technology **sensitivity**

- ▼ MOSFET flicker **noise**

- Distortion due to larger device mismatching

$$R_1 \equiv \frac{1}{2\beta \left( V_{tun1} - V_{tun2} \right)}$$

$G_d \propto (V_{tun1} - V_{tun2})$

- 2 MRC-Amplifiers for AGC

- 3 Continuous-Time Gm-C Filters

- 4 Switched-Capacitor Filters

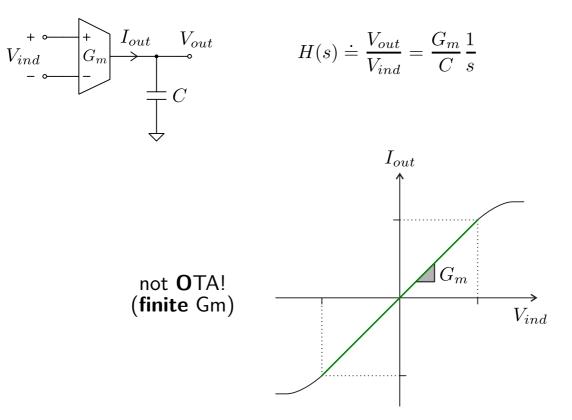

### **Continuous-Time Filters**

Also common in **high-frequency** filters...

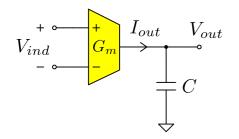

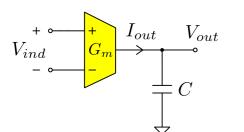

#### **Gm-C Integrator**

Based on wide-range input MOS transconductors:

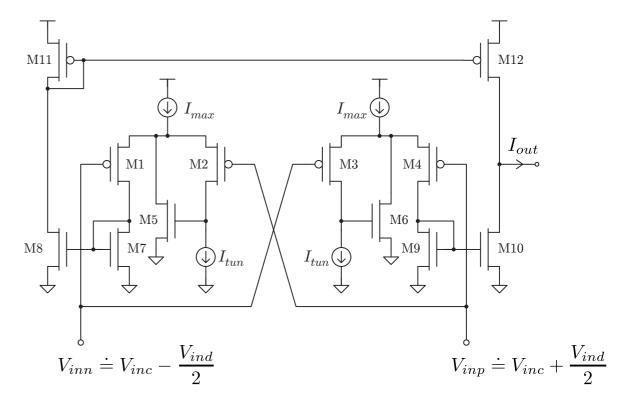

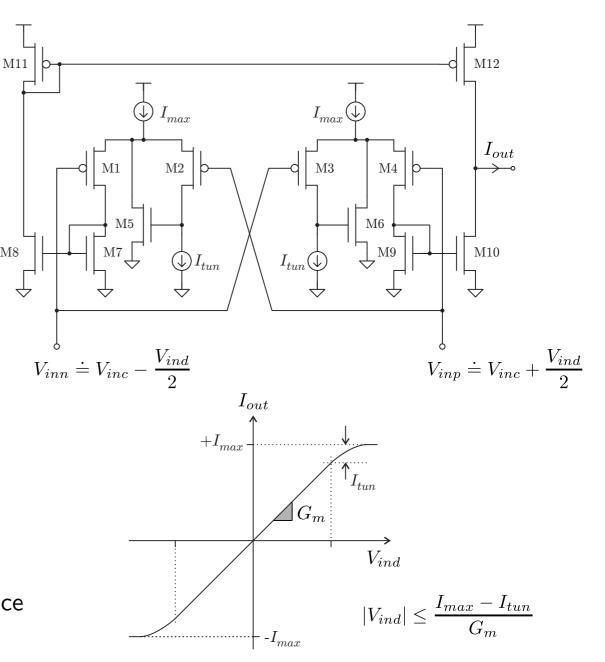

### **Gm-C Integrator**

Cross-coupled CMOS circuit realization:

matched devices operating in **strong inversion** saturation:

$$I_{D1} = \frac{\beta}{2n} \left[ \left( V_{inc} - \frac{V_{ind}}{2} \right) - V_{TH} - \left( V_{inc} + \frac{V_{ind}}{2} - V_{TH} - \sqrt{\frac{2nI_{tun}}{\beta}} \right) \right]^2$$

$$G_m \doteq \frac{I_{out}}{V_{ind}} = 2\sqrt{\frac{2\beta I_{tun}}{n}}$$

$$I_{D4} = \frac{\beta}{2n} \left[ \left( V_{inc} + \frac{V_{ind}}{2} \right) - V_{TH} - \left( V_{inc} - \frac{V_{ind}}{2} - V_{TH} - \sqrt{\frac{2nI_{tun}}{\beta}} \right) \right]^2$$

$$I_{out} = I_{D4} - I_{D1} = \frac{\beta}{2n} \left[ \left( V_{ind} + \sqrt{\frac{2nI_{tun}}{\beta}} \right)^2 - \left( -V_{ind} + \sqrt{\frac{2nI_{tun}}{\beta}} \right)^2 \right]$$

ee

M8

### **Gm-C Integrator**

**Cross-coupled** CMOS circuit realization:

$$G_m \doteq \frac{I_{out}}{V_{ind}} = 2\sqrt{\frac{2\beta I_{tun}}{n}}$$

- Linear differential transconductance

- ▲ Built-in **limiter**

- Technology dependence

### 1 Pre-Amplification

- 2 MRC-Amplifiers for AGC

- 3 Continuous-Time Gm-C Filters

- 4 Switched-Capacitor Filters

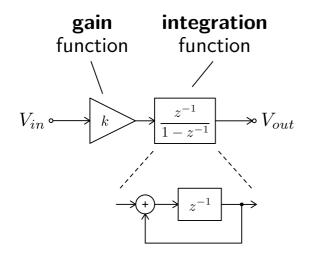

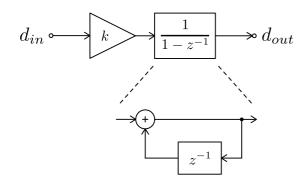

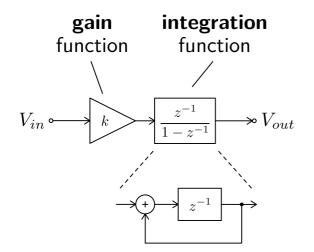

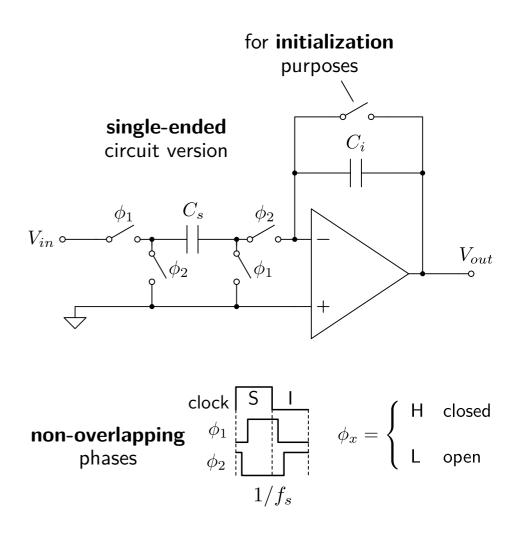

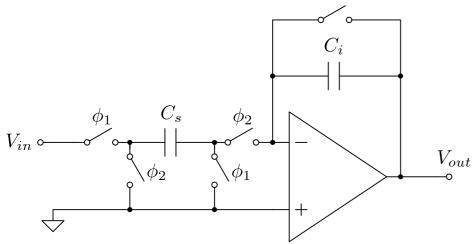

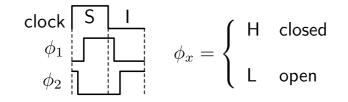

### **Switched-Capacitor Filters**

► The very basic building **block**:

Analog circuit realization (ADC)

**Digital** circuit realization (DAC)

► The very basic building **block**:

Analog circuit realization (ADC)

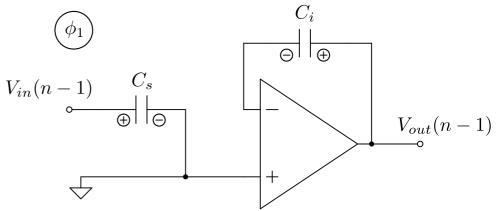

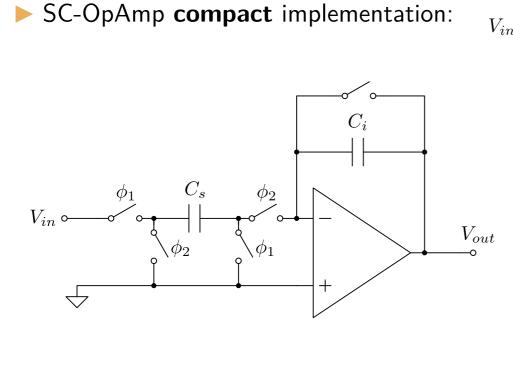

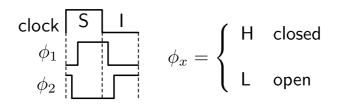

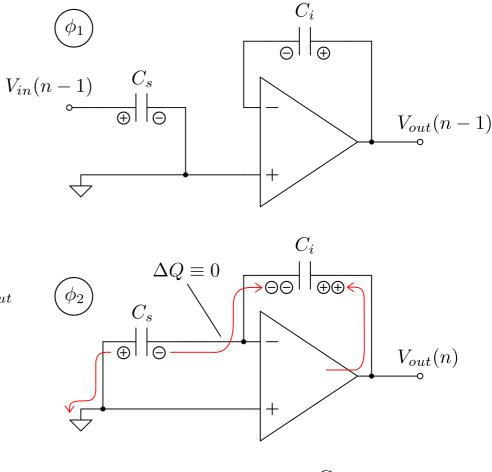

SC-OpAmp compact implementation:

$$V_{out}(n) = V_{out}(n-1) + \frac{C_s}{C_i}V_{in}(n-1)$$

$$\frac{V_{out}}{V_{in}}(z) = k \frac{z^{-1}}{1 - z^{-1}} \qquad k \doteq \frac{C_s}{C_i}$$

$C_i$

## **SC OpAmp Optimization**

$\phi_1$

### **SC OpAmp Optimization**

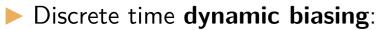

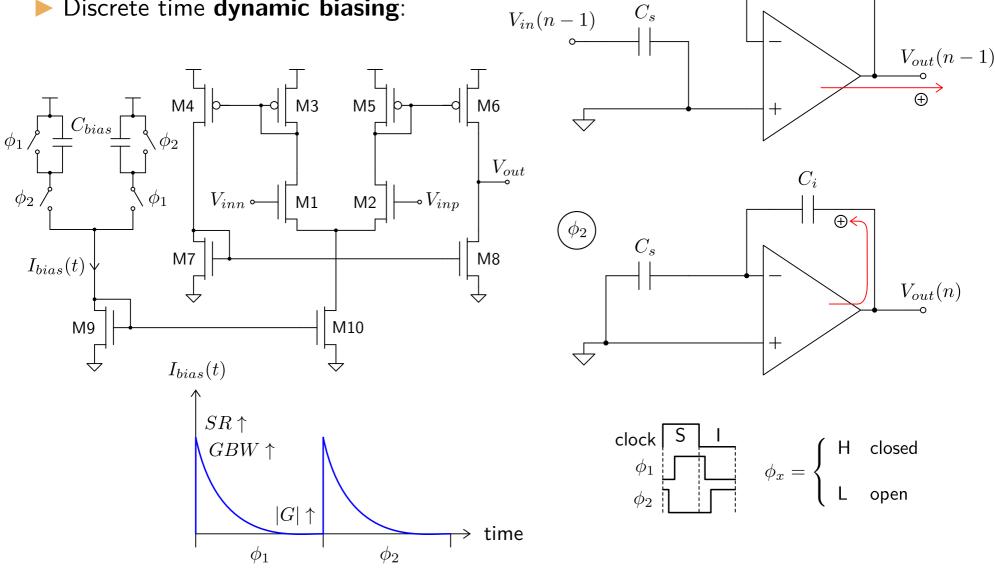

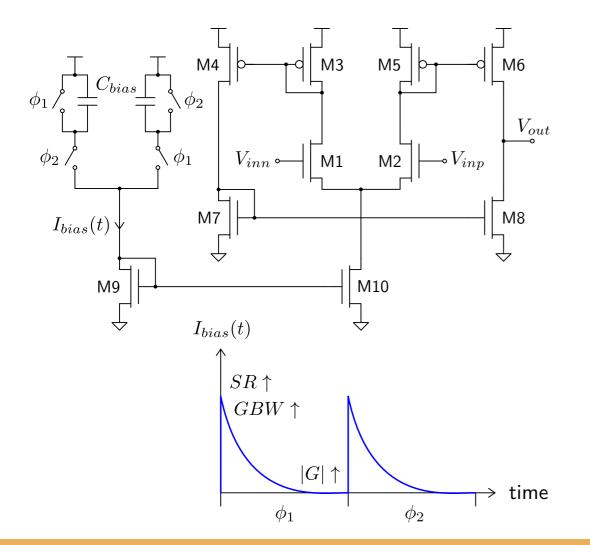

#### Discrete time dynamic biasing:

- ▲ Synchronous Class-AB operation

- ▲ Static **power** savings

- OpAmp fast on/off recovery time required

- Biasing peak value is technology dependent

- Ripple induced in the power rails (digital-like)