# 5. Low-Power OpAmps

#### Francesc Serra Graells

francesc.serra.graells@uab.cat Departament de Microelectrònica i Sistemes Electrònics Universitat Autònoma de Barcelona

> paco.serra@imb-cnm.csic.es Integrated Circuits and Systems IMB-CNM(CSIC)

- 2 Subthreshold Operation

- 3 Class-AB Output Stages

- 4 Rail-to-Rail Topologies

- 5 Inverter-Based Pseudo-Differential Multi-Stages Architectures

- 2 Subthreshold Operation

- 3 Class-AB Output Stages

- 4 Rail-to-Rail Topologies

- 5 Inverter-Based Pseudo-Differential Multi-Stages Architectures

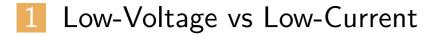

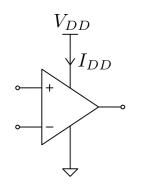

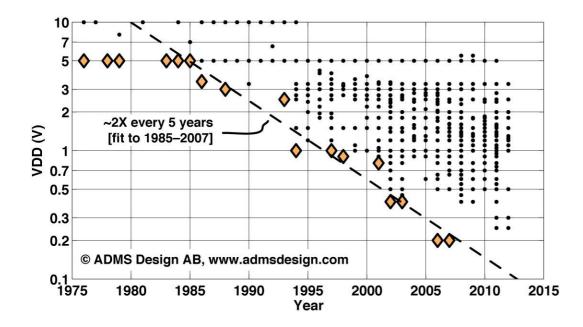

OpAmp overall **power** consumption:

$P_{DD} = I_{DD} \times V_{DD}$

OpAmp overall **power** consumption:

- Alternative supply sources (battery, solar cell, scavenging)

- **Poor** power scaling

- Limited by technology

- Low-voltage circuit techniques:

- Rail-to-rail

- Inverter-based

- Supply multipliers

- Back gate ...

OpAmp overall **power** consumption:

▲ **Strong** power savings

- Limited by noise and bandwidth

- Low-current circuit techniques:

- Subthreshold

- Class-AB

- Dynamic biasing

- Duty cycle ...

- Alternative supply sources (battery, solar cell, scavenging)

- **Poor** power scaling

- Limited by technology

- Low-voltage circuit techniques:

- Rail-to-rail

- Inverter-based

- Supply multipliers

- Back gate …

OpAmp overall **power** consumption:

▲ **Strong** power savings

- Limited by noise and bandwidth

- Low-current circuit techniques:

- Subthreshold

- Class-AB

- Dynamic biasing

- Duty cycle ...

- Alternative supply sources (battery, solar cell, scavenging)

- **Poor** power scaling

- Limited by technology

- **Low-voltage** circuit techniques:

- Rail-to-rail

- Inverter-based

- Supply multipliers

- Back gate …

- Conflicts can arise between low-current and low-voltage design techniques!

#### 2 Subthreshold Operation

3 Class-AB Output Stages

- 4 Rail-to-Rail Topologies

- 5 Inverter-Based Pseudo-Differential Multi-Stages Architectures

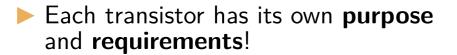

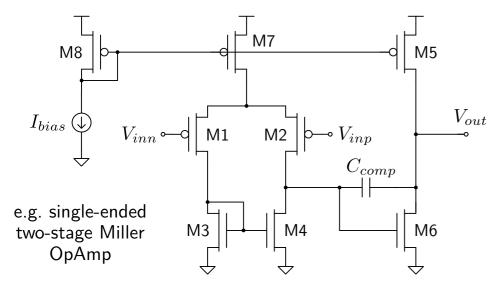

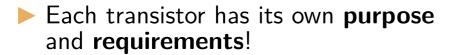

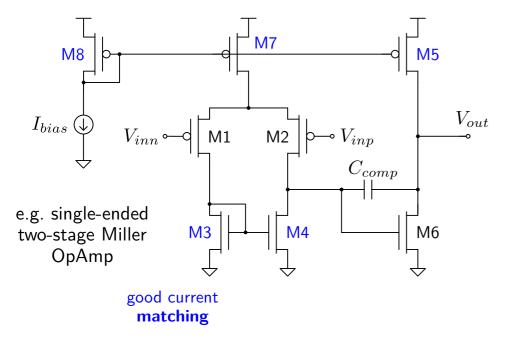

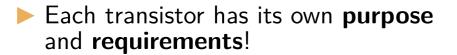

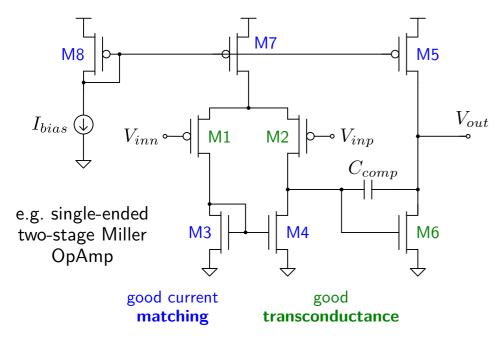

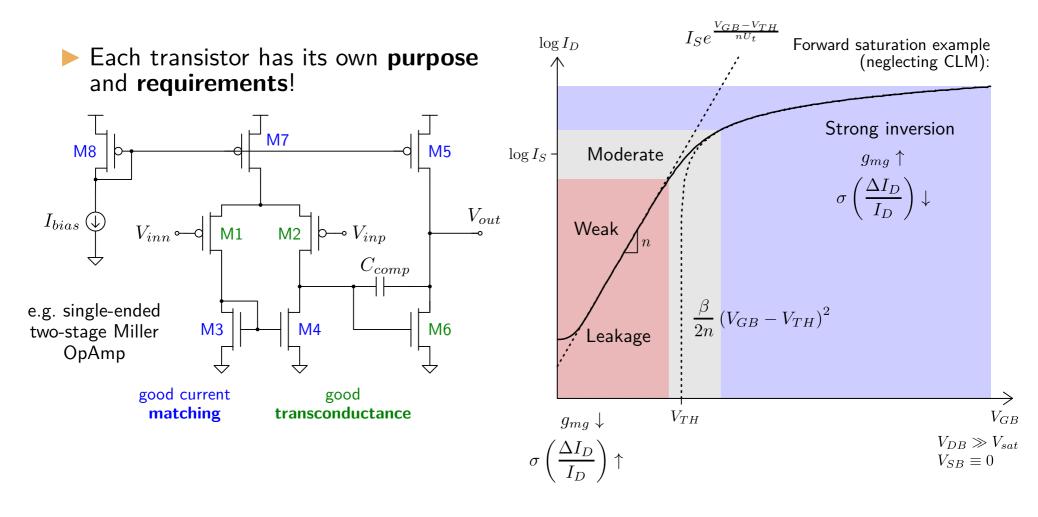

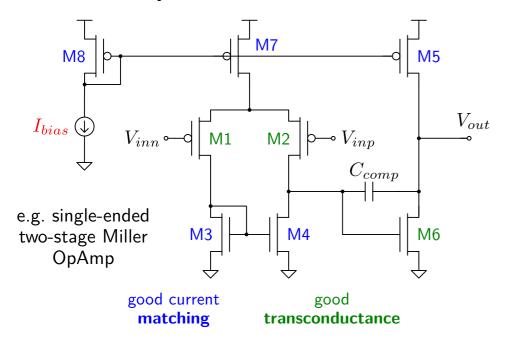

Each transistor has its own purpose and requirements!

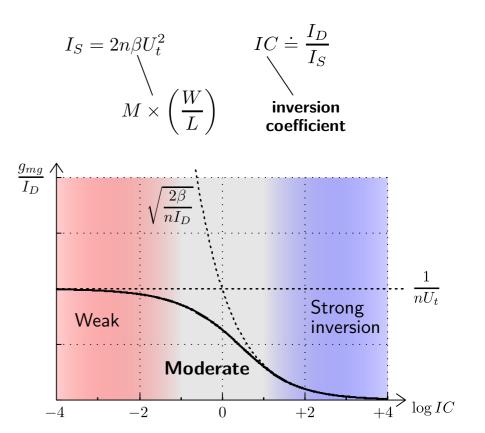

- **IC-based** circuit design:

- IC>>1 e.g. good current matching

- IC~1 optimized transconductance/power

- IC<<1 e.g. translinear e<sup>x</sup> functions

Individual operating point selection by sizing + biasing:

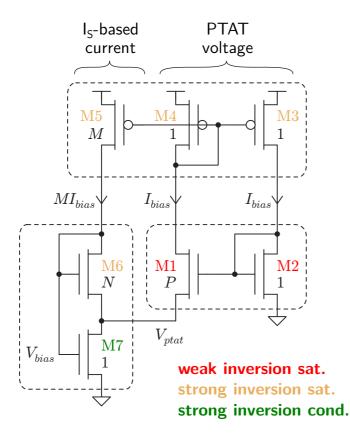

## **Specific Current Generator**

#### ► **I**<sub>s</sub>-based current reference:

$$MI_{bias} = \frac{N\beta_7}{2n} (V_{bias} - V_{TH} - nV_{ptat})^2$$

$$(M+1)I_{bias} = \beta_7 \left( V_{bias} - V_{TH} - \frac{n}{2} V_{ptat} \right) V_{ptat}$$

$$Q = \left[\frac{\ln P}{2(M+1)} \left(\sqrt{\frac{M}{N}} + \sqrt{\frac{M}{N}} + M + 1\right)\right]^2$$

$$I_{bias} \doteq QI_{S7}$$

▲ By using I<sub>bias</sub> for biasing circuits, IC selection is **independent** from technology

http://dx.doi.org/10.1109/JSSC.2002.806258

F. Serra-Graells et al., Sub-1V CMOS Proportional-To-Absolute-Temperature References, IEEE Journal of Solid-State Circuits, 38:1(84-8), Jan 2003

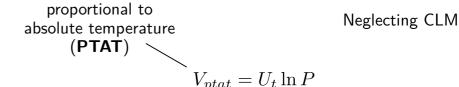

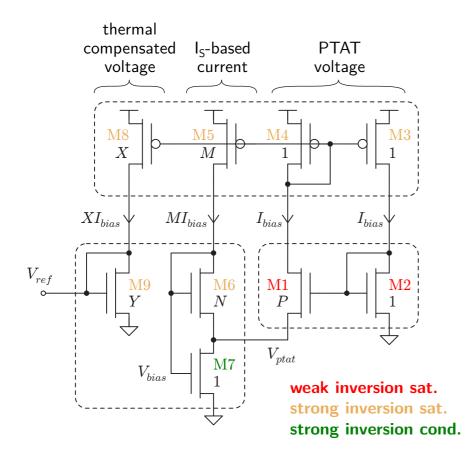

## **Specific Current Generator**

#### ► I<sub>s</sub>-based current reference:

▲ As a side effect, **temperature compensated** voltage references can be also obtained:

$$V_{ref} = 2n\sqrt{\frac{QX}{Y}}U_t + V_{TH}$$

$$V_{TH}(T) = V_{TH}(T_O) - \alpha \left(\frac{T}{T_O} - 1\right)$$

$$\sqrt{\frac{QX}{Y}} = \frac{1}{2n} \frac{\alpha}{U_t(T_O)}$$

$$V_{ref} \equiv \alpha + V_{TH}(T_O)$$

▲ By using I<sub>bias</sub> for biasing circuits, IC selection is **independent** from technology

http://dx.doi.org/10.1109/JSSC.2002.806258

F. Serra-Graells et al., Sub-1V CMOS Proportional-To-Absolute-Temperature References, IEEE Journal of Solid-State Circuits, 38:1(84-8), Jan 2003

- 2 Subthreshold Operation

- 3 Class-AB Output Stages

- 4 Rail-to-Rail Topologies

- 5 Inverter-Based Pseudo-Differential Multi-Stages Architectures

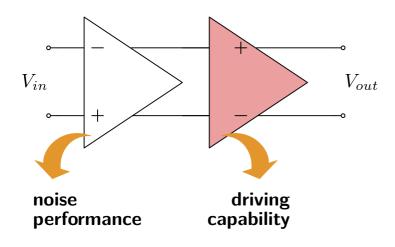

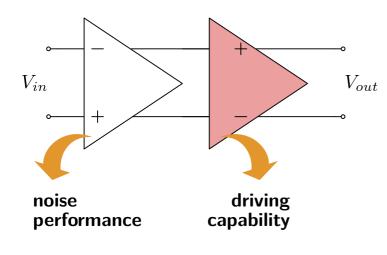

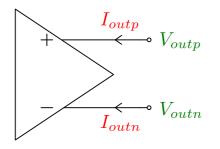

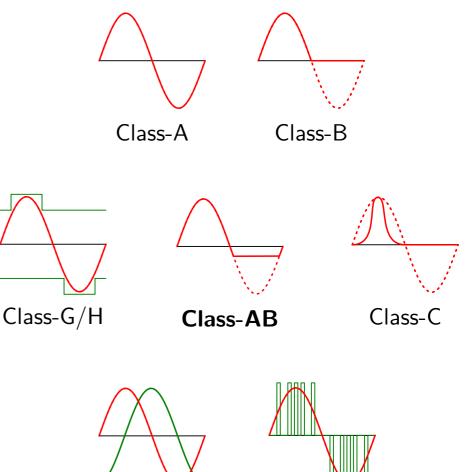

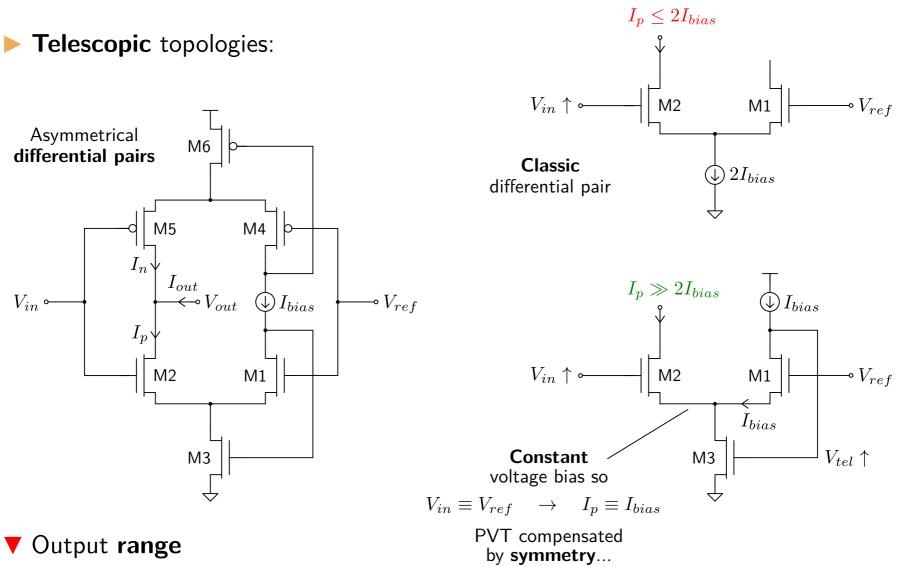

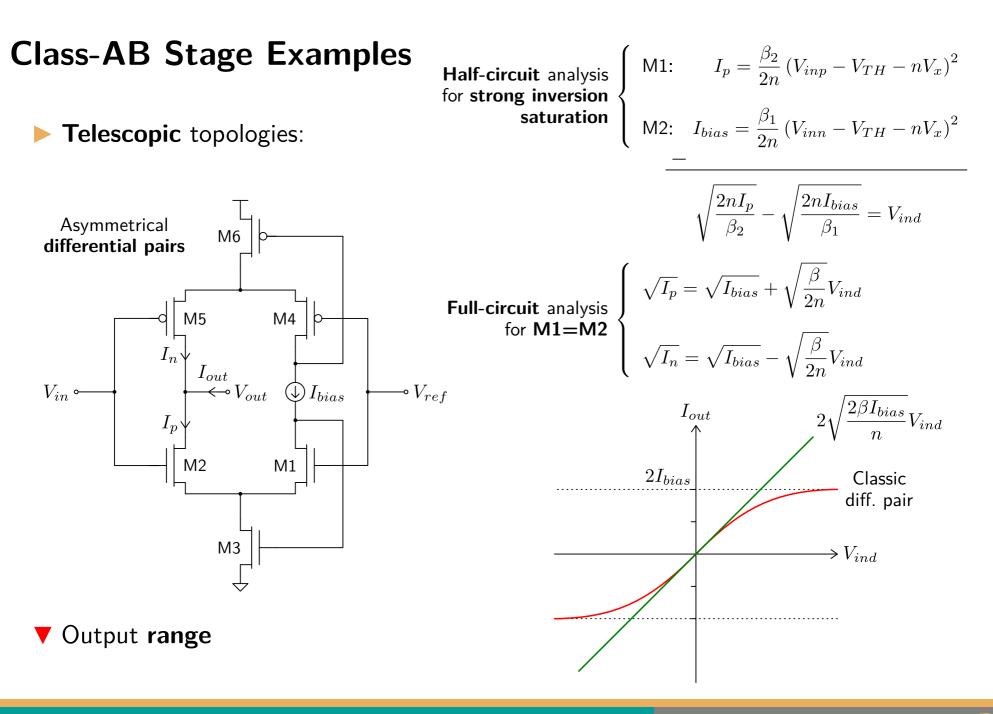

## **Output Operation Class**

OpAmp **power** investment:

**Output stage** operation modes:

## **Output Operation Class**

#### OpAmp **power** investment:

Class-E/F

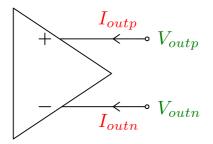

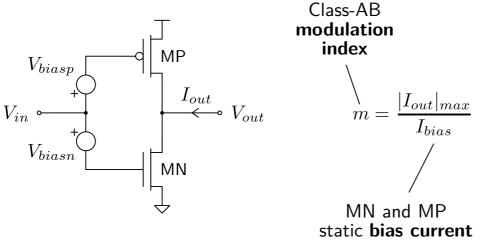

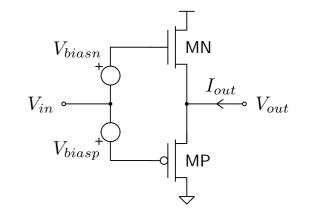

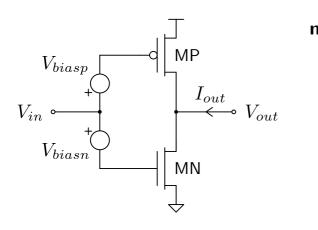

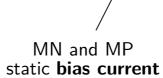

#### **Basic CMOS Topologies**

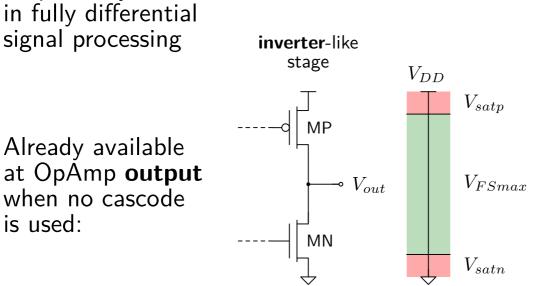

Inverter-like stage:

#### **Push-pull** type stage:

### **Basic CMOS Topologies**

Inverter-like stage:

modulation index  $M = \frac{|I_{out}|_{max}}{T}$

Class-AB

- High voltage gain

- Intrinsic high output impedance (1/g<sub>md</sub>)

- Suitable for capacitive loads only

- Optimized full-scale

#### **Push-pull** type stage:

- Unity voltage gain

- Intrinsic low **output impedance** (1/g<sub>ms</sub>)

- Suitable for any type of **load impedance**

- Reduced full-scale

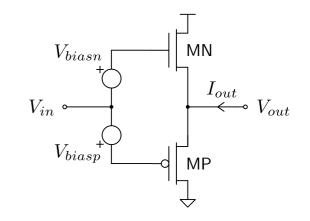

- Biasing circuitry to control I<sub>bias</sub> against PVT (CMOS process, supply voltage and temperature) corners and to reach high Class-AB m-values?

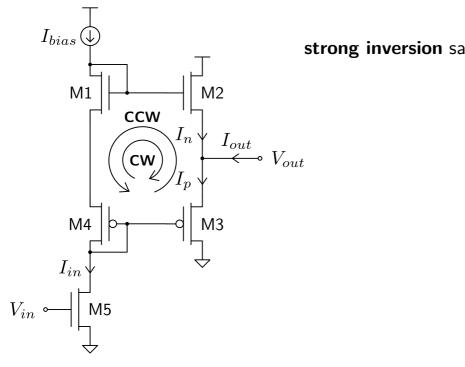

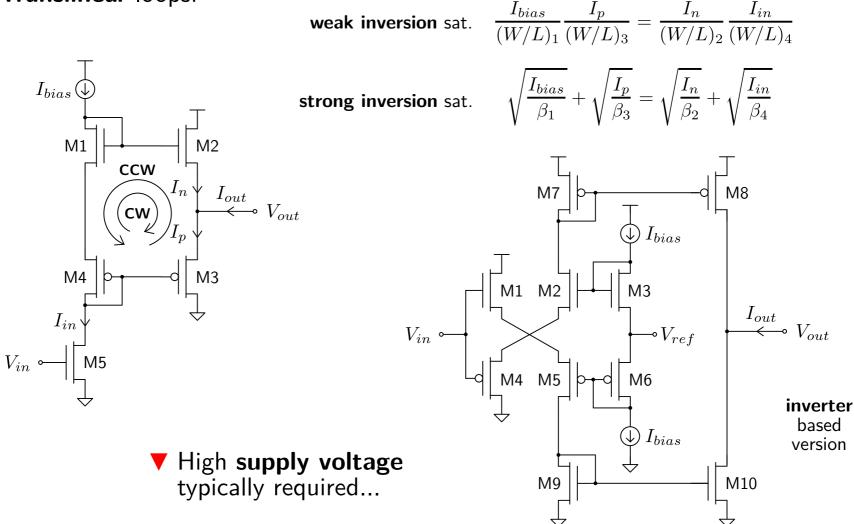

**Translinear** loops:

**Translinear** loops:

weak inversion sat

et.

$$\frac{I_{bias}}{(W/L)_1} \frac{I_p}{(W/L)_3} = \frac{I_n}{(W/L)_2} \frac{I_{in}}{(W/L)_4}$$

$$\int \frac{I_{bias}}{\beta_1} + \sqrt{\frac{I_p}{\beta_3}} = \sqrt{\frac{I_n}{\beta_2}} + \sqrt{\frac{I_{in}}{\beta_4}}$$

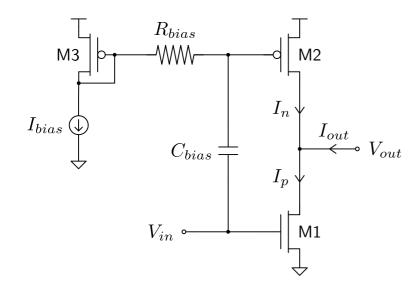

**Translinear** loops:

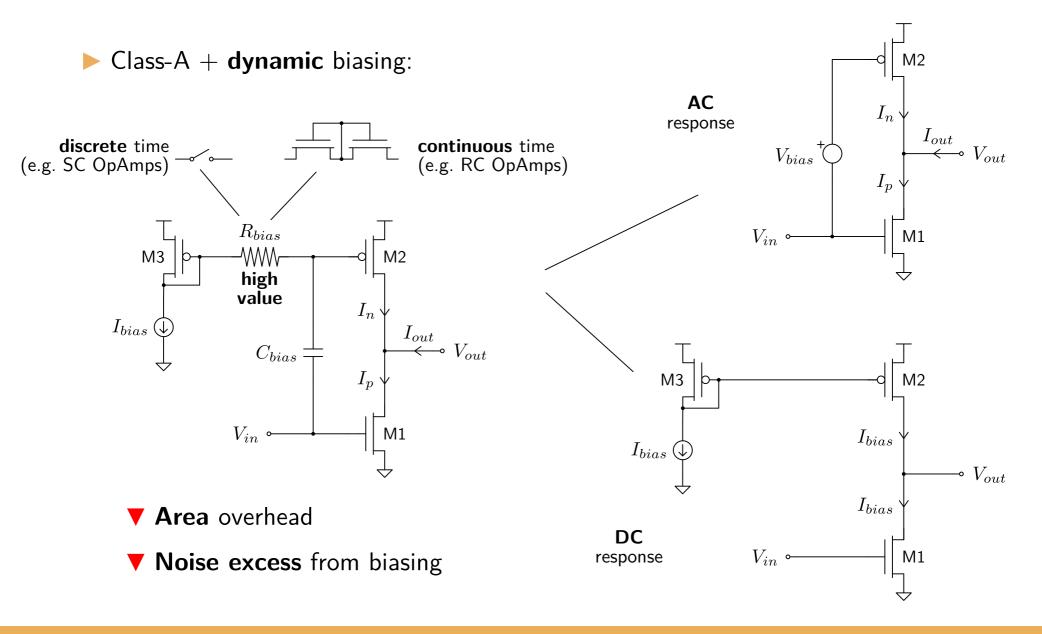

Class-A + dynamic biasing:

- 2 Subthreshold Operation

- 3 Class-AB Output Stages

- 4 Rail-to-Rail Topologies

- 5 Inverter-Based Pseudo-Differential Multi-Stages Architectures

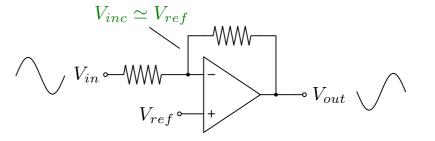

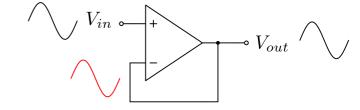

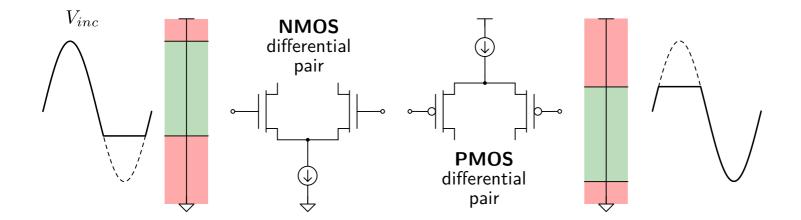

#### Why Rail-to-Rail?

- Optimization of signal full-scale  $(V_{FS})$  and probably dynamic range (DR)

- Compatibility with low supply voltages (e.g. battery-powered, energy scavenging)

Required by CMFB

signal processing

Vecessary at OpAmp input?

$V_{inc} \simeq V_{in}$

Required for certain feedback configurations!

Already available at OpAmp output when no cascode is used:

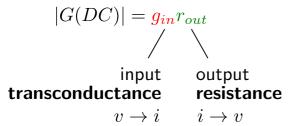

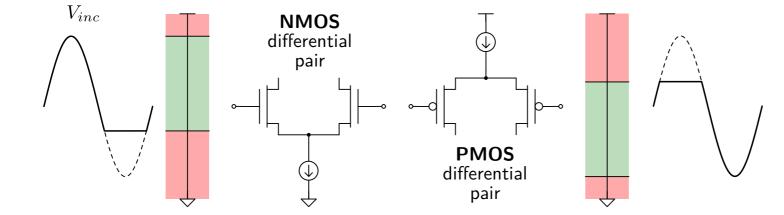

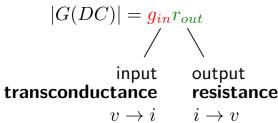

## **OpAmp Input Transconductance**

#### ► Overall **gain** performance:

#### **Input** transconductor for rial-to-rail?

## **OpAmp Input Transconductance**

output

$i \to v$

resistance

input transconductance  $v \to i$

**Input** transconductor for rial-to-rail?

## **OpAmp Input Transconductance**

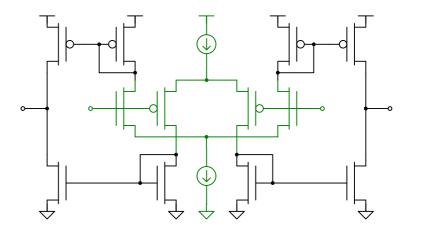

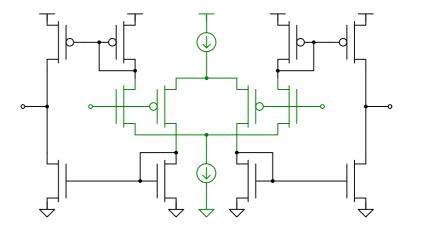

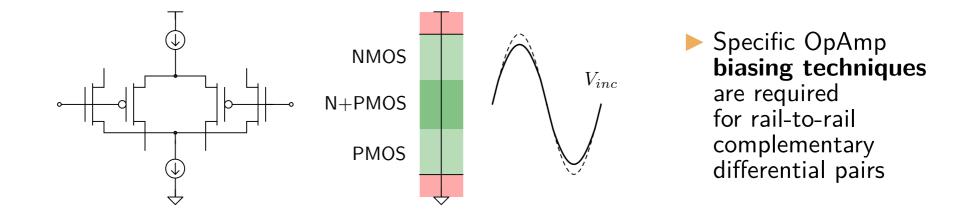

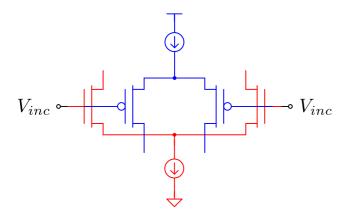

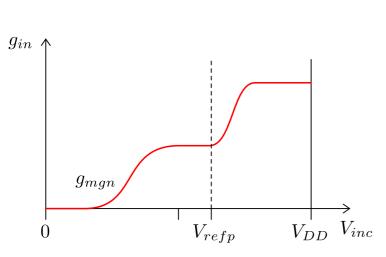

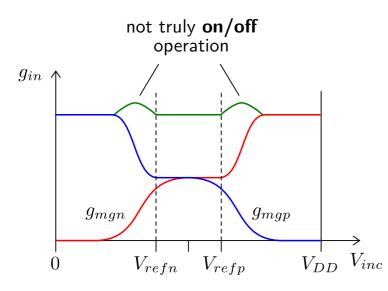

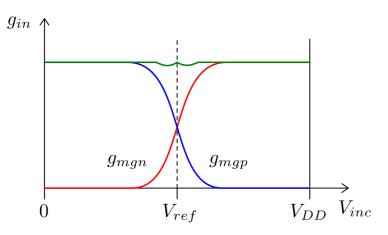

▲ **Complementary** differential pair

**Non-constant** transconductance (gain):

Complementary differential pair raw input transconductance:

Complementary differential pair raw input transconductance:

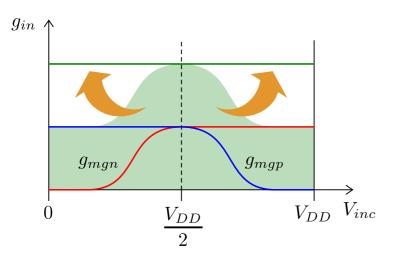

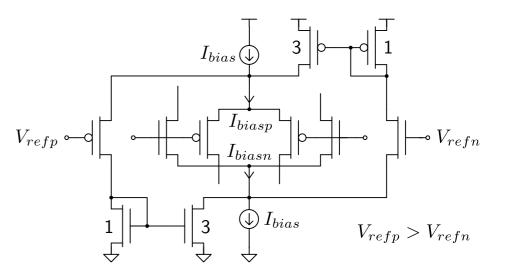

#### Equalization in strong inversion:

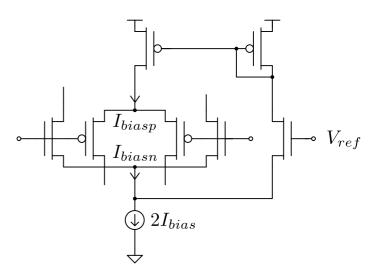

$g_{mgn} + g_{mgp} \equiv \text{const}$

$$\sqrt{2n\beta_n I_{biasn}} + \sqrt{2n\beta_p I_{biasp}} \equiv {\rm const}$$

e.g.

$$\frac{(W/L)_p}{(W/L)_n} \equiv \frac{\beta_{un}}{\beta_{up}} \sim 3$$

$$\sqrt{I_{biasn}} + \sqrt{I_{biasp}} \equiv \text{const}$$

$$\int I_{biasp}$$

$$\int I_{biasp}$$

$$\sqrt{I_{biasn}} + \sqrt{I_{biasn}} = \begin{cases} \sqrt{4I_{bias}} + \sqrt{0} = 2\sqrt{I_{bias}} & \text{NMOS} \\ \sqrt{I_{bias}} + \sqrt{I_{bias}} = 2\sqrt{I_{bias}} & \text{N+PMOS} \\ \sqrt{0} + \sqrt{4I_{bias}} = 2\sqrt{I_{bias}} & \text{PMOS} \end{cases}$$

$V_{inc}$

**Equalization in strong inversion**:

$$\sqrt{I_{biasn}} + \sqrt{I_{biasp}} = \begin{cases} \sqrt{4I_{bias}} + \sqrt{0} = 2\sqrt{I_{bias}} & \text{NMOS} \\ \sqrt{I_{biasn}} + \sqrt{I_{bias}} = 2\sqrt{I_{bias}} & \text{N+PMOS} \\ \sqrt{0} + \sqrt{4I_{bias}} = 2\sqrt{I_{bias}} & \text{PMOS} \end{cases}$$

**Equalization in strong inversion**:

$$\sqrt{I_{biasn}} + \sqrt{I_{biasp}} = \begin{cases} \sqrt{4I_{bias}} + \sqrt{0} = 2\sqrt{I_{bias}} & \text{NMOS} \\ \sqrt{I_{biasn}} + \sqrt{I_{bias}} = 2\sqrt{I_{bias}} & \text{N+PMOS} \\ \sqrt{0} + \sqrt{4I_{bias}} = 2\sqrt{I_{bias}} & \text{PMOS} \end{cases}$$

- ▲ **Compact** bias control

- **Non-exact** solution

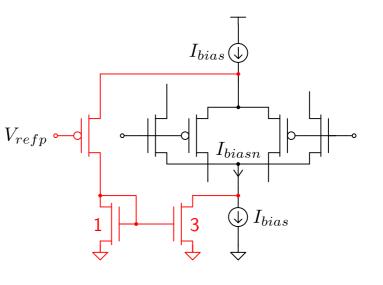

#### **Current Switch**

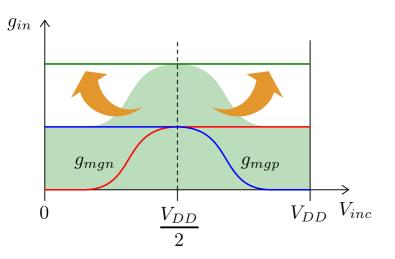

**Equalization in weak inversion**:

$g_{mgn} + g_{mgp} \equiv \text{const}$

$$\frac{I_{biasn}}{nU_t} + \frac{I_{biasp}}{nU_t} \equiv \text{const}$$

$$I_{biasn} + I_{biasp} \equiv \text{const}$$

▲ **Compact** bias control

Transconductance equalization sensitivity to reference voltage

- 2 Subthreshold Operation

- 3 Class-AB Output Stages

- 4 Rail-to-Rail Topologies

- 5 Inverter-Based Pseudo-Differential Multi-Stages Architectures

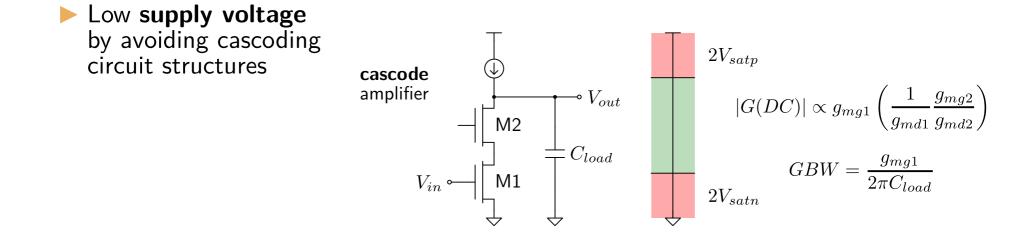

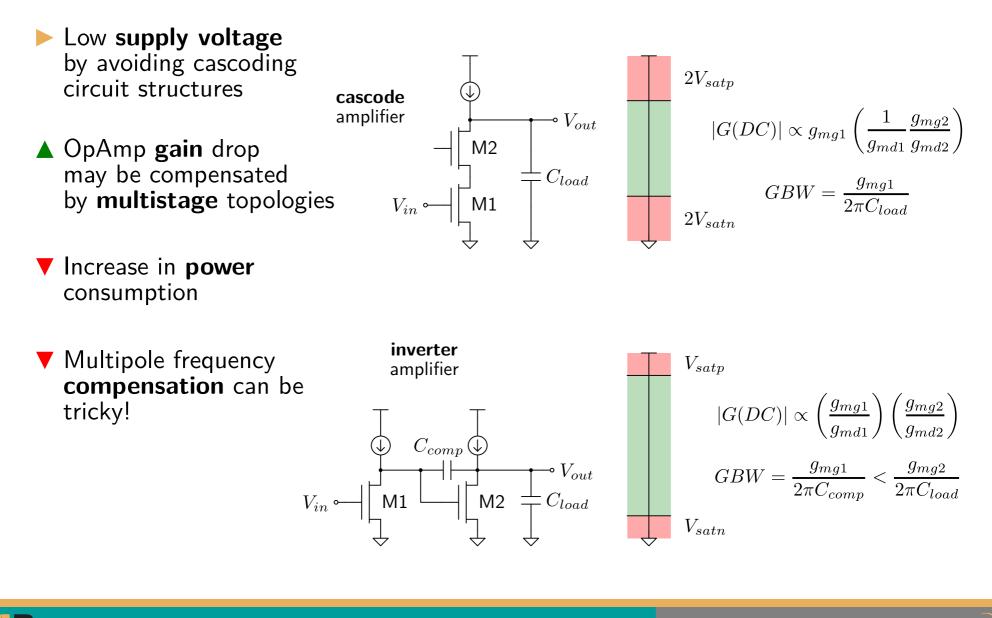

### **Cascade vs Cascode**

### Cascade vs Cascode

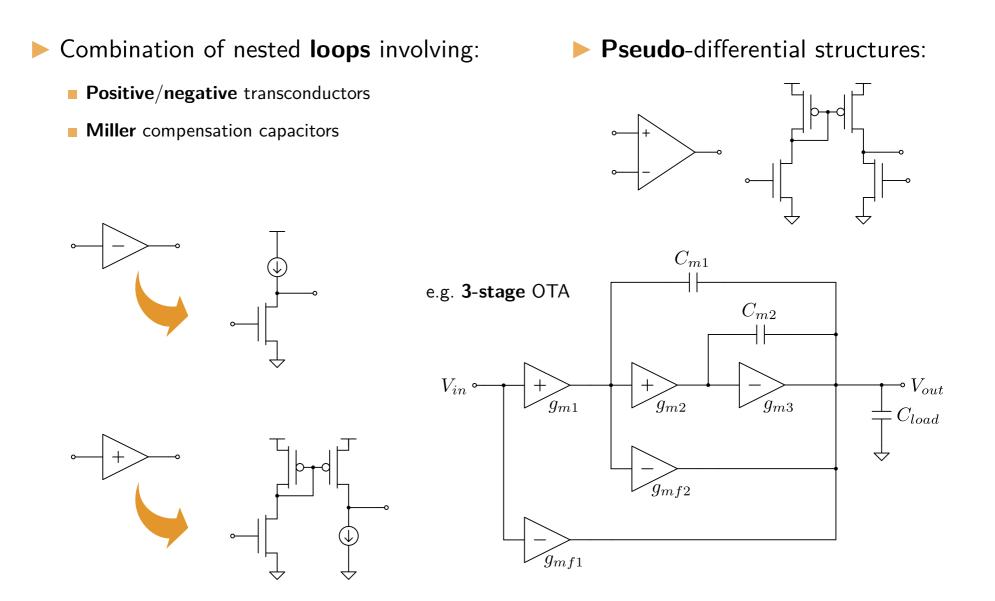

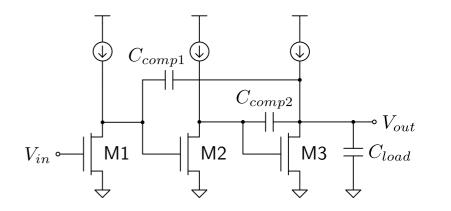

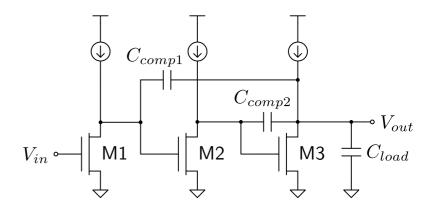

## **3-Stage Nested Miller OTA**

Inverter as transconductance basic building block

$$GBW = \frac{g_{mg1}}{2\pi C_{comp1}} \qquad f_{p2} = \frac{g_{mg2}}{2\pi C_{comp2}} \qquad f_{p3} = \frac{g_{mg3}}{2\pi C_{load}}$$

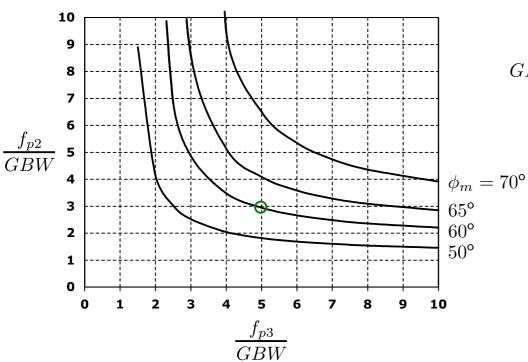

## **3-Stage Nested Miller OTA**

- Inverter as transconductance basic building block

- ▲ Phase margin save design

$$GBW = \frac{g_{mg1}}{2\pi C_{comp1}} \qquad f_{p2} = \frac{g_{mg2}}{2\pi C_{comp2}} \qquad f_{p3} = \frac{g_{mg3}}{2\pi C_{load}}$$

$$\phi_m = 90^{\circ} - \arctan\left(\frac{GBW}{f_{p2}}\right) - \arctan\left(\frac{GBW}{f_{p3}}\right)$$

Increase in power consumption

**Bandwidth** reduction

## **Nested Gm-C Compensation**