# 4. Full-Custom Analog Design Methodology

Francesc Serra Graells

francesc.serra.graells@uab.cat Departament de Microelectrònica i Sistemes Electrònics Universitat Autònoma de Barcelona

> paco.serra@imb-cnm.csic.es Integrated Circuits and Systems IMB-CNM(CSIC)

Design of Analog and Mixed Integrated Circuits and Systems F. Serra Graells

#### 1 Device Sizing

- 2 Process and Mismatching Simulation

- 3 The Art of Analog Layout

- 4 Physical Verification

- 5 Parasitics Extraction

#### 6 DFM Techniques

#### 1 Device Sizing

- 2 Process and Mismatching Simulation

- 3 The Art of Analog Layout

- 4 Physical Verification

- 5 Parasitics Extraction

#### 6 DFM Techniques

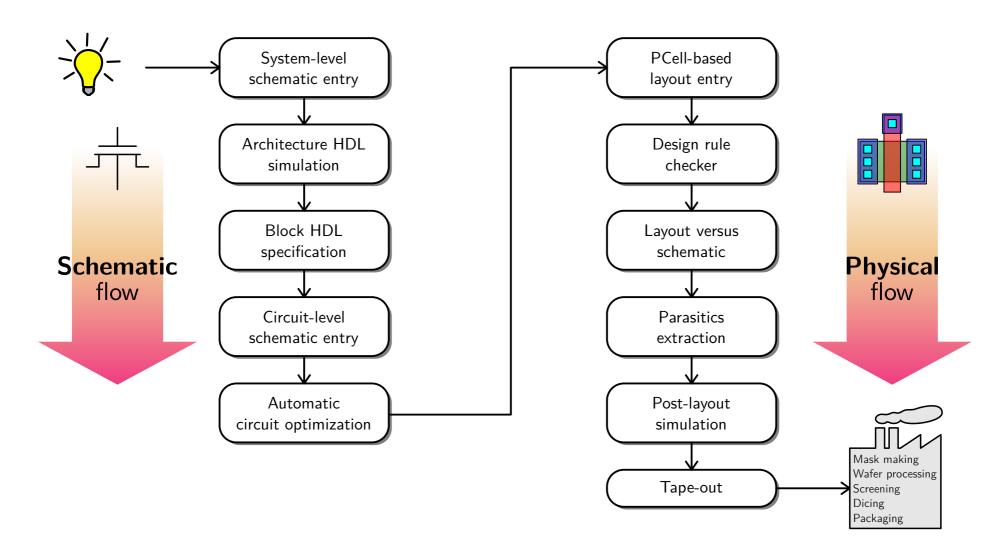

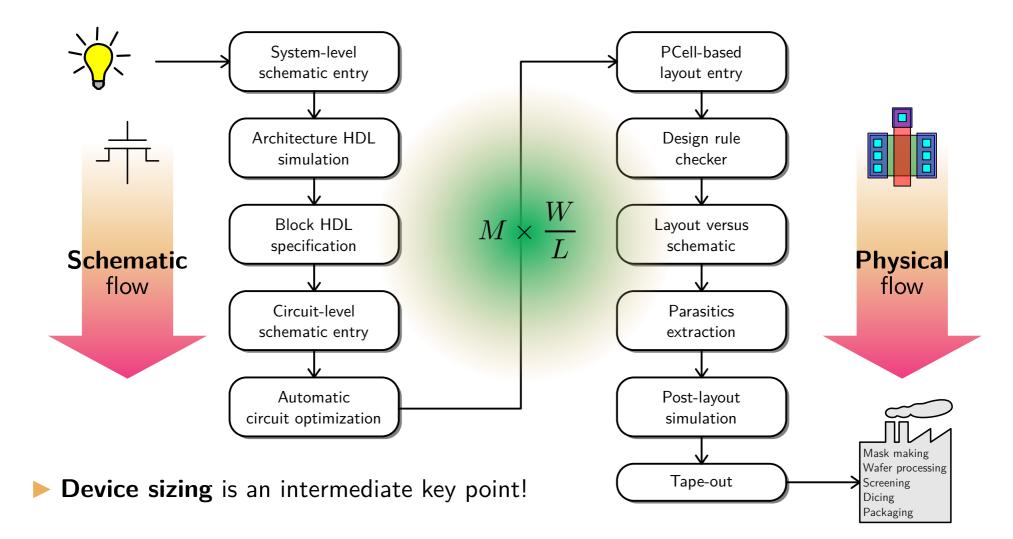

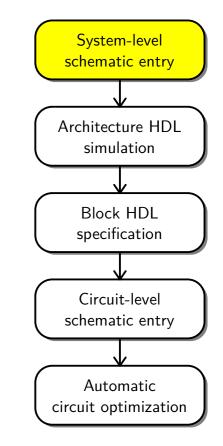

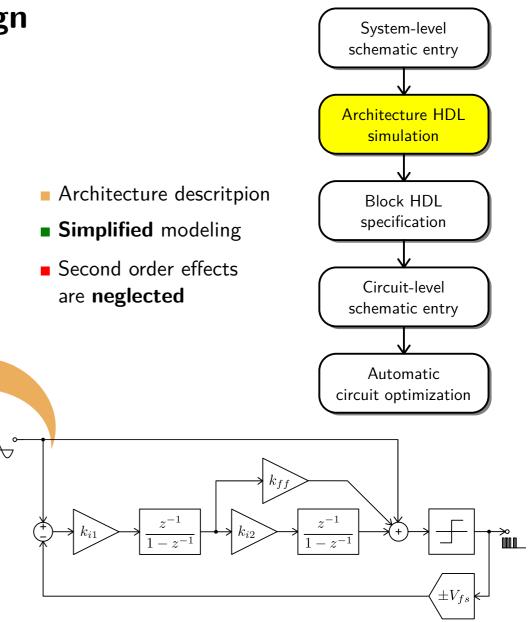

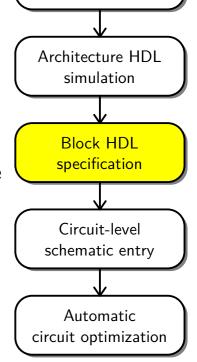

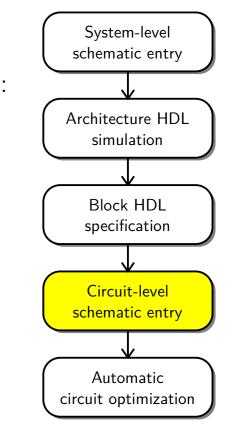

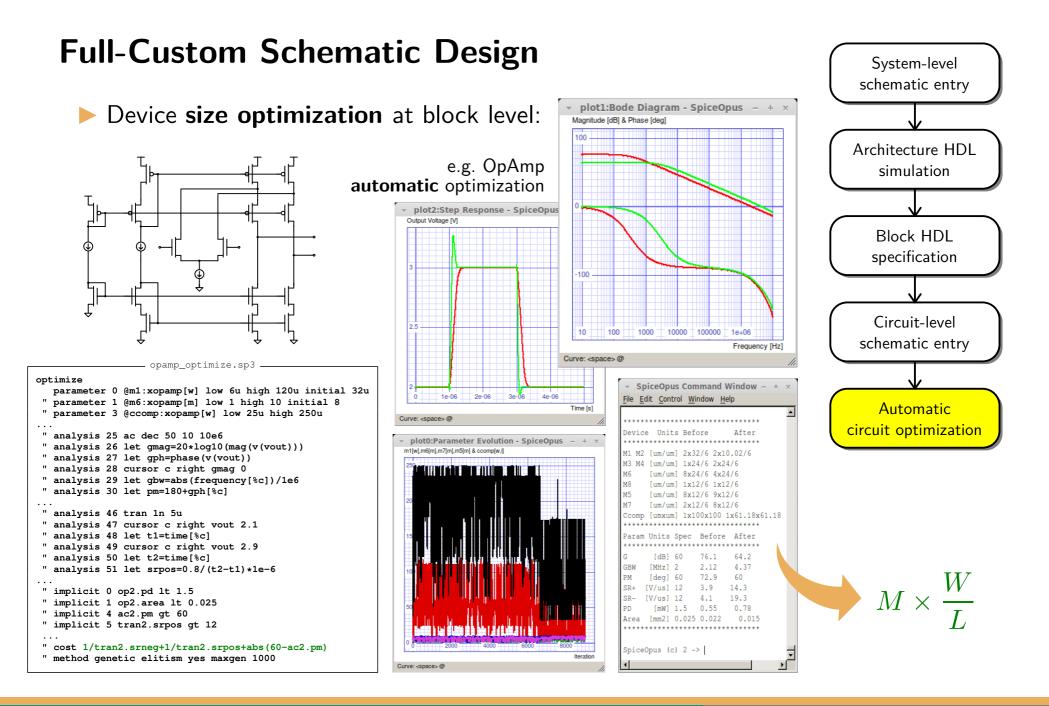

# **Full-Custom Analog IC Design Flow**

From circuit **idea to layout** masks...

▲ EDA-assisted methodology

# **Full-Custom Analog IC Design Flow**

From circuit **idea to layout** masks...

▲ EDA-assisted methodology

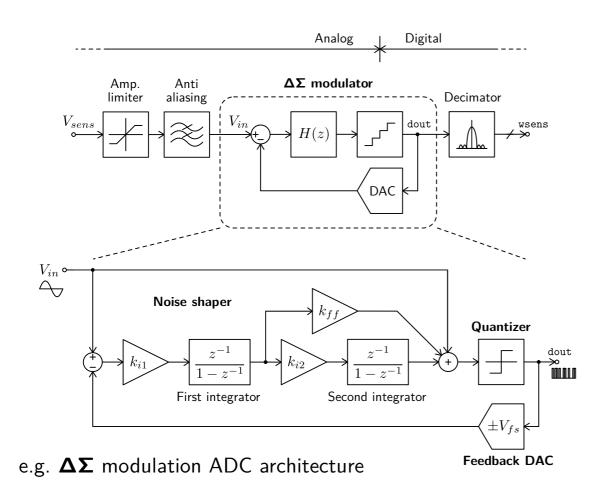

Architecture selection according to system and application specifications:

- Signal processing performance

- Communications standards

- Power constraints

- Testbility requirements

- ... and many more!

```

System modeling through any

hardware descitpion language (HDL)

```

```

_____ zinteg2lim.mod _

void cm_zinteg2lim(ARGS) {

inp = INPUT(inp);

/* Retriving input values */

clk = INPUT_STATE(clk);

pos_edge = PARAM(pos_edge); /* Retrieving parameters */

out_max = PARAM(out_ax);

. . .

switch (ANALYSIS) {

case TRANSIENT:

if ((*clk_mem==ONE)&&(clk==ZERO)) {/* Neq. clk edge */

if (pos_edge==FALSE)

action = SAMPLING_INTEGRATION;

} else {

if ((*clk_mem==ZERO)&&(clk==ONE)) {/* Pos. clk edge*/

if (pos_edge==TRUE)

action = SAMPLING_INTEGRATION;

} else {

/* No clock edge */

action = HOLDING;

}

\sim

switch (action) {

case SAMPLING_INTEGRATION:

*inp_mem = inp;

out = *out_mem+*inp_mem;

/* Limiter */

if (out<out_min) { out = out_min; }</pre>

if (out>out_max) { out = out_max; }

*out mem = out;

break;

case HOLDING:

out = *out mem;

}}

```

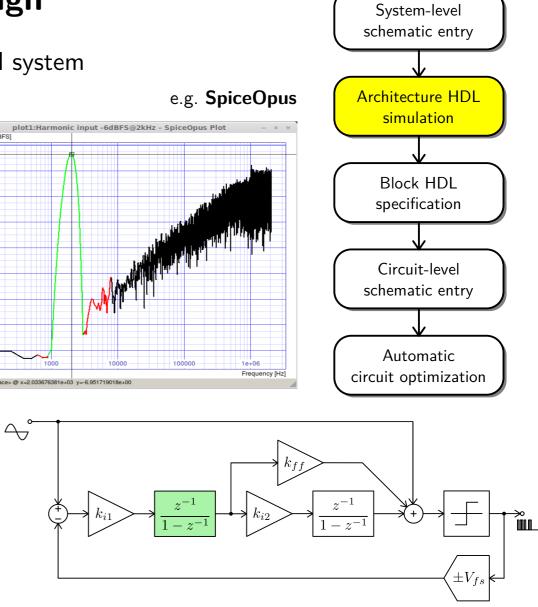

#### HDL numerical simulation of the full system using event-based engines

- Architecture evaluation

- Simulation speed-up by orders of magnitude

- Ideal response (maximum possible performance)

```

_ dsm-arch.sub

.subckt dsm arch vin dclk dout

asumin [%v(vin) %v(vdac)] %v(verr) msumin

.model msumin usummer(sign=[1.0 -1.0])

aki1 %v(verr) %v(vintlin) mki1

.model mki1 kgain(k=0.3)

azint1 %v(vint1in) %d(dclk) %v(vint1out) mzint1

.model mzint1 zinteg2lim(pos_edge=0 out_ic=0.0

+ out min=-5.0 out max=5.0)

aki2 %v(vint1out) %v(vint2in) mki2

.model mki2 kgain(k=0.7)

azint2 %v(vint2in) %d(dclk) %v(vint2out) mzint2

.model mzint2 zinteg2lim(pos_edge=0 out_ic=0.0

+ out_min=-5.0 out_max=5.0)

akff %v(vintlout) %v(vkffout) mkff

.model mkff kgain(k=2.0)

asumout [%v(vint2out) %v(vkffout) %v(vin)]

+ %v(vquantin) msumout

.model msumout usummer(sign=[1.0 1.0 1.0])

aquant %v(vquantin) %d(~dclk) %d(dout) mquant

.model mquant quant21sh(inp_th=0.0 out_ic=0 pos_edge=0

+ t_rise=1e-9 t_fall=1e-9)

adac %d(dout) %v(vdac) mdac

.model mdac dac21sym(out_level=2.0)

.ends

```

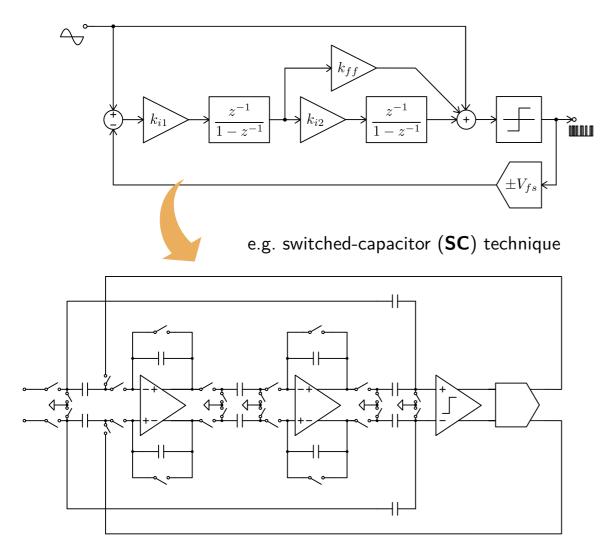

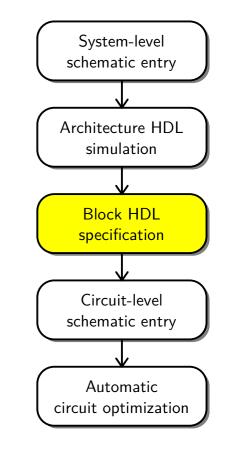

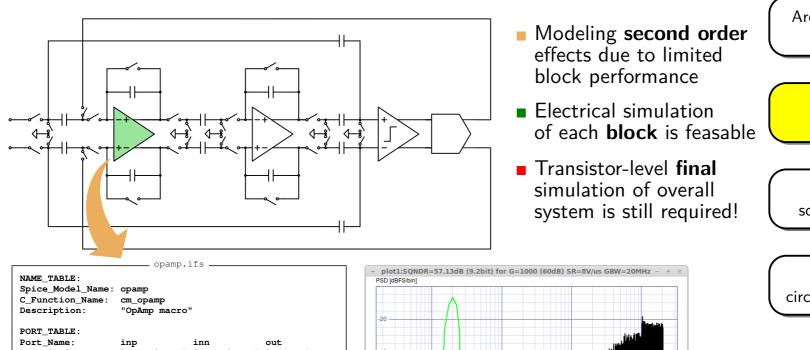

Choosing most suitable circuit technique according to:

- CMOS technology options

- Circuit sensitivity against process, supply and temperature (PVT)

- IC operation conditions (calibration, testability...)

- **External** components available

**Splitting** system design problem into independent **blocks**:

System-level schematic entry

Description: "pos. input" "neg. input" "output" Direction: in in out Default\_Type: v v v PARAMETER TABLE: Parameter\_Name: G GBW SR Description: "DC OL gain" "GBW" "slew-rate" Data\_Type: real real real Default Value: 1000 1e6 1e6 Limits: [0 -1 [0 -] [0 -] PARAMETER TABLE: Parameter\_Name: out\_min out\_max Description: "lower out limit" "upper out limit" Data\_Type: real real Default\_Value: 0 5.0 Limits: [0 5.0] [0 5.0] . . .

e.g. limited {G,GBW,SR} **Opamp** macro model

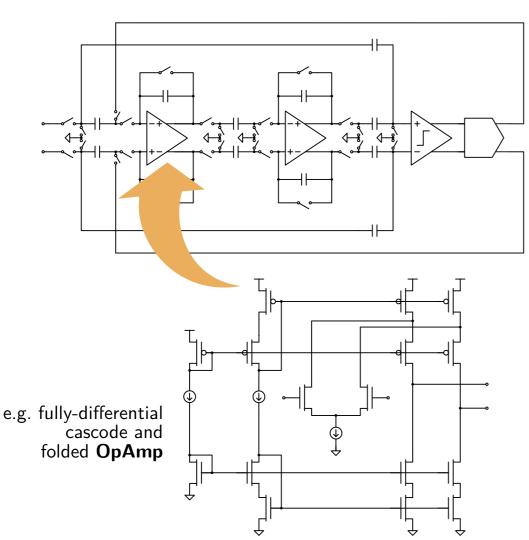

Choosing the particular circuit topology for each system block:

- Separated block tests

- Target specs from previous step e.g. {G,GBW,SR}

- Fast and accurate electrical simulations

- Several topologies can be easily investigated

- Inter-block coupled effects not covered!

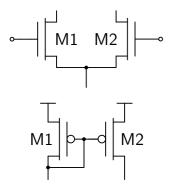

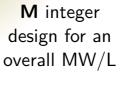

# **MOSFET Sizing Analog Guidelines**

Transistor (also other devices) matching ratios:

multiplicity (**M**) design for a common channel aspect ratio (W/L)

$$M \times \frac{W}{I}$$

Device output impedance:

$$\lambda \propto \frac{1}{L} \downarrow$$

non-minimum channel length (L) above design rules for a given W/L

> **M** and **W/L** design for a given absolute L value

overall

MOS transconductance:

$$M\frac{W}{L}\uparrow \quad g_{mg,s}\uparrow$$

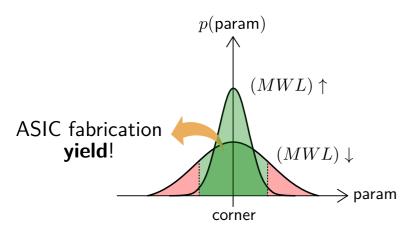

**Bandwidth**, technology **mismatching** and **flicker** noise:  $C = \frac{\epsilon_{ox}}{MWL}$

device area (**MWL**)  $\sigma (\Delta design for a given M and W/L <math>\frac{dv_{nfk}^2}{dv_{nfk}^2}$

$$\sigma(\Delta P) \simeq \frac{A_P}{\sqrt{MWL}}$$

$$\frac{dv_{nfk}^2}{df} = \frac{K_{fk}}{MWL} \frac{1}{f}$$

Physical layout considerations:

e.g. M **even** values for common centroid layout techniques

#### 1 Device Sizing

#### 2 Process and Mismatching Simulation

- 3 The Art of Analog Layout

- 4 Physical Verification

- 5 Parasitics Extraction

#### 6 DFM Techniques

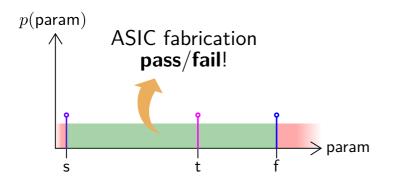

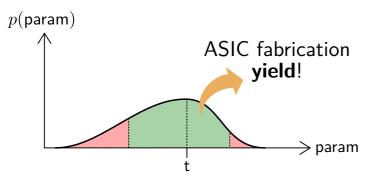

#### **Process Simulation**

Global deviations of model parameters:

- Same change in all devices of the ASIC

- Worse-case **corner** analysis: (t)yp, (f)ast, (s)low...

```

cnm25proc.lib

* CNM25 process corners

.lib common

.model cnm25modn nmos LEVEL = 2

+ TOX = 380E - 10

VTO = \{vton\}

NSUB = 2.64E16 \quad UO = \{uon\}

+ UCRIT = 1E4

UEXP = 6.86E-2 NFS = 7.11E11

+ DELTA = 2.20

RS = 93.8

LD = 9.13E-7

XJ = 8.24E - 8

+ VMAX = 5.96E4

NEFF = 1.48

CJ = 3.50E - 4

MJ = .40

+ CJSW = 5.95E-10 MJSW = .29

PB = .65

+ AF

=1.33 KF

=1e-29

.model cnm25modp pmos LEVEL = 2

+ TOX = 380E - 10

VTO = \{vtop\}

NSUB = 1.36E16 \quad UO = \{uop\}

+ UCRIT = 1E4

UEXP = 1.16E-1 NFS = 6.62E11

+ DELTA = 1.82

RS = 134.9

LD = 8.10E-7

XJ = 2.78E - 9

+ VMAX = 1.20E5

NEFF = 6.67E-2 CJ = 3.82E-4

MJ = .35

+ CJSW = 7.38E-10 MJSW = .39

PB = .56

+ AF

=1.33 KF

=1e-29

.model cnm25cpoly c CJ= 4.227E-4 CJSW=0.0

.endl

.lib tt

.param vton=.942

.param vtop=-1.139

.param uon=648

.param uop=213

.lib 'cnm25proc.lib' common

.endl

.lib ss

V_{TH}\uparrow_{

m slow}

.param vton=1.1

.param vtop=-1.3

.param uon=415

\beta \downarrow

.param uop=131

.lib 'cnm25proc.lib' common

.endl

.lib ff

V_{TH}\downarrow_{\mathsf{fast}}

.param vton=0.7

.param vtop=-0.9

.param uon=881

\beta \uparrow

.param uop=295

.lib 'cnm25proc.lib' common

.endl

```

## **Process Simulation**

Global deviations of model parameters:

- Same change in all devices of the ASIC

- Worse-case **corner** analysis: (t)yp, (f)ast, (s)low...

- Combined corners: process/voltage/temperature (PVT)

Montecarlo statistical analysis:

```

cnm25proc.lib

* CNM25 process corners

.lib common

.model cnm25modn nmos LEVEL = 2

VTO = \{vton\}

+ TOX = 380E - 10

NSUB = 2.64E16 UO = {uon}

+ UCRIT = 1E4

UEXP = 6.86E-2 NFS = 7.11E11

+ DELTA = 2.20

RS = 93.8

LD = 9.13E-7

XJ = 8.24E - 8

+ VMAX = 5.96E4

NEFF = 1.48

CJ = 3.50E - 4

MJ = .40

+ CJSW = 5.95E-10 MJSW = .29

PB = .65

+ AF

=1.33 KF

=1e-29

.model cnm25modp pmos LEVEL = 2

+ TOX = 380E - 10

VTO = \{vtop\}

NSUB = 1.36E16 \quad UO = {uop}

+ UCRIT = 1E4

UEXP = 1.16E-1 NFS = 6.62E11

+ DELTA = 1.82

RS = 134.9

LD = 8.10E-7

XJ = 2.78E - 9

+ VMAX = 1.20E5

NEFF = 6.67E-2 CJ = 3.82E-4

MJ = .35

+ CJSW = 7.38E-10 MJSW = .39

PB = .56

+ AF

=1.33 KF

=1e-29

.model cnm25cpoly c CJ= 4.227E-4 CJSW=0.0

.endl

.lib tt

.param vton=.942

.param vtop=-1.139

.param uon=648

.param uop=213

.lib 'cnm25proc.lib' common

supply voltage

.endl

.lib ss

.param vton=1.1

V_{TH}\uparrow

.param vtop=-1.3

slow

.param uon=415

\beta \downarrow

.param uop=131

.lib 'cnm25proc.lib' common

.endl

fs

tt

.lib ff

temp.

SS

.param vton=0.7

N/PMOS

V_{TH}\downarrow

.param vtop=-0.9

fast

.param uon=881

\beta \uparrow

.param uop=295

.lib 'cnm25proc.lib' common

.endl

```

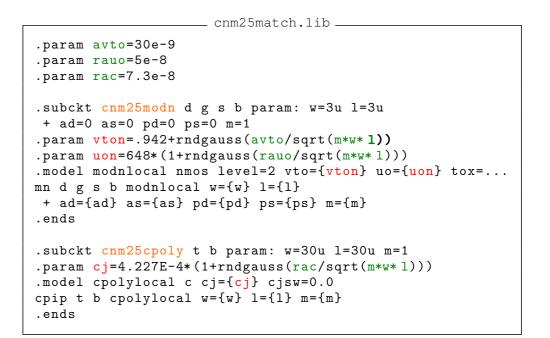

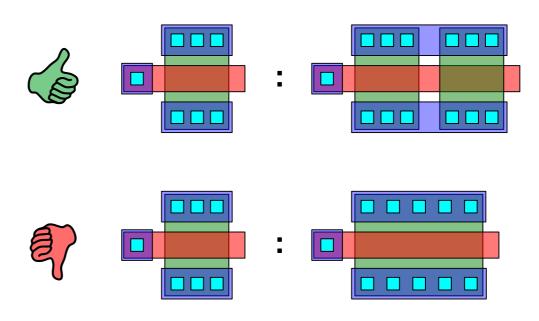

# **Mismatching Simulation**

- **Local** deviations of model parameters:

- Different change for each device of the ASIC

Ţ

- Pelgrom Law

- **Montecarlo** statistical analysis:

#### 1 Device Sizing

- 2 Process and Mismatching Simulation

- 3 The Art of Analog Layout

- 4 Physical Verification

- 5 Parasitics Extraction

#### 6 DFM Techniques

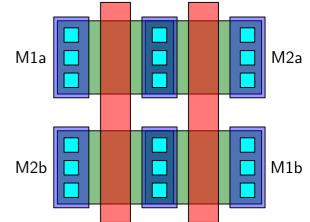

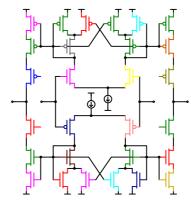

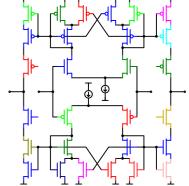

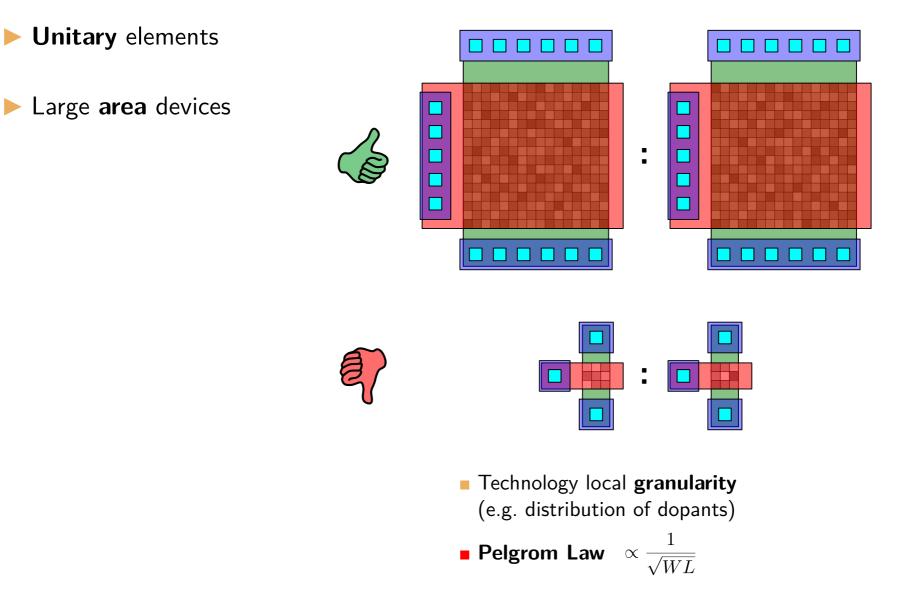

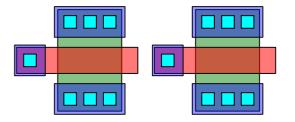

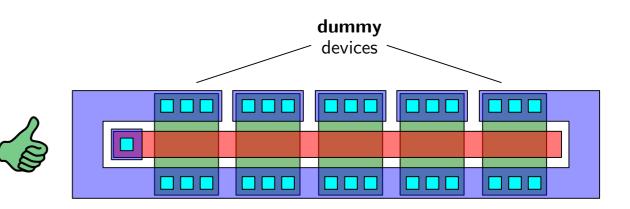

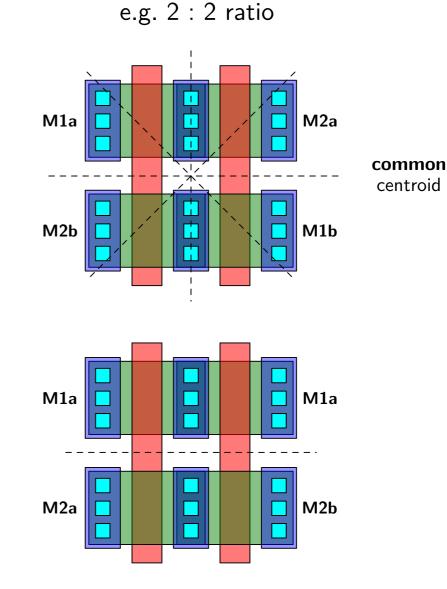

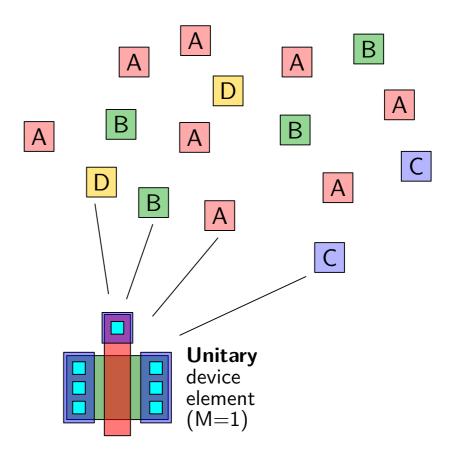

**Unitary** elements

e.g. 1 : 2 ratio

- Play with multiplicity only

- Same ratio for second order effects also (e.g. area and perimeter ratio in caps)

- **Larger area** for the overall array

e.g. 1 : 1 ratio

- **Unitary** elements

- Large area devices

- Minimum distance

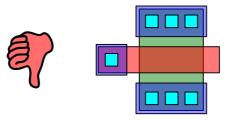

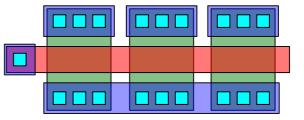

e.g. 1 : 1 ratio

- Technology global drifts

(e.g. gate oxide thickness slope)

- **Design rule** spacing limits

- Unitary elements

- Large area devices

- Minimum distance

- Same orientation

Anisotropic materials (e.g. wafer crystal lattice orientation)

F. Serra Graells

Longer **routing** may be required...

- **Unitary** elements

- Large area devices

- Minimum distance

- Same orientation

- Same sorround

e.g. 1 : 1 : 1 ratios

- Inter-device second order effects (e.g. parasitic RLC)

- Larger area for the overall array

- Unitary elements

- Large area devices

- Minimum distance

- Same orientation

- Same sorround

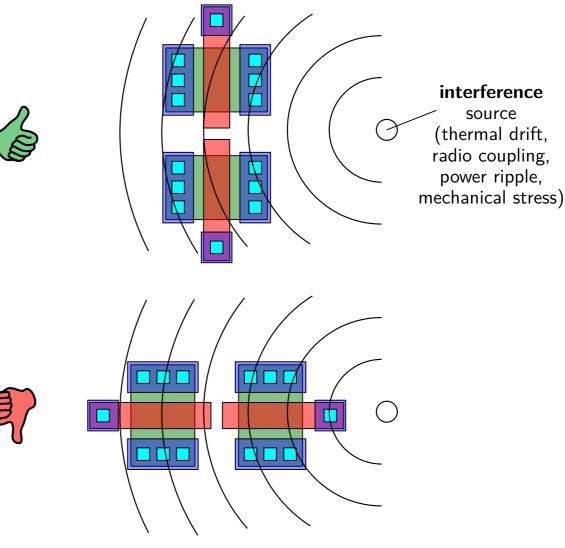

- Same symmetry

- Differential circuits (common mode interference)

- Complex floorplan

- **Unitary** elements

- Large area devices

- Minimum distance

- Same orientation

- Same sorround

- Same symmetry

- Compensation of linear gradients (and non-linear at short distance)

- **Longer routing** is usually required...

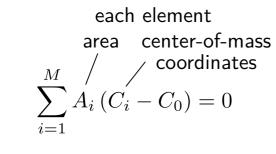

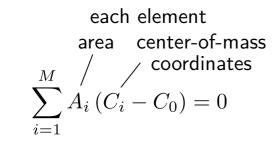

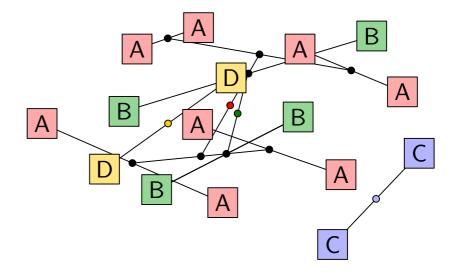

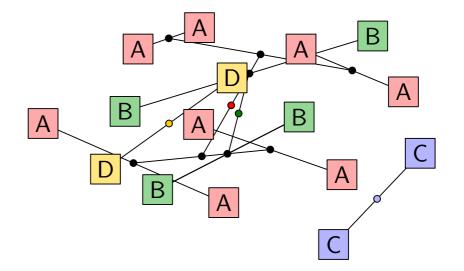

Difficult to achieve for large and multiple groups of unitary elements e.g. A : B : C : D ratios 8 4 2 2

- Difficult to achieve for large and multiple groups of unitary elements

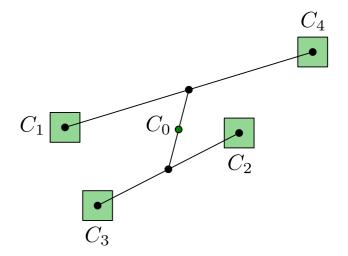

- Centroid as a center-of-mass concept, but with area weights...

centroid coordinates  $C_0 = \frac{\sum_{i=1}^{M} A_i C_i}{\sum_{i=1}^{M} A_i}$

If all elements are of same area:

$$C_0 \equiv \frac{1}{M} \sum_{i=1}^{M} C_i$$

$C_1 \bullet$  $C_3$

$C_4$

•

$C_2$

- Difficult to achieve for large and multiple groups of unitary elements

- Centroid as a center-of-mass concept, but with area weights...

centroid coordinates  $C_0 = \frac{\sum_{i=1}^{M} A_i C_i}{\sum_{i=1}^{M} A_i}$

If all elements are of **same area**:

$$C_0 \equiv \frac{1}{M} \sum_{i=1}^M C_i$$

Center-of-area is the **average** of elements positions...

- Difficult to achieve for large and multiple groups of unitary elements

- Centroid as a center-of-mass concept, but with area weights...

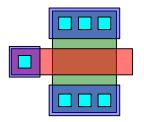

- ▲ **Centroid**-based golden rules:

- Coincidence of all centroids

e.g. A : B : C : D ratios 8 4 2 2

Not a common centroid arrangement!

- Difficult to achieve for large and multiple groups of unitary elements

- Centroid as a center-of-mass concept, but with area weights...

- ▲ **Centroid**-based golden rules:

- Coincidence of all centroids

- Symmetry for X and Y axes

e.g. A : B : C : D ratios 8 4 2 2

|   |   |   |   |   |   |   | Α |

|---|---|---|---|---|---|---|---|

| A | Α | В | D | С | В | A | Α |

- Difficult to achieve for large and multiple groups of unitary elements

- Centroid as a center-of-mass concept, but with area weights...

- ▲ **Centroid**-based golden rules:

- Coincidence of all centroids

- Symmetry for X and Y axes

- Dispersion of groups as uniformly as possible

e.g. A : B : C : D ratios 8 4 2 2

| Α | A | В | С | D | В | Α | A |

|---|---|---|---|---|---|---|---|

| Α | Α | В | D | С | В | Α | A |

| Α | В | A | С | Α | D | Α | В |

|---|---|---|---|---|---|---|---|

| В | A | D | A | C | A | В | Α |

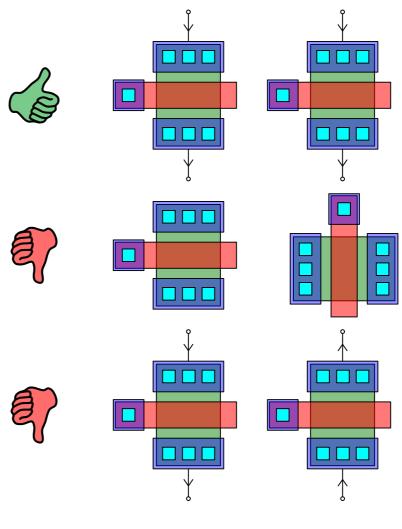

- Difficult to achieve for large and multiple groups of unitary elements

- Centroid as a center-of-mass concept, but with area weights...

- ▲ **Centroid**-based golden rules:

- Coincidence of all centroids

- Symmetry for X and Y axes

- Dispersion of groups as uniformly as possible

- Compactness of overall array to ideal square shape

e.g. A : B : C : D ratios 8 4 2 2

| Α | В | Α | С | Α | D | A | В |

|---|---|---|---|---|---|---|---|

| В | A | D | A | С | Α | В | A |

| Α | В | Α | В |

|---|---|---|---|

| С | A | D | Α |

| Α | D | A | С |

| В | A | В | Α |

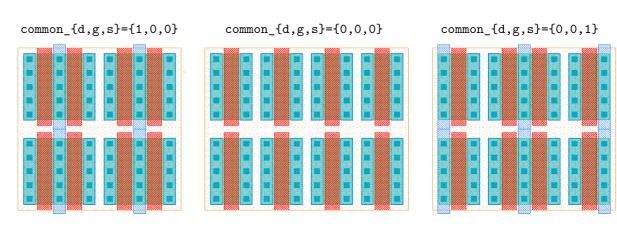

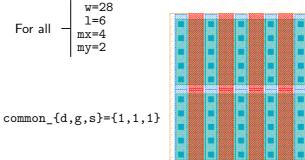

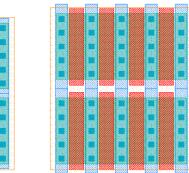

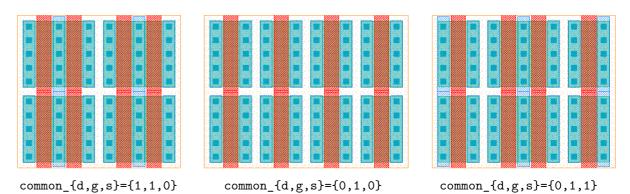

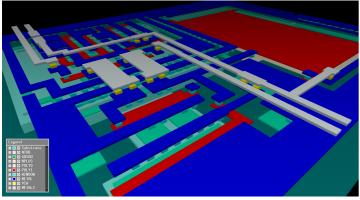

# **PCell-Based Layout**

- ▲ Unitary elements

- ▲ **Regular** geometry

- ▲ Design rule compliant

common\_{d,g,s}={1,0,1}

e.g. CNM25 NMOSFET parameterized cell (PCell)

Design of Analog and Mixed Integrated Circuits and Systems F. Serra Graells

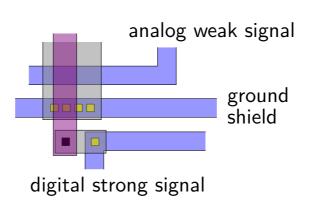

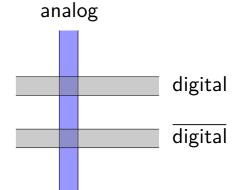

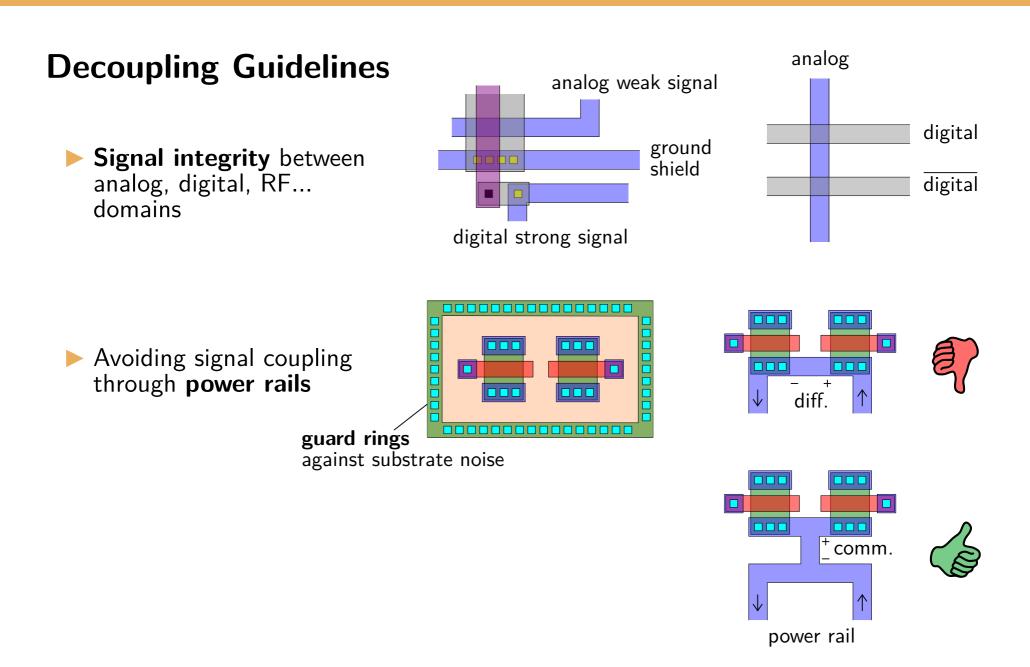

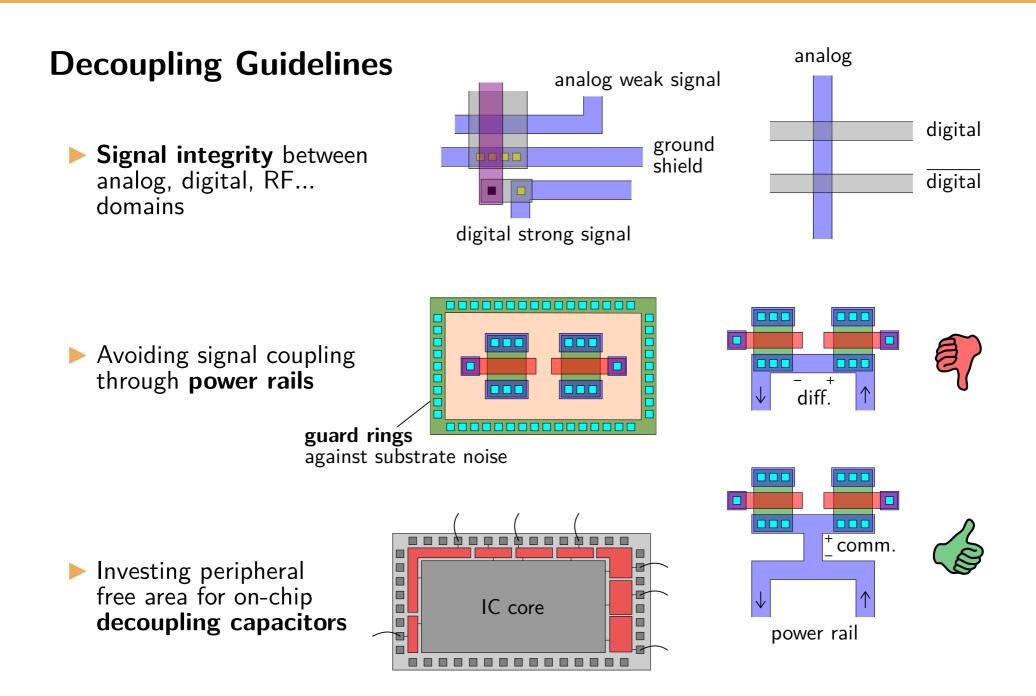

# **Decoupling Guidelines**

Signal integrity between analog, digital, RF... domains

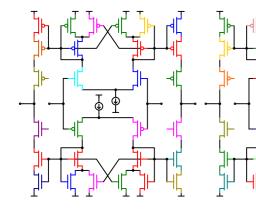

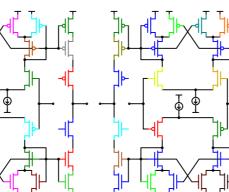

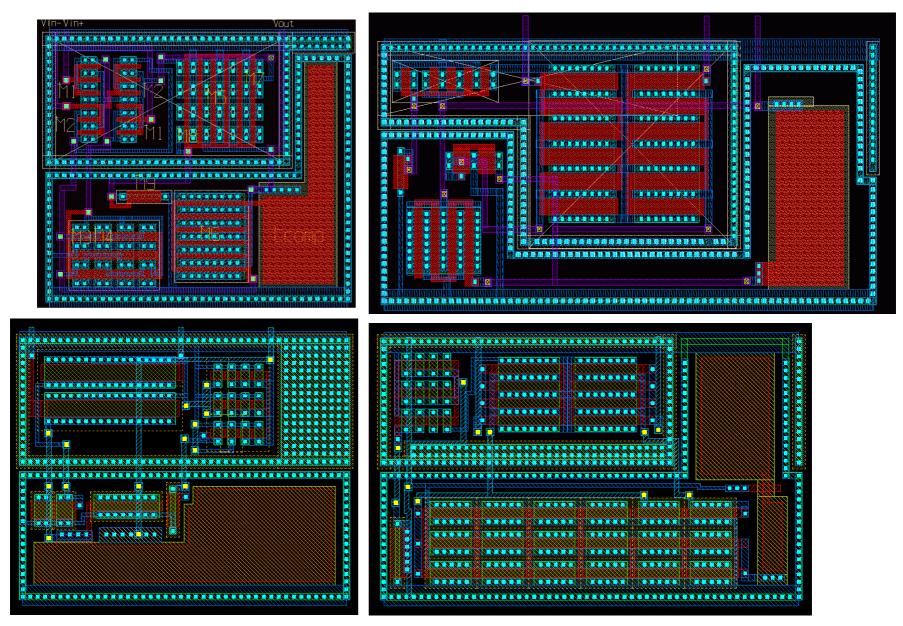

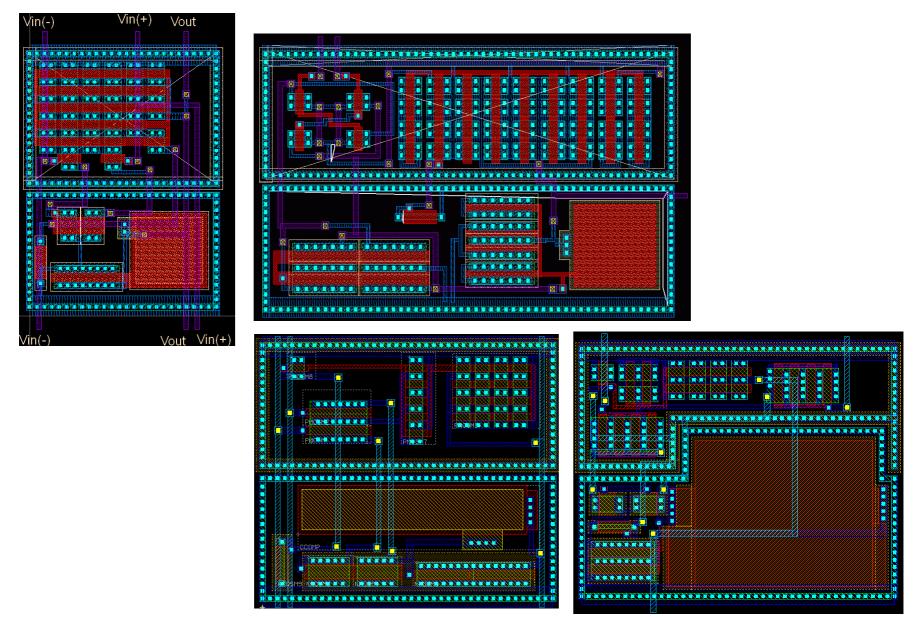

# **OpAmp Layout Examples**

Let's evaluate other students work....

UAB

# **OpAmp Layout Examples**

Let's evaluate other students work....

UAB

# 1 Device Sizing

- 2 Process and Mismatching Simulation

- 3 The Art of Analog Layout

- 4 Physical Verification

- 5 Parasitics Extraction

# 6 DFM Techniques

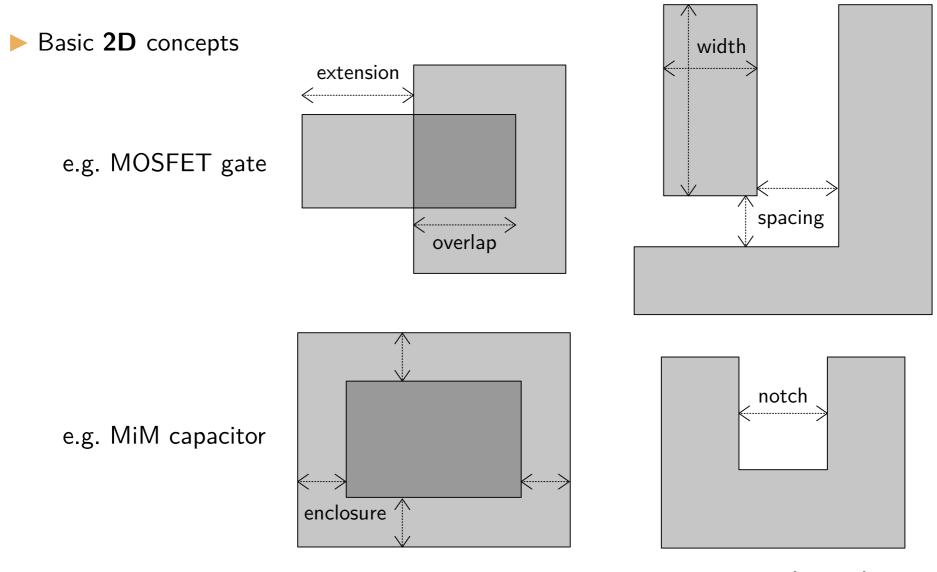

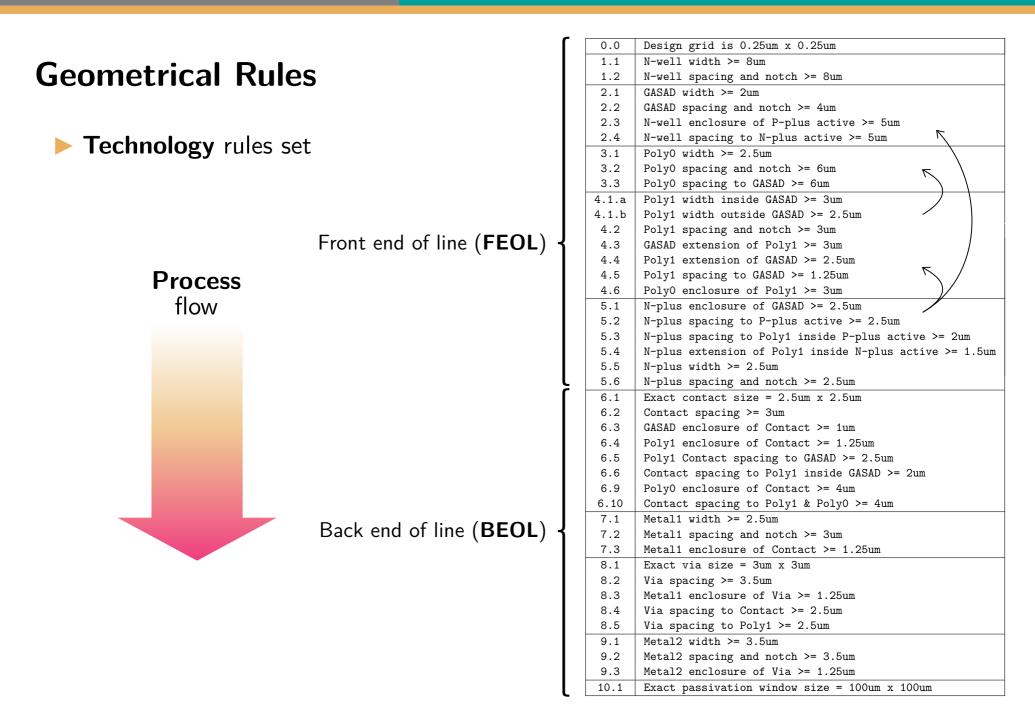

### **Geometrical Rules**

e.g. signal routing

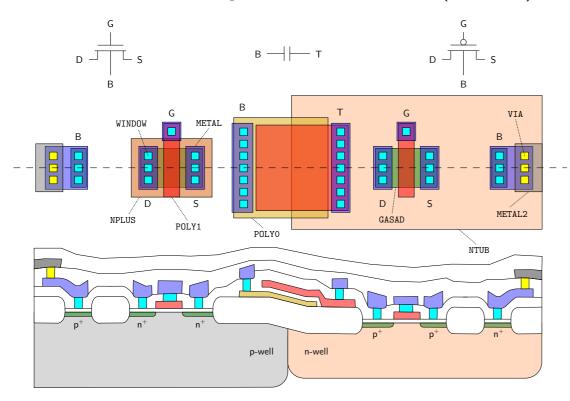

#### **Geometrical Rules**

#### **Technology** rules set

e.g. 2.5um 2P2M CMOS (CNM25)

| 0.0   | Design grid is 0.25um x 0.25um                          |  |  |

|-------|---------------------------------------------------------|--|--|

|       |                                                         |  |  |

| 1.1   | N-well width >= 8um                                     |  |  |

| 1.2   | N-well spacing and notch >= 8um                         |  |  |

| 2.1   | GASAD width >= 2um                                      |  |  |

| 2.2   | GASAD spacing and notch >= 4um                          |  |  |

| 2.3   | N-well enclosure of P-plus active >= 5um                |  |  |

| 2.4   | N-well spacing to N-plus active >= 5um                  |  |  |

| 3.1   | Poly0 width >= 2.5um                                    |  |  |

| 3.2   | PolyO spacing and notch >= 6um                          |  |  |

| 3.3   | PolyO spacing to GASAD >= 6um                           |  |  |

| 4.1.a | Poly1 width inside GASAD >= 3um                         |  |  |

| 4.1.b | Poly1 width outside GASAD >= 2.5um                      |  |  |

| 4.2   | Poly1 spacing and notch >= 3um                          |  |  |

| 4.3   | GASAD extension of Poly1 >= 3um                         |  |  |

| 4.4   | Poly1 extension of GASAD >= 2.5um                       |  |  |

| 4.5   | Poly1 spacing to GASAD >= 1.25um                        |  |  |

| 4.6   | PolyO enclosure of Poly1 >= 3um                         |  |  |

| 5.1   | N-plus enclosure of GASAD >= 2.5um                      |  |  |

| 5.2   | N-plus spacing to P-plus active >= 2.5um                |  |  |

| 5.3   | N-plus spacing to Poly1 inside P-plus active >= 2um     |  |  |

| 5.4   | N-plus extension of Poly1 inside N-plus active >= 1.5um |  |  |

| 5.5   | N-plus width >= 2.5um                                   |  |  |

| 5.6   | N-plus spacing and notch >= 2.5um                       |  |  |

| 6.1   | Exact contact size = 2.5um x 2.5um                      |  |  |

| 6.2   | Contact spacing >= 3um                                  |  |  |

| 6.3   | GASAD enclosure of Contact >= 1um                       |  |  |

| 6.4   | Poly1 enclosure of Contact >= 1.25um                    |  |  |

| 6.5   | Poly1 Contact spacing to GASAD >= 2.5um                 |  |  |

| 6.6   | Contact spacing to Poly1 inside GASAD >= 2um            |  |  |

| 6.9   | PolyO enclosure of Contact >= 4um                       |  |  |

| 6.10  | Contact spacing to Poly1 & Poly0 >= 4um                 |  |  |

| 7.1   | Metal1 width >= 2.5um                                   |  |  |

| 7.2   | Metal1 spacing and notch >= 3um                         |  |  |

| 7.3   | Metal1 enclosure of Contact >= 1.25um                   |  |  |

| 8.1   | Exact via size = 3um x 3um                              |  |  |

| 8.2   | Via spacing >= 3.5um                                    |  |  |

| 8.3   | Metal1 enclosure of Via >= 1.25um                       |  |  |

| 8.4   | Via spacing to Contact >= 2.5um                         |  |  |

| 8.5   | Via spacing to Poly1 >= 2.5um                           |  |  |

| 9.1   | Metal2 width >= 3.5um                                   |  |  |

| 9.2   | Metal2 spacing and notch >= 3.5um                       |  |  |

| 9.3   | Metal2 enclosure of Via >= 1.25um                       |  |  |

| 10.1  | Exact passivation window size = 100um x 100um           |  |  |

#### UAB

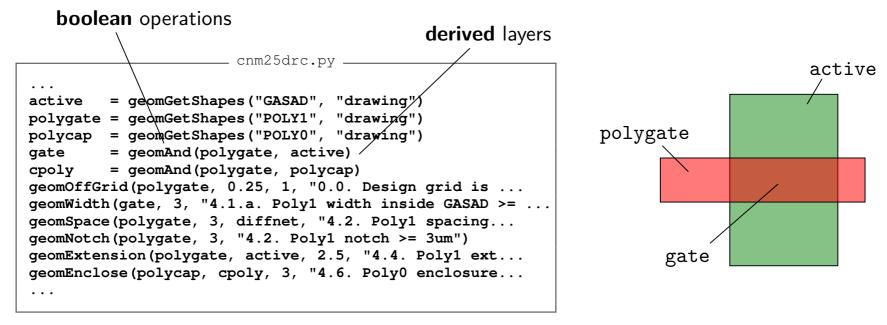

# **Design Rule Checker**

Programming a rules set...

e.g. 2.5um 2P2M CMOS (CNM25)

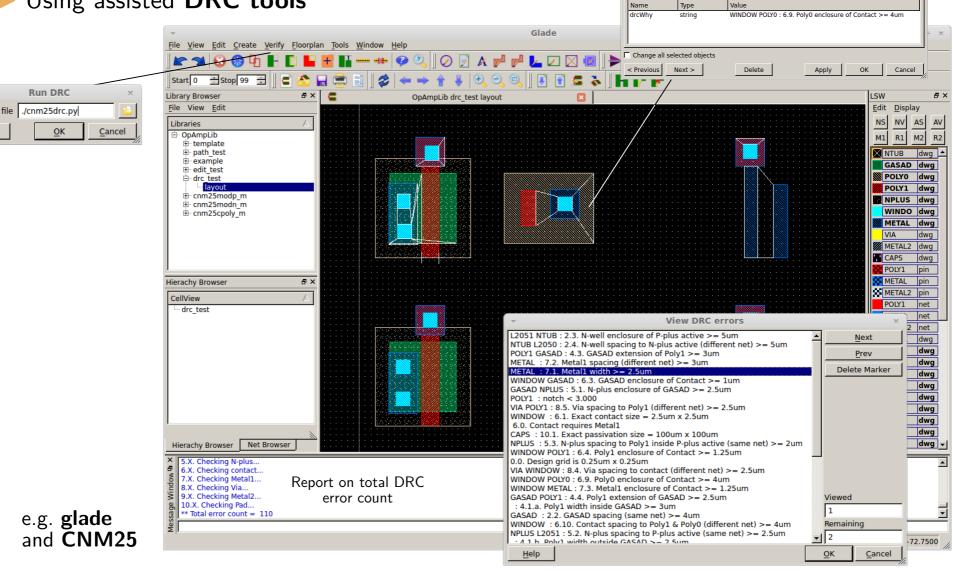

# **Design Rule Checker**

### Using assisted DRC tools

| · •            | Run DRC       | ×              |

|----------------|---------------|----------------|

| DRC rules file | ./cnm25drc.py | 2              |

| <u>H</u> elp   | <u>о</u> к    | <u>C</u> ancel |

Properties for object POLYGON in cell drc\_test view layout

Add

Modify Delete

Properties Polygon

# 1 Device Sizing

- 2 Process and Mismatching Simulation

- 3 The Art of Analog Layout

- 4 Physical Verification

- 5 Parasitics Extraction

### 6 DFM Techniques

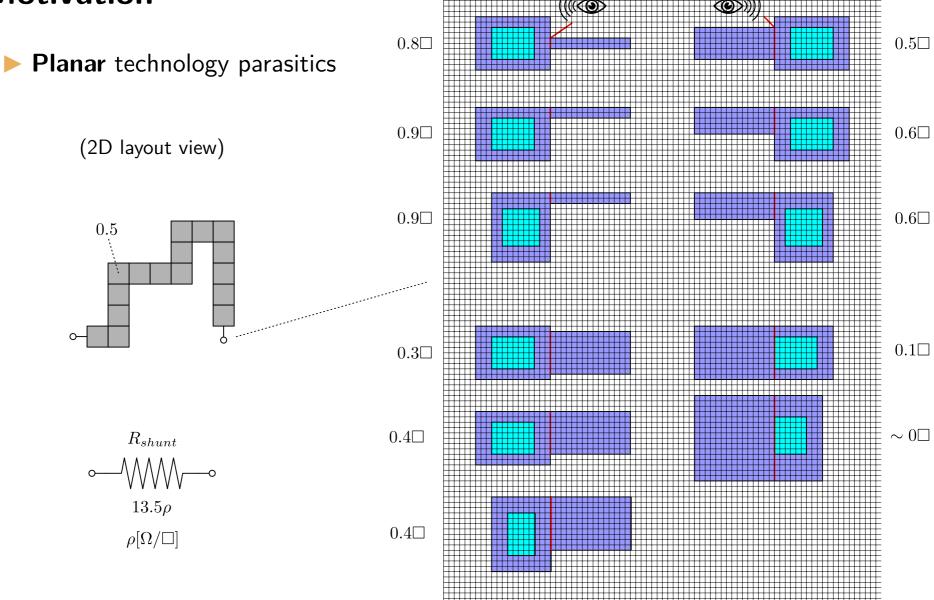

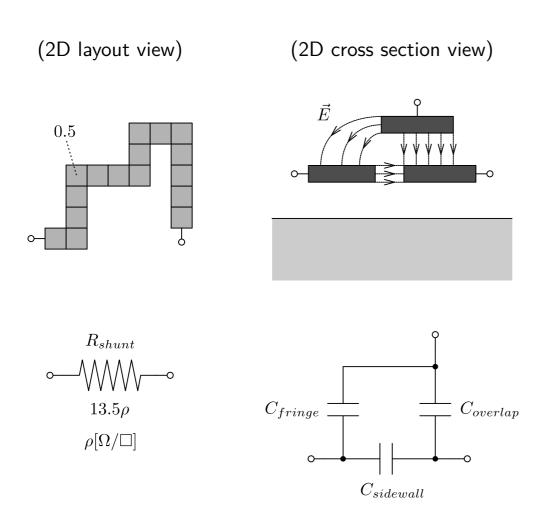

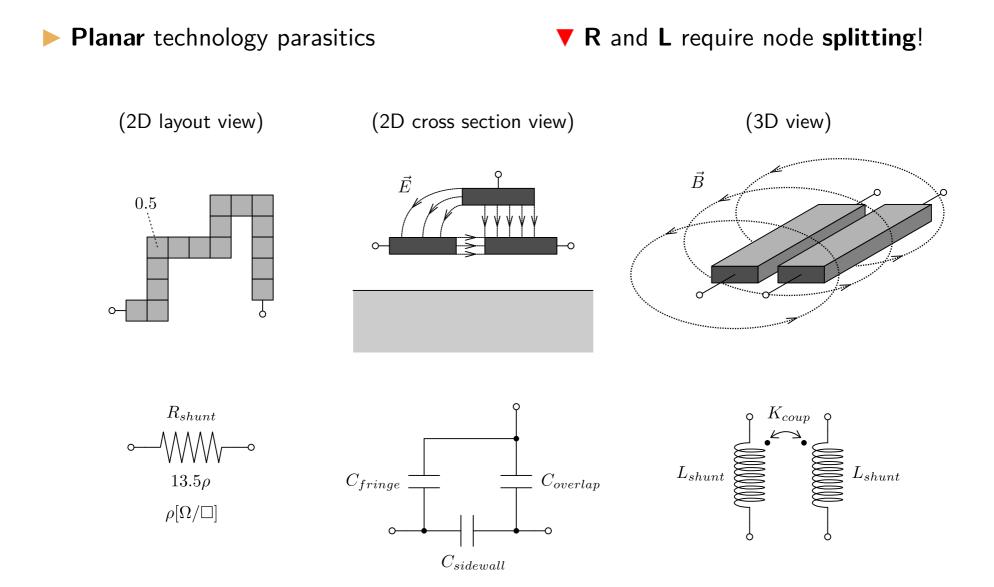

### **Motivation**

### **Motivation**

### **Motivation**

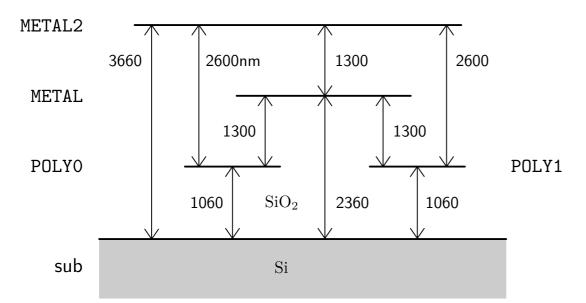

### **Extraction Tools**

Programming a simple rules set for parasitic overlap capacitance only...

```

cnm25xtr.py

...

geomLabel(polygate, "POLY1", "pin", 1)

geomLabel(polygate, "POLY1", "net", 0)

geomConnect([

[cont, ndiff, pdiff, polygate, polycap, metal1],

[via12, metal1, metal2]...])

extractMOS("cnm25modn", ngate, polygate, ndiff, pwell)

extractParasitic3(pdiff, metal2, cmetal2diff, 0,

[metal1, polygate, polycap])

...

```

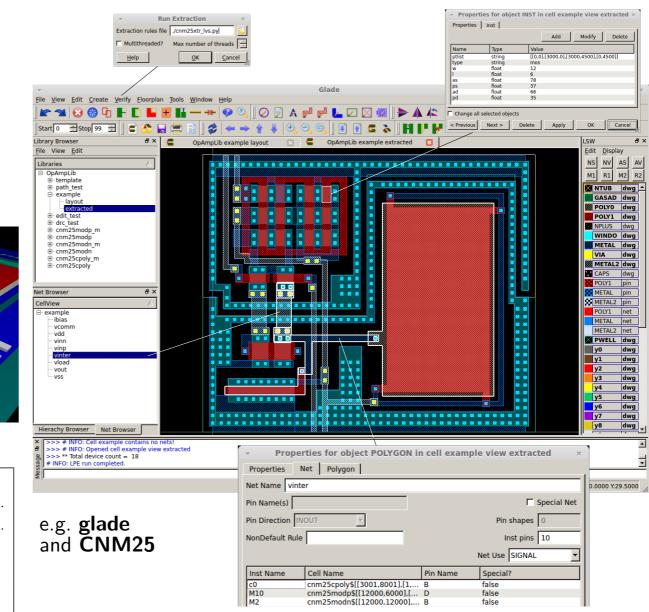

e.g. 2.5um 2P2M CMOS (CNM25)

# **Extraction Tools**

- Programming a simple rules set for parasitic overlap capacitance only...

- Using assisted extraction tools...

opamp\_par.sub .SUBCKT opamp vinn vinp vout vdd vss ibias MM0 vdd ibias vdd vdd cnm25modp w=1.2e-05 l=6e-06 as=... MM1 vdd ibias vout vdd cnm25modp w=1.2e-05 l=6e-06 as=... Cc0 vinter vout cnm25cpoly w=6.42928e-05 l=0.000156207 MM8 vout ibias vdd vdd cnm25modp w=1.2e-05 l=6e-06 as=... ... CP1 vinter vss C=3.8582e-13 CP2 vout ibias C=3.33692e-15 CP3 vinp vss C=1.85938e-15 CP4 vout vcomm C=2.0918e-15 ...

. ENDS

### 1 Device Sizing

- 2 Process and Mismatching Simulation

- 3 The Art of Analog Layout

- 4 Physical Verification

- 5 Parasitics Extraction

### 6 DFM Techniques

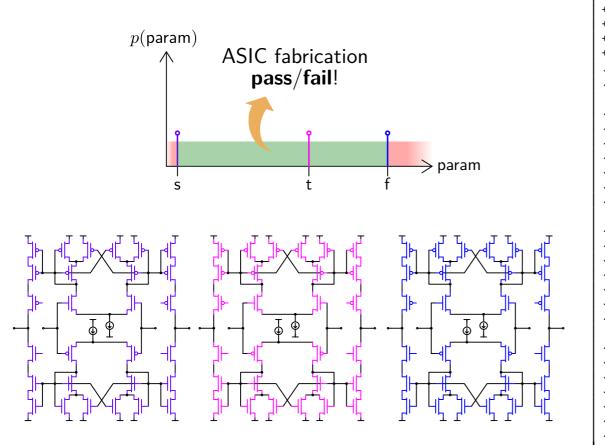

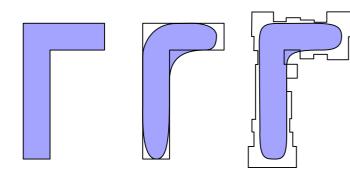

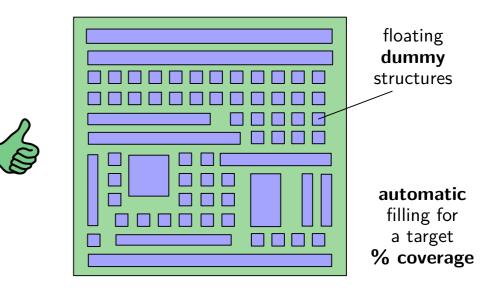

- From few IC prototypes to small and medium series

- Design for manufacturing (DFM) layout rules to increase manufacturing yield

- Some **examples**:

- Dummy filling

52/55

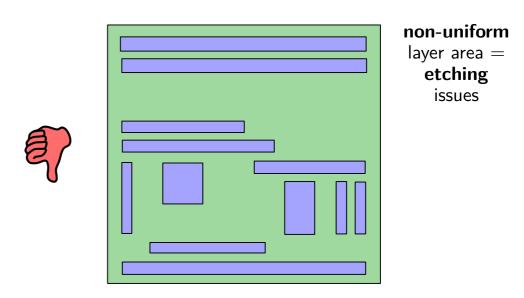

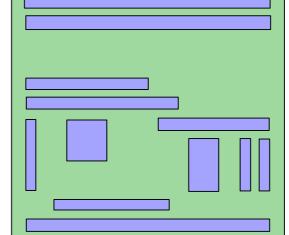

- From few IC prototypes to small and medium series

- Design for manufacturing (DFM) layout rules to increase manufacturing yield

- Some **examples**:

- Dummy filling

non-uniform layer area = etching issues

53/55

Using few shapes also simplifies optical proximity correction (**OPC**)

- From few IC prototypes to small and medium series

- Design for manufacturing (DFM) layout rules to increase manufacturing yield

- Some **examples**:

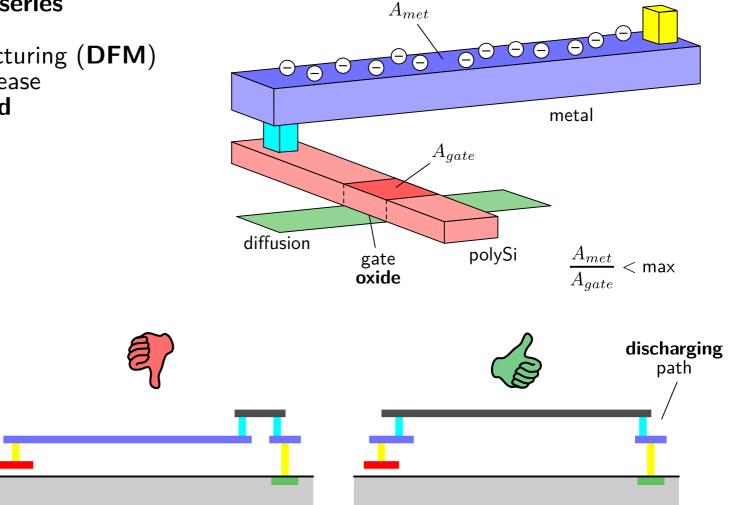

- Dummy filling

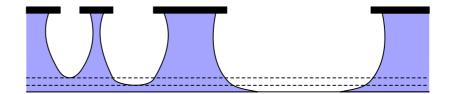

- Antenna reduction

metal2 metal1 polySi diff **charge** stored during metal patterning can **break** thin gate oxide:

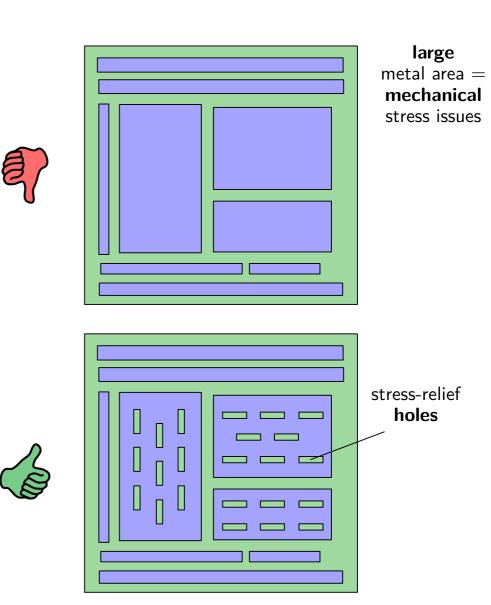

- From few IC prototypes to small and medium series

- Design for manufacturing (DFM) layout rules to increase manufacturing yield

- Some **examples**:

- Dummy filling

- Antenna reduction

- Metal slotting

- Multiple contacts

- Extra guard rings

55/55