# A 6.5-μW 70-dB 0.18-μm CMOS Potentiostatic Delta-Sigma for Electrochemical Sensors

Joan Aymerich, Michele Dei, Lluís Teres and Francisco Serra-Graells joan.aymerich@imb-cnm.csic.es

> Integrated Circuits and Systems (ICAS) Instituto de Microelectrónica de Barcelona, IMB-CNM(CSIC)

> > July 2018

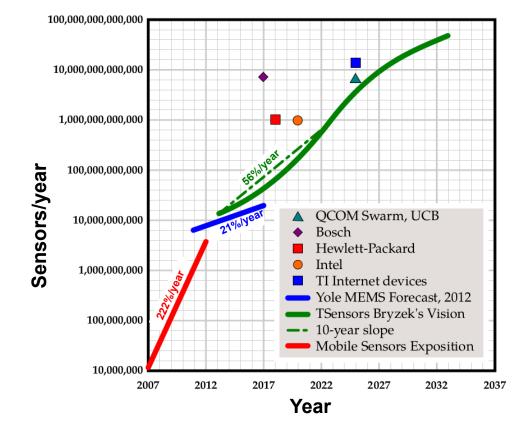

## **Sensors Market Vision**

- Several organizations created visions for continued growth to trillion(s) sensors

- **\$15 trillion by 2022**

- Electrochemical sensors are growing exponentially due to potential of miniaturization and mass production

- Monolithic or hybrid integration onto CMOS platforms

- Applications in biosensors, quality control, ...

CUU

Expected sensor production growth per year www.tsensorssummit.org

## 2 Potentiostatic $\Delta\Sigma$ Modulator architecture

3 Low-Power Circuit Implementation

4 0.18- $\mu m$  CMOS Design Example

## 5 Conclusions

## 2 Potentiostatic $\Delta\Sigma$ Modulator architecture

3 Low-Power Circuit Implementation

4 0.18- $\mu m$  CMOS Design Example

## 5 Conclusions

- ▲ Interaction with microorganisms

- ▲ **Selectivity** by functionalization

- **V** Reduced **speed** and **life** time

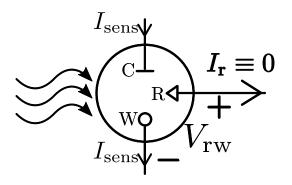

- Potentiostatic and amperometric operations

- Three electrodes:

- Working

- **R**eference

- Counter

GUUS

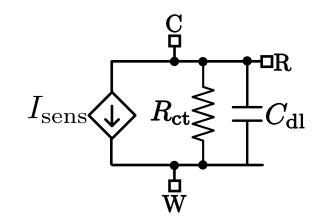

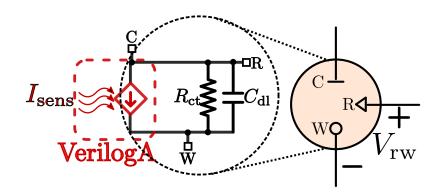

- Measurement independent of the R and C impedances.

- Current associated to the electrons involved in a redox process

$$O + e^- \stackrel{\text{red}}{\underset{\text{ox}}{\longleftarrow}} R$$

Electrochemical time constant:  $\tau_{\rm ch} = R_{\rm ct}C_{\rm dl} \approx 10^{-1}{\rm s}$

Different detection methods are required

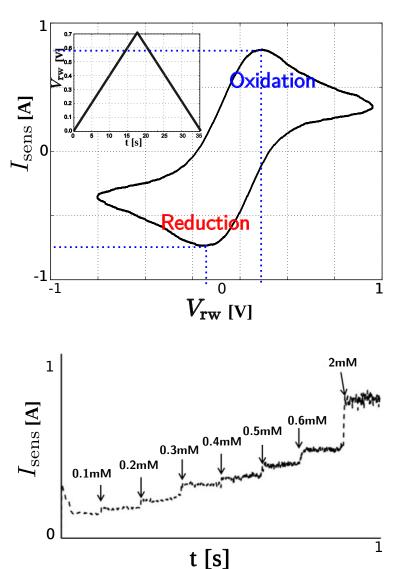

## Cyclic Voltammetry (CV)

- Sensor performance, rapid location of redox potentials, ...

- Sweeping electrode potential  $V_{rw}$  and measuring resulting current  $I_{sens}$

- Potentiostat must sink/source current

### Chronoamperometry (CA)

•  $V_{rw}$  fixed and  $I_{sens}$  monitored as a function of time while concentration is swept

### **کستار السکار کار**

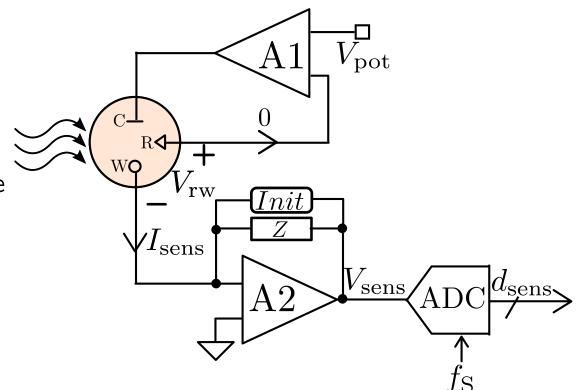

# **Classic circuit implementation**

### Potentiostat

A<sub>1</sub> establishes the control loop to accomplish potentiostat operation

$V_{\rm rw} = V_{\rm pot}$  &  $I_{\rm r} \equiv 0$

### Amperometry

A<sub>2</sub> converts sensor current to voltage for digitization and readout

Requires multiples OpAmps + ADC

Large area and power consumption

## 2 Potentiostatic $\Delta\Sigma$ Modulator architecture

**Composed of Complementation**

4 0.18- $\mu m$  CMOS Design Example

## 8/26

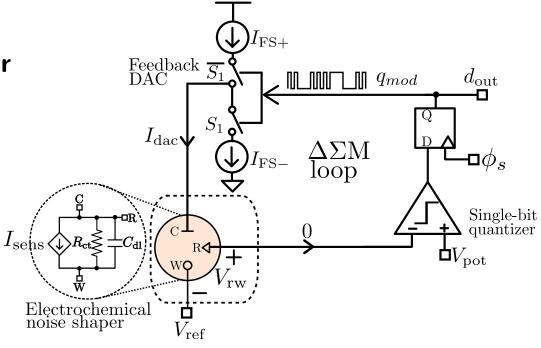

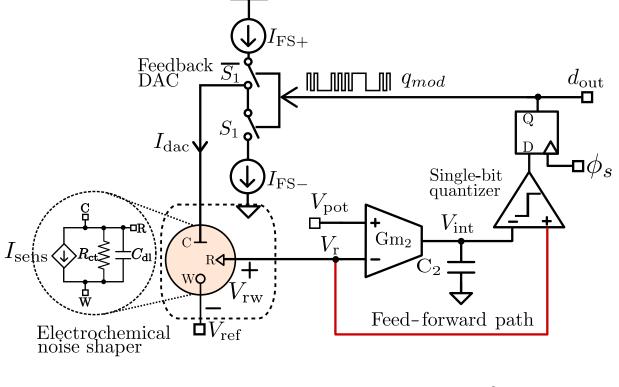

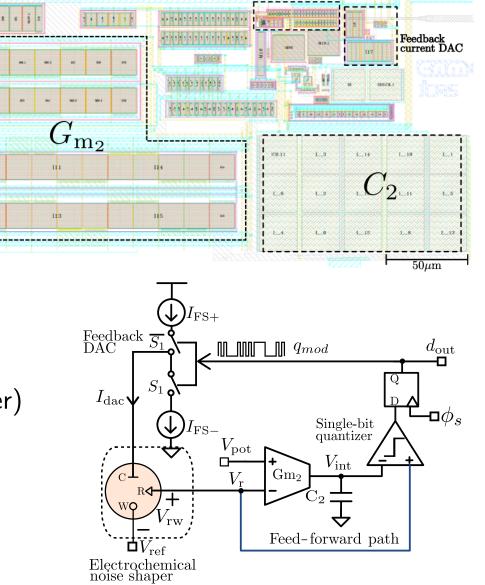

# Potentiostatic $\Delta \Sigma M$

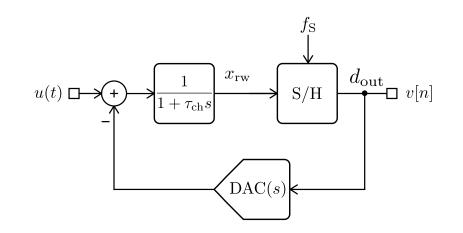

► Behaviour similar to low-pass first-order single-bit CT  $\Sigma\Delta M$  A/D modulator

- Error current converted into voltage and shaped in frequency by the electrochemical sensor itself

- ▲ High oversampling ratios (OSR>100) can be easly obtained with kHz-range clock frequencies f<sub>S</sub>

- Amperometric read-out through the  $\Delta\Sigma$  modulation of output bit stream  $q_{mod}$ by chemical input  $I_{sens}$

CUU

$d_{\rm out}$

$\mathbf{D} \phi_{\mathbf{s}}$

D

$V_{\rm ref}$

$d_{\operatorname{out}}_{\bullet \blacksquare v[n]}$

S/H

Single-bit

quantizer

$V_{\rm int}$

$C_2$

$q_{mod}$

$Gm_2$

$Gm_1$

# From 1<sup>st</sup> order to 2<sup>nd</sup> order $\Delta \Sigma M$

From electrochemical only au to **hybrid/mixed EC/electronic**  $au_{\mathbf{S}}$

Electronic time constant C<sub>2</sub>/Gm<sub>2</sub>

Allows precise potentiostatic operation

**Tones** and pattern noise **suppression**

- Feed-Forward through Gm<sub>1</sub>

- Stabilize the loop

CUUS

[5] J. Aymerich, M. Dei, L. Terés and F. Serra-Graells, "Design of a Low-Power Potentiostatic Second-Order CT Delta-Sigma ADC for Electrochemical Sensors, " 2017 13th Conference on Ph.D. Research in Microelectronics and Electronics (PRIME)

$u(t) \square$

Electrochemical noise shaper

$I_{\rm sehs}$

Feedback  $\overline{S}$

$I_{\rm dac}$

$S_1$

$V_{\rm ref}$

$1 + \tau_{\rm ch} s$

$l_{\rm FS}$

$V_{\rm pot}$

T28

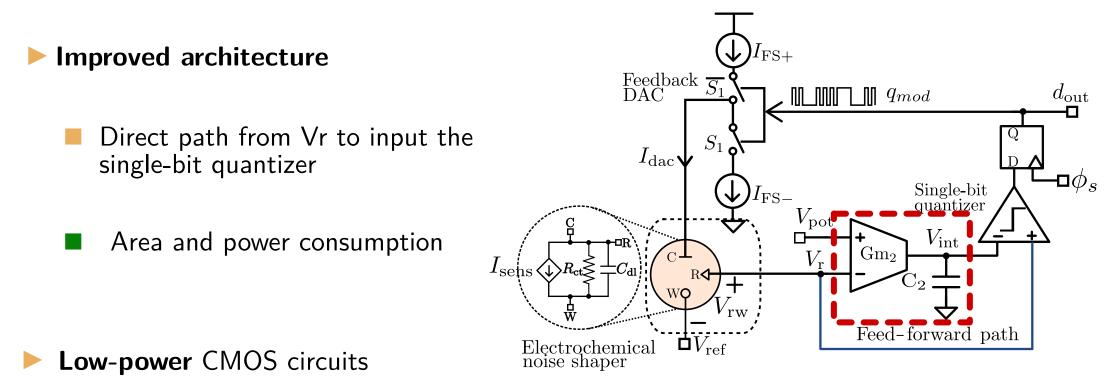

# From 1<sup>st</sup> order to 2<sup>nd</sup> order $\Delta \Sigma M$

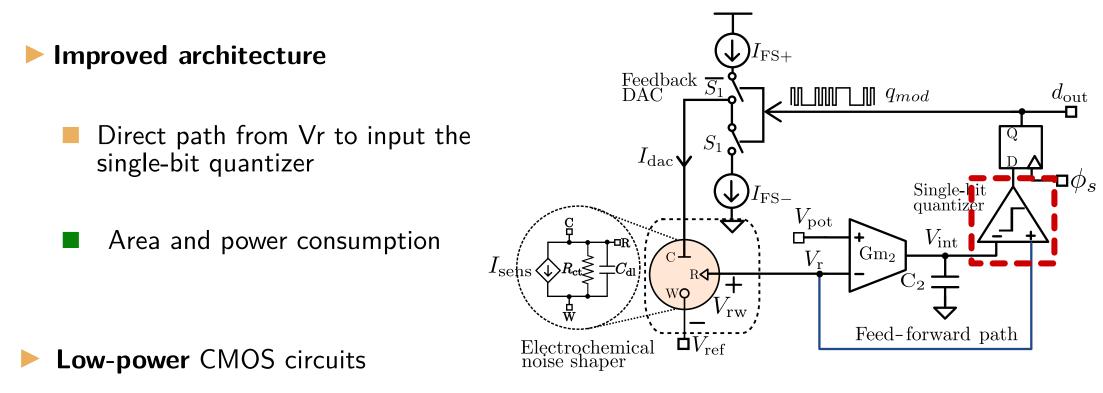

## Improved architecture

- Direct path from Vr to input the single-bit quantizer

- Area and power consumption

Low-power CMOS circuits

- Large flexibility on the selection of potentiostatic voltage

- Wide common-mode voltage range

# 2 Potentiostatic $\Delta \Sigma$ Modulator architecture

3 Low-Power Circuit Implementation

4 0.18- $\mu m$  CMOS Design Example

## 5 Conclusions

# From 1<sup>st</sup> order to 2<sup>nd</sup> order $\Delta \Sigma M$

- **Large flexibility** on the selection of **potentiostatic voltage**.

- Single-bit quantizer: Wide input common-mode voltage range

**Transconductance Gm**<sub>2</sub>: Wide input/output common-mode voltage range

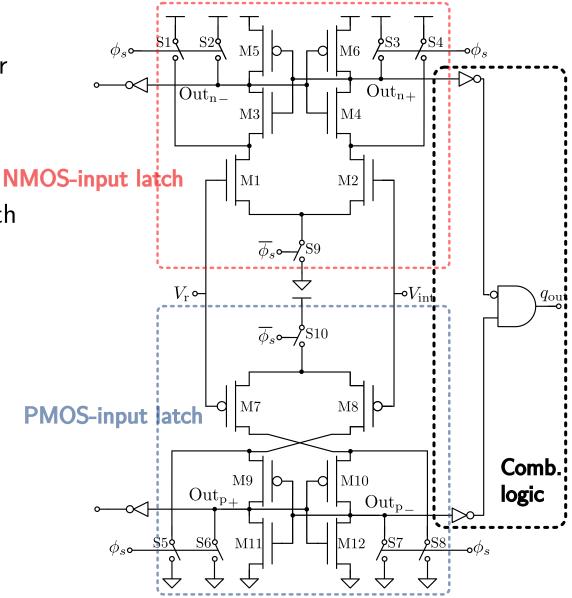

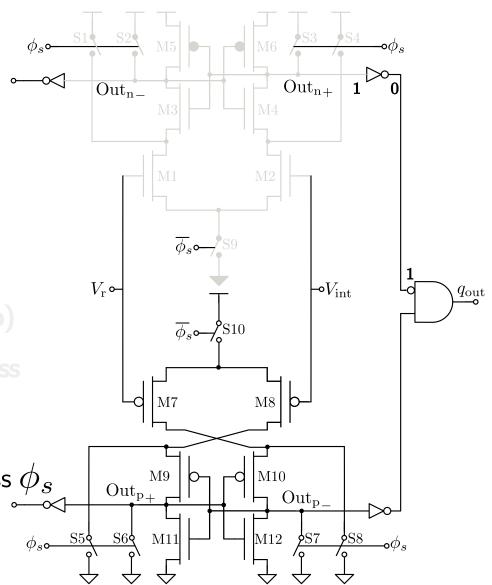

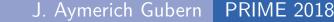

# Single-bit quantizer

- Rail-to-rail complementary latch comparator

- High-input impedance

- Zero-static power consumption

- Combinational logic allows to merge both NMOS-PMOS-input comparators

## 14/26

# Single-bit quantizer

Rail-to-rail complementary latch comparator

- High-input impedance

- Zero-static power consumption

- Combinational logic allows to merge both NMOS-PMOS-input comparators

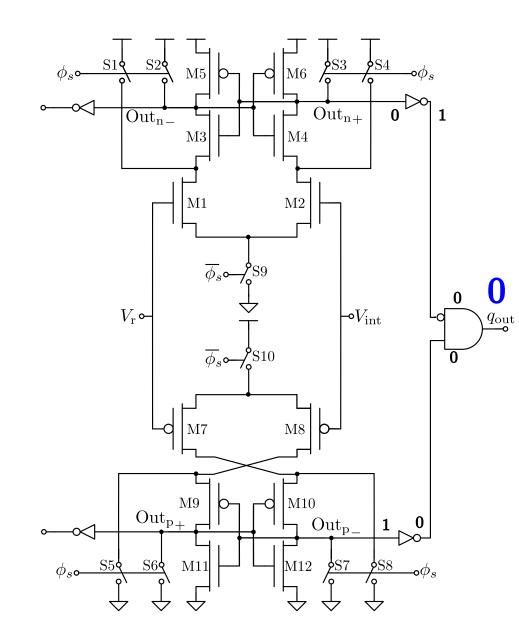

- PMOS OFF: Input common-mode > (Vdd-VTHp)

- lacksquare Outp nodes remain at the negative rail regardless  $\phi_s$

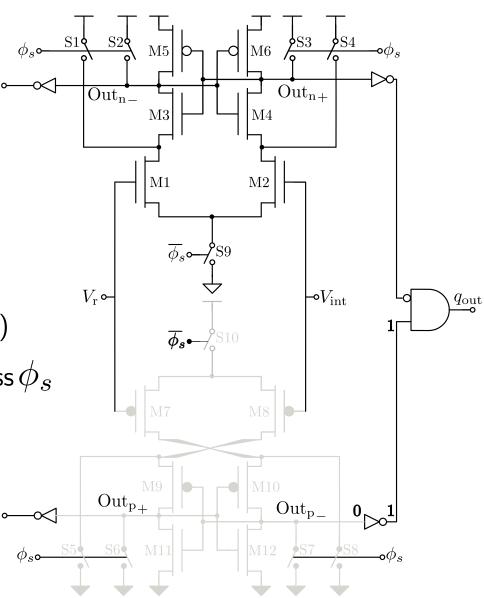

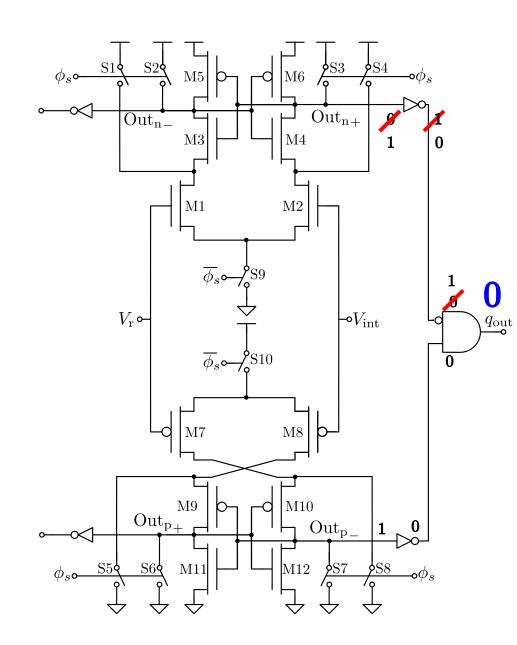

# Single-bit quantizer

Rail-to-rail complementary latch comparator

- High-input impedance

- Zero-static power consumption

- Combinational logic allows to merge both NMOS-PMOS-input comparators

PMOS OFF: Input common-mode > (Vdd-VTHp)

• Outp nodes remain at the negative rail regardless

**NMOS OFF:** Input common-mode < (VTHn)

lacksim Outn nodes remain at the positive rail regardless  $\phi_s$

# From 1st order to 2nd order $\Delta \Sigma M$

Large flexibility on the selection of potentiostatic voltage.

**Single-bit quantizer**: Wide input common-mode voltage range

**Transconductance Gm**<sub>2</sub>: Wide input/output common-mode voltage range

# **Gm-C** Integrator

- **Constant gm** over the input common-mode voltage

- Avoid variations in the electronic integrator time constant

- M1 M4 operated in weak inversion

Sum of the tail currents constant

#### 1:1M6M8 $\forall I_{\text{biasp}}$ M11 $V_{b3}$ M10 $^{M4}V_{r}$ V<sub>pot</sub>o M3 $- V_{int}$ M2 M1 $V_{\text{ref}}$ $V_{b1}$ M5M13 M12 $\overline{\Psi}_{ m biasn}$ $G_{m_2}$ $V_{b2}$ M14M15 $M_{\rm bias}$

### Wide output swing

$2V_{\rm ov} < V_{\rm int} < V_{\rm dd} - 2V_{\rm ov}$   $V_{\rm ov} \longrightarrow Overdrive voltage$

### **CNM®**)CPS

# 2 Potentiostatic $\Delta\Sigma$ Modulator architecture

- 3 Low-Power Circuit Implementation

- 4 0.18- $\mu m$  CMOS Design Example

## 5 Conclusions

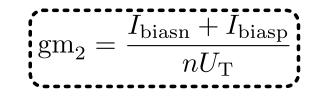

## Low-power 0.18- $\mu m$ CMOS Design

- Layout area: 0.063mm<sup>2</sup>

- Gm-C integrator occupy most of the area

- to minimize offset, i.e potentiostatic error (Vr Vpot)

- slow integrator time constant (sampling frequency @ 1kHz)

### Large Feedback DAC

To minimize low-frequency noise. (DAC noise added directly to the input, it is not shaped by the delta-sigma loop-filter)

Ongoing run XFAB-XH018

on-chip

current source

#### 18/26

### ເກີອາກິ

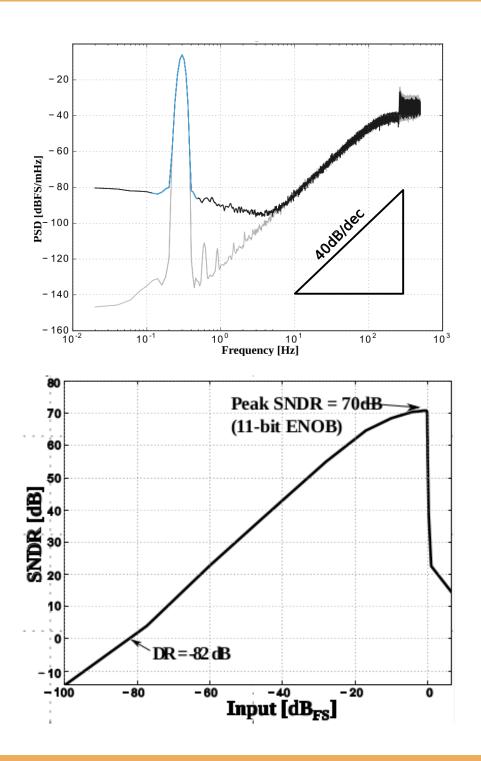

# **Post-Layout Simulations**

### Output spectrum comparison w/ and w/o electronic transient

- $f_S = 1k Hz$

- $\bullet \tau_{\rm ch} = 0.15 \mathrm{s}(OSR \approx 500)$

- $I_{\rm FS} = 1.25 \mu A$

- 70-dB dynamic range for 1.25uA current full scale. (280pA RMS, noise)

- Higher resolution is achievable enlarging the area of the feedback DAC

AREA PENALTY AGAINST DYNAMIC RANGE.

| DAC + bias current<br>Area estimation | Total area increased | SNDR      | ENOB |

|---------------------------------------|----------------------|-----------|------|

| $1400 \mu m^2$                        | —                    | 70 - dB   | 11   |

| $5600 \mu m^2$                        | 7%                   | 75.5 - dB | 12   |

| $22400 \mu m^2$                       | 33%                  | 81 - dB   | 13   |

## ເພື່ອ

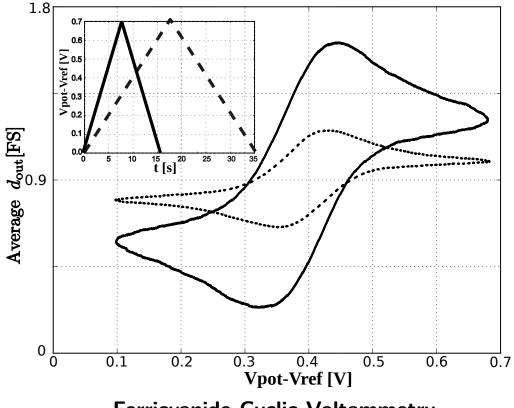

# **Post-Layout Simulations**

Cyclic Voltammetry

- **Triangular waveform** is applied to the reference electrode while the sensor current is measured simultaneously

- **VerilogA model**: Vrw-Isens DC look-up tables based on two experimental measurements of ferricyanide CVs

Ferricyanide Cyclic Voltammetry

### ເພື່ອກູ

# **Simulation Results**

### Performance simulation results

| Parameter                 | Symbol                      | Value                | Unit             |

|---------------------------|-----------------------------|----------------------|------------------|

| Supply voltage            | $V_{\rm DD}$                | 1.8                  | V                |

| Potential range           | $V_{\rm pot} - V_{\rm ref}$ | $\pm 0.7$            | V                |

| Input full scale          | $I_{\rm FS}$                | $\pm 0.2$ to $\pm 2$ | $\mu A$          |

| Oversampling ratio        | OSR                         | 500                  | —                |

| Sampling frequency        | $f_{ m S}$                  | 1                    | $\mathrm{kHz}$   |

| Layout area               | —                           | 0.0063               | $mm^2$           |

| SNDR at $1.25 \mu A_{FS}$ | SNDR                        | 70                   | $^{\mathrm{dB}}$ |

| Power at $2\mu A_{FS}$    | $P_{\mathrm{D}}$            | 6.5                  | $\mu { m W}$     |

**Power consumption** mainly determined by feedback current DAC

$P_{DAC} = 5\mu W$

Rest of circuit blocks  $P_{DAC} = 1.5 \mu W$

## 2 Potentiostatic $\Delta \Sigma$ Modulator architecture

3 Low-Power Circuit Implementation

4 0.18- $\mu m$  CMOS Design Example

## 5 Conclusions

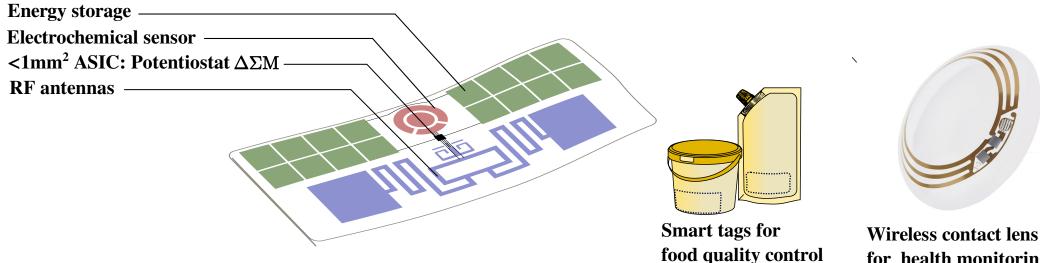

## Conclusions

- **Compact architecture** thanks to the electrode-electrolyte interface used as an integrator stage in the  $\Delta\Sigma$  structure

- Minimalist analog circuits fully integrable in purely digital CMOS technologies

- **High resolution** with kHz-range clock frequencies: SNDR = 70dB@1kHz

- **Low-power**  $(1.5\mu W)$  operation compared to sensor consumption

## **Conclusions**

- **Compact architecture** thanks to the electrode-electrolyte interface used as an integrator stage in the  $\Delta\Sigma$  structure

- **Minimalist** analog circuits fully integrable in purely digital CMOS technologies

- **High resolution** with kHz-range clock frequencies: SNDR = 70 dB@1kHz

- **Low-power (** $1.5\mu$ W**)** operation compared to sensor consumption

## **Future work**

GNM®JCPS

for health monitoring

# Single-bit quantizer

Rail-to-rail complementary latch comparator

- Zero-static power consumption

- Combinational logic allows to merge both NMOS-PMOS-input comparators

- PMOS and NMOS ON

$\blacksquare \mathsf{Vint} > \mathsf{Vr}$

## 10/26

# Single-bit quantizer

Rail-to-rail complementary latch comparator

- Zero-static power consumption

- Combinational logic allows to merge both NMOS-PMOS-input comparators

- PMOS and NMOS ON

Vint > Vr

$\blacksquare \mathsf{Vint} < \mathsf{Vr}$

### ເກີສູ

### 26/26

# Single-bit quantizer

Rail-to-rail complementary latch comparator

- Zero-static power consumption

- Combinational logic allows to merge both NMOS-PMOS-input comparators

- PMOS and NMOS ON

Vint > Vr

$\blacksquare$  Vint < Vr

# **Power Consumption Comparison**

|                    |                      |             |              |             |             | [This work] |

|--------------------|----------------------|-------------|--------------|-------------|-------------|-------------|

| Technology         | 0.18 µm              | 0.5 µm      | 0.13 µm      | 0.18 µm     | 2.5 µm      | 0.18 µm     |

| ADC structure      | Current to frequency | Delta-sigma | Single-Slope | Delta-sigma | Delta-sigma | Delta-sigma |

| Sampling frequency | -                    | 100 kHz     | 1.25 kHz     | -           | 1 kHz       | 1 kHz       |

| FS current         | 150 nA               | 16 µA       | 600 nA       | 1.65 µA     | 2 µA        | 2 µA        |

| Power consumption  | 3 µW                 | 241 µW      | 56 µW        | 920 µW      | 25 µW       | 5 µW        |

| @ supply voltage   | @ 1.2 V              | @ 1.2 V     | @ 2 V        | @ 1.8 V     | @ 5 V       | @ 1.8 V     |

|                    |                      |             |              |             |             |             |