# Design of a Low-Power Potentiostatic Second-Order CT Delta-Sigma ADC for Electrochemical Sensors

Joan Aymerich Gubern joan.aymerich@imb-cnm.csic.es

Integrated Circuits and Systems (ICAS) Instituto de Microelectrónica de Barcelona, IMB-CNM(CSIC)

June 2017

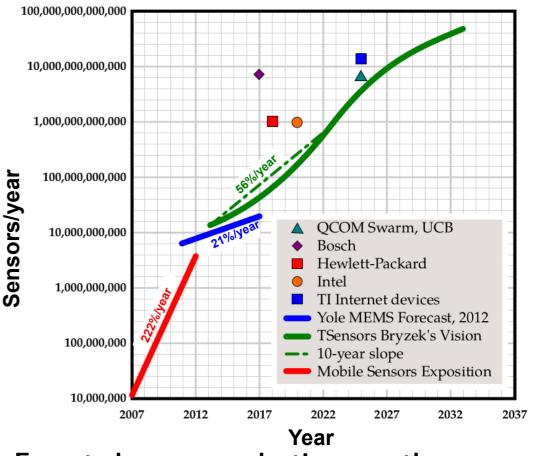

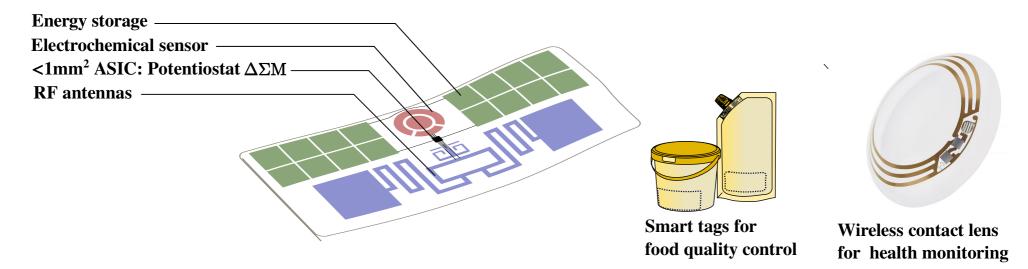

### **Trillion-Sensor Vision**

- Several organizations created visions for continued growth to trillion(s) sensors

- **\$15 trillion by 2022**

- Electrochemical sensors are growing exponentially due to potential of miniaturization and mass production

- Monolithic or hybrid integration onto CMOS platforms

- Applications in biosensors, quality control, ...

Expected sensor production growth per year

www.tsensorssummit.org

#### ເພື່ອງເບີຍ

### **2** Potentiostatic $\Delta\Sigma$ Modulator architecture

3 Proposed architecture

4 Design methodology and trade-offs

### 5 Conclusions

ເພື່ອງເພ

1 Amperometric Electrochemical Sensors

### 2 Potentiostatic $\Delta\Sigma$ Modulator architecture

3 Proposed architecture

4 Design methodology and trade-offs

### 5 Conclusions

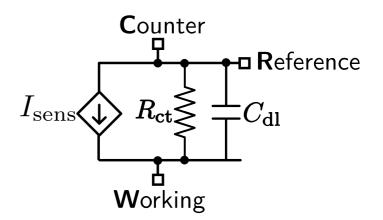

### **Amperometric Electrochemical Sensors**

- ▲ Interaction with microorganisms

- ▲ **Selectivity** by functionalization

- Reduced speed and life time

- Potentiostatic and amperometric operations

- **Three electrodes:**

- Working

Reference

Counter

- Measurement independent of the R and C impedances.

- Electrochemical time constant:  $\tau_{\rm ch} = R_{\rm ct}C_{\rm dl} \approx 10^{-1}{\rm s}$

- **Rct** = charge-transfer resistance

- CdI = double-layer capacitance

#### ເພ

#### J. Aymerich Gubern PRIME 2017

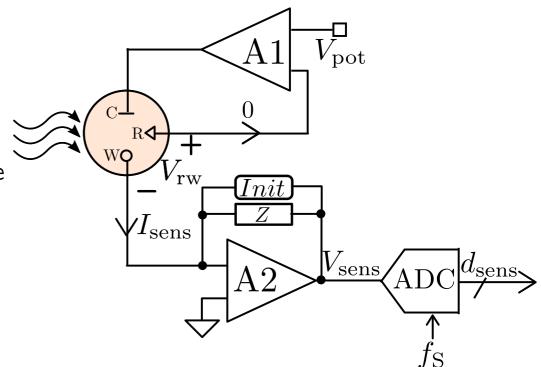

### **Classic circuit implementation**

#### Potentiostat

A<sub>1</sub> establishes the control loop to accomplish potentiostat operation

$V_{

m rw}=V_{

m pot}$  &  $I_{

m r}\equiv 0$

#### Amperometry

A<sub>2</sub> converts sensor current to voltage for digitization and readout

Requires multiples OpAmps + ADC

Large area and power consumption

### 2 Potentiostatic $\Delta\Sigma$ Modulator architecture

3 Proposed architecture

4 Design methodology and trade-offs

### 5 Conclusions

J. Aymerich Gubern PRIME 2017

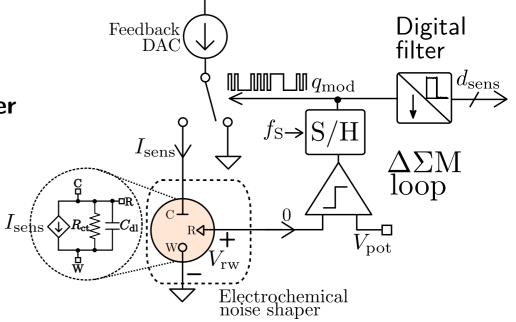

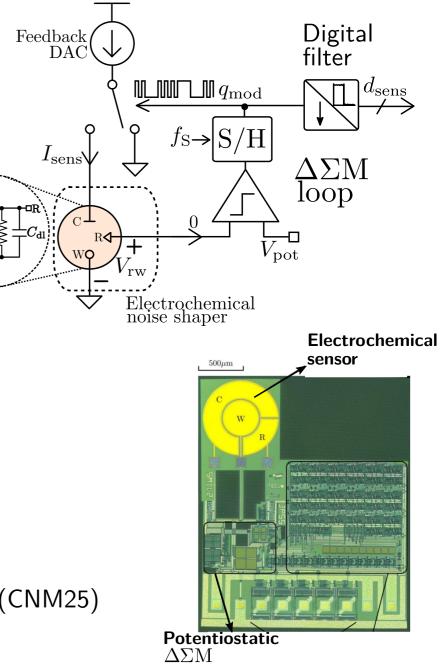

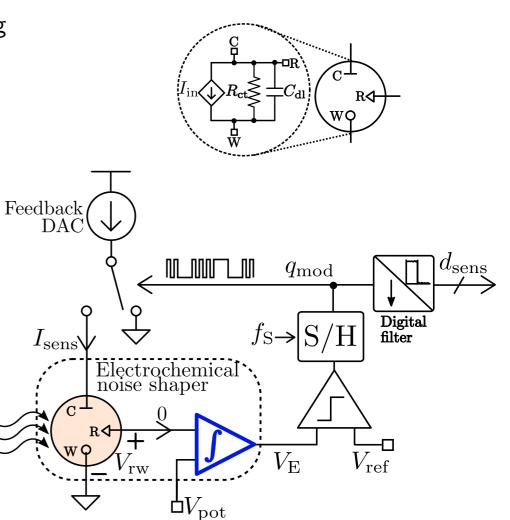

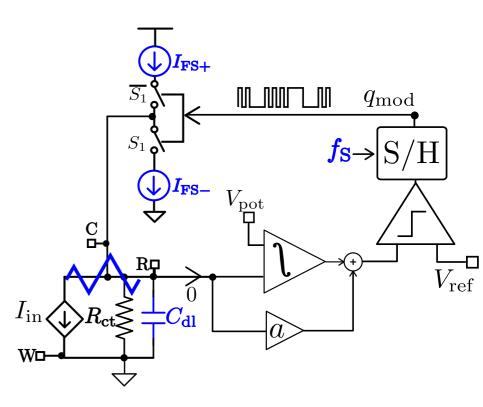

## Potentiostatic $\Delta \Sigma M$

- ▶ Behaviour similar to low-pass first-order single-bit CT  $\Sigma\Delta M$  A/D modulator

- Error current converted into voltage and shaped in frequency by the electrochemical sensor itself

- ▲ High oversampling ratios (OSR>100) can be easly obtained with kHz-range clock frequencies f<sub>S</sub>

- Amperometric read-out through the  $\Delta\Sigma$ modulation of output bit stream  $q_{\rm mod}$ by chemical input  $I_{\rm sens}$

## Potentiostatic $\Delta \Sigma M$

- ▶ Behaviour similar to low-pass first-order single-bit CT  $\Sigma\Delta M$  A/D modulator

- Error current converted into voltage and shaped in frequency by the electrochemical sensor itself

- ▲ High oversampling ratios (OSR>100) can be easly obtained with kHz-range clock frequencies f<sub>S</sub>

- Amperometric read-out through the  $\Delta\Sigma$ modulation of output bit stream  $q_{\rm mod}$ by chemical input  $I_{\rm sens}$

Monolithic CMOS integration Inexpensive 2.5µm in-house CMOS technology (CNM25) developed by ICAS group at IMB-CNM(CSIC)

#### ເດີຍເອີ

$I_{\rm sehs}$

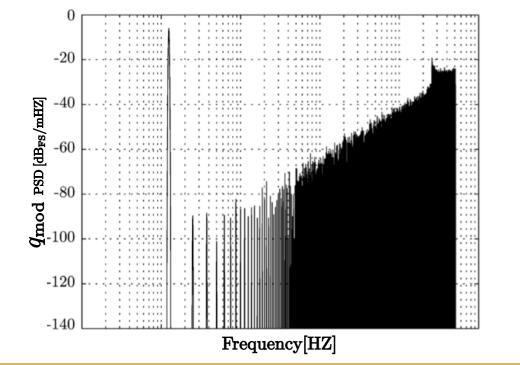

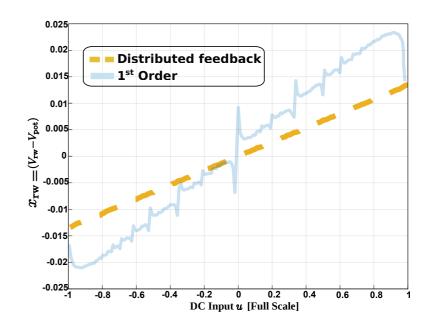

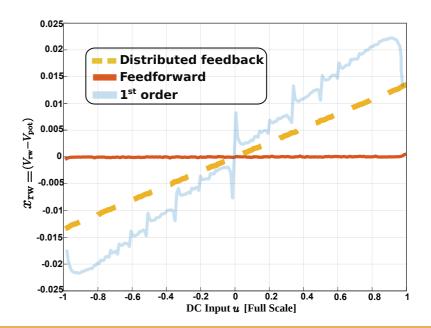

## Potentiostatic $\Delta \Sigma M$

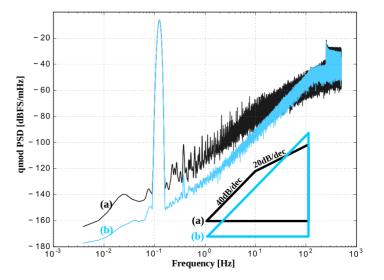

**v** Typical **tonal component** of  $1^{\text{st}}$  order  $\Delta \Sigma M$

- Quantization error and input signal correlation

- Potentiostat operation not well-defined

Potentiostatic error  $\mathcal{X}_{rw}$  influenced by the input signal

#### ເກີ

1 Amperometric Electrochemical Sensors

### **2** Potentiostatic $\Delta \Sigma$ Modulator architecture

### 3 Proposed architecture

4 Design methodology and trade-offs

### 5 Conclusions

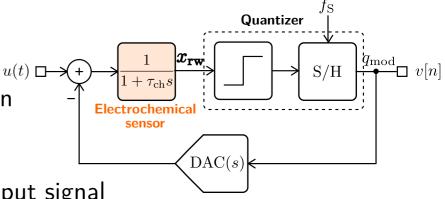

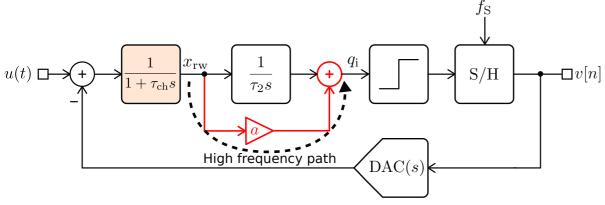

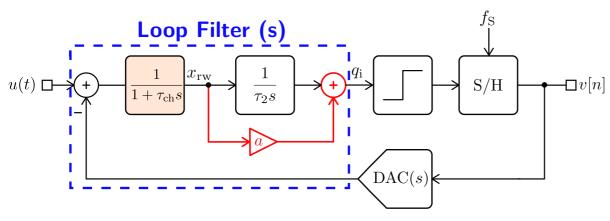

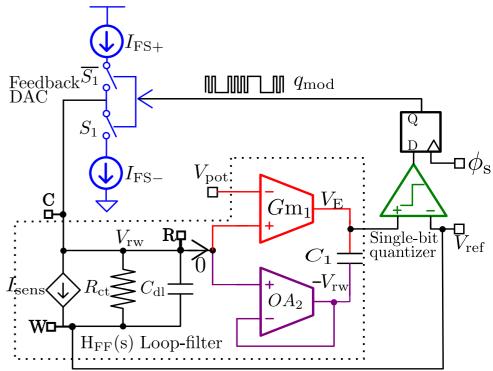

### Proposed amperometric potentiostatic $\Sigma\Delta M$

Incremental work: Addition of electronic integration

▲ **Higher resolution:** 2<sup>nd</sup> order noise shaping

- ▲ Idle tones attenuation

- ▲ Potentiostatic operation well-defined ■ Electronic integrator forces  $V_{rw} = V_{pot}$

▼ New design trade-offs!

- **Stability compensation** is required

- A zero must be added in the loop filter to compensate the phase shift

#### 12/26

#### COM JUS

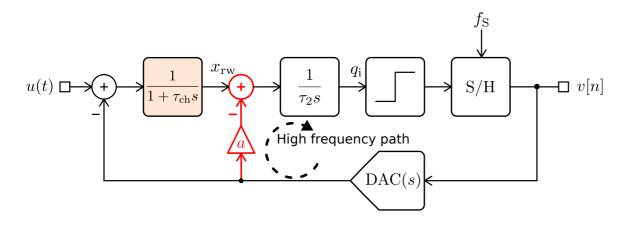

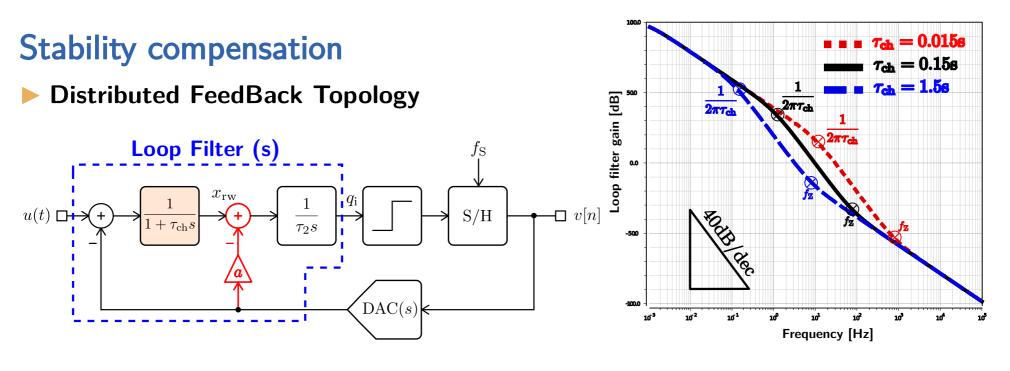

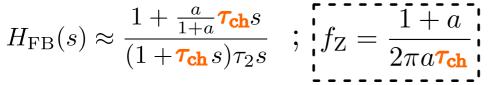

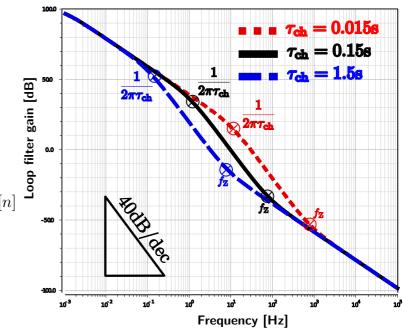

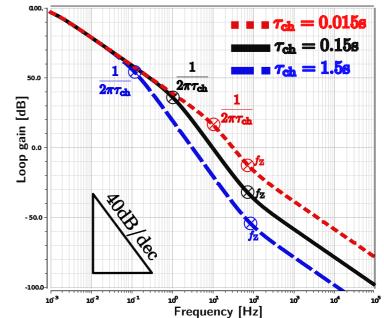

### Distributed FeedBack Topology

Loop Filter Zero frequency location

$$H_{\rm FB}(s) \approx \frac{1 + \frac{a}{1+a} \boldsymbol{\tau_{\rm ch}} s}{(1 + \boldsymbol{\tau_{\rm ch}} s) \boldsymbol{\tau_2} s} \quad ; \quad f_{\rm Z} = \frac{1+a}{2\pi a \boldsymbol{\tau_{\rm ch}}}$$

Loop Filter Zero frequency location

$$H_{\rm FB}(s) \approx \frac{1 + \frac{a}{1+a} \boldsymbol{\tau_{\rm ch}} s}{(1 + \boldsymbol{\tau_{\rm ch}} s) \tau_2 s} \quad ; \quad f_{\rm Z} = \frac{1+a}{2\pi a \boldsymbol{\tau_{\rm ch}}}$$

▼  $f_Z$  depends on sensor time constant  $\tau_{ch}$ ■  $\downarrow \tau_{ch} \rightarrow \uparrow f_Z$  Leading to instability!!

#### Loop Filter Zero frequency location

▼  $f_Z$  depends on sensor time constant  $\tau_{ch}$ ■  $\downarrow \tau_{ch} \rightarrow \uparrow f_Z$  Leading to unstability!!

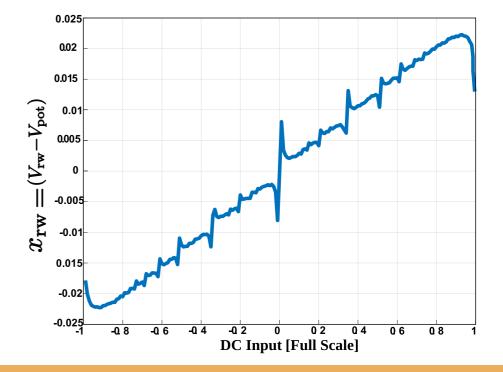

Potentiostatic voltage strongly influenced by the sensor input signal

$x_{\rm rw} = a_{\rm fb}$

#### ເດັກສູອ ກໍ່ເກັນ

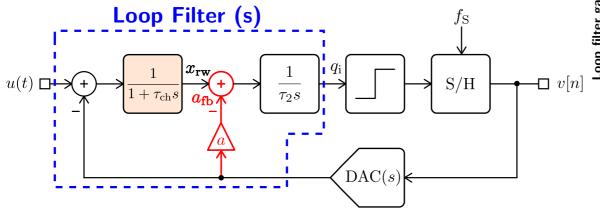

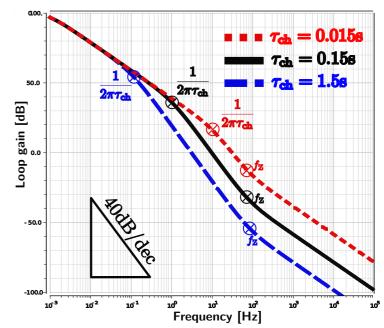

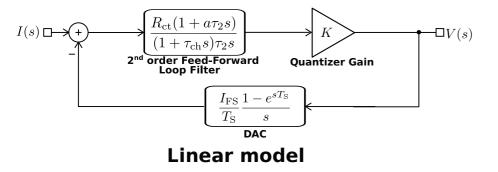

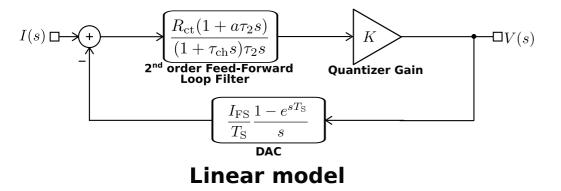

### Feed-Forward Topology

#### Loop Filter Zero frequency location

$$H_{\rm FF}(s) = \frac{1 + a\tau_2 s}{(1 + \tau_{\rm ch} s)\tau_2 s}; \quad f_{\rm Z} = \frac{1}{2\pi a\tau_2}$$

Variations in the sensor time constant do not compromise the stability of the system!

### Feed-Forward Topology

Loop Filter Zero frequency location

$$H_{\rm FF}(s) = \frac{1 + a\tau_2 s}{(1 + \tau_{\rm ch} s)\tau_2 s}; \quad f_{\rm Z} = \frac{1}{2\pi a\tau_2}$$

- Variations in the sensor time constant do not compromise the stability of the system!

- **Electronic integrator forces** its input  $x_{rw}$  to have **DC zero component**.

#### ເກີອາວັເກີອ

1 Amperometric Electrochemical Sensors

2 Potentiostatic  $\Delta \Sigma$  Modulator architecture

3 Proposed architecture

4 Design methodology and trade-offs

### 5 Conclusions

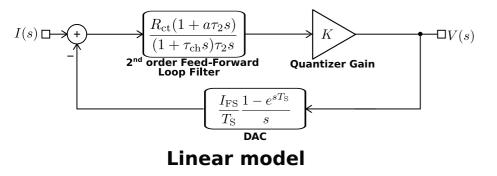

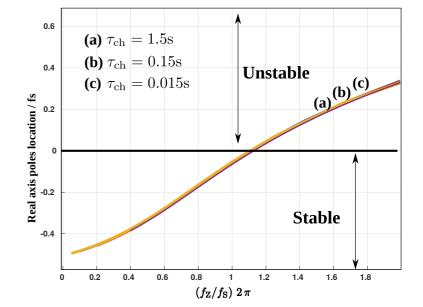

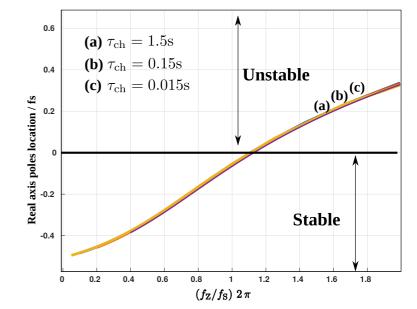

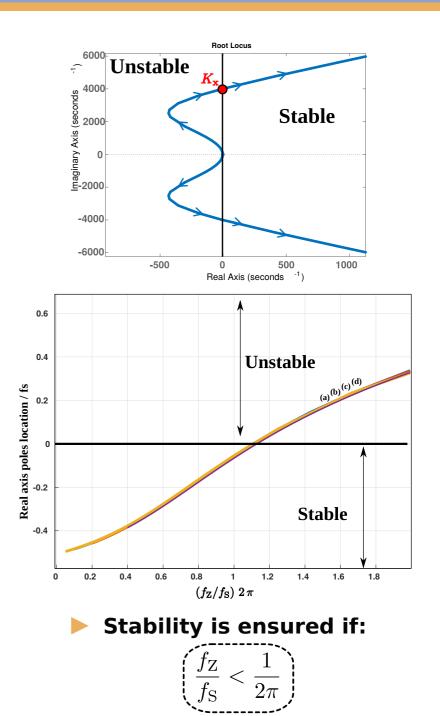

#### Linear model

- Stability region as a function of f<sub>z</sub>/f<sub>s</sub>

- **Root locus** analysis: Closed-loop poles moves as quantizer gain changes

- Stability condition:  $f_{

m Z} < f_{

m S}/(2\pi)$

### **Small-Signal Stability Analysis**

#### Linear model

- Stability region as a function of f<sub>z</sub>/f<sub>s</sub>

- **Root locus** analysis: Closed-loop poles moves as quantizer gain changes

- Stability condition:  $f_{

m Z} < f_{

m S}/(2\pi)$

- Power Spectrum as function of zero location

- More stable (More 1<sup>st</sup> order behaviour) Less aggressive noise shaping

- Less safety stability margin Better noise shaping

#### ເກີອາເປັນ

J. Aymerich Gubern PRIME 2017

## Potentiostat Voltage Ripple

- Voltage ripple may be required to be kept below certain minimum

- Feedback current DAC (I<sub>FS</sub>) charges/discharges Cdl

- T<sub>s</sub> is the only degree of freedom to minimize ripple

- **(** $C_{dI}$  and **I**<sub>FS</sub> are fixed by the application)

$$\frac{\Delta V_{\rm rw}}{V_{\rm rw}} \propto \frac{I_{\rm FS} T_S / C_{\rm dl}}{I_{\rm FS} R_{\rm ct}} = \frac{T_{\rm S}}{\tau_1}$$

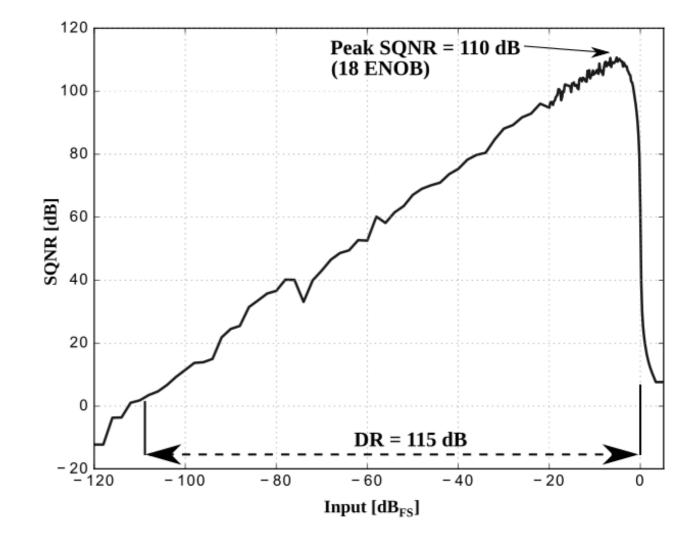

### SQNR vs input signal

Top-level simulation

$f_S = 1k \text{Hz}$

- $\bullet \tau_{\rm ch} = 0.15 \mathrm{s}(OSR \approx 500)$

- $f_{\rm Z}/f_{\rm S} = 1/(4\pi)$

$I_{\rm FS} = 2\mu A$

### Low-power circuit implementation

- Flexible and modular to be mapped into different CMOS technologies

- Electronic integrator: Gm<sub>1</sub>-C<sub>1</sub>

- Feed-Forward path

- Latch comparator for 1-bit quantization

- **D-type flip-flop** for S/H

- Feedback current DAC

- Power consumption mainly determined by current DAC FS, allowing chemical reaction take place

#### ເກີ

### **Simulation Results**

#### Performance simulation results

Power consumption mainly determined by current DAC FS  $P_{DAC} = 4.7 \mu W$

Rest of circuit blocks P = 370 nW

#### 0.18µm CMOS technology

| Parameter                | Symbol                      | Value     | Unit             |

|--------------------------|-----------------------------|-----------|------------------|

| Supply voltage           | $V_{\rm DD}$                | 1.8       | V                |

| Potential range          | $V_{\rm pot} - V_{\rm ref}$ | $\pm 0.7$ | V                |

| Input full scale         | $I_{\rm FS}$                | $\pm 2$   | $\mu \mathrm{A}$ |

| Oversampling ratio       | OSR                         | 500       | —                |

| Sampling frequency       | $f_{ m S}$                  | 1         | m kHz            |

| Loop-filer zero location | $f_{\rm Z}/f_{ m S}$        | $1/\pi$   | _                |

| Potentiostatic ripple    | $\Delta V_{ m rw}$          | 11.6      | mVrms            |

| Power at $2\mu A_{FS}$   | $P_{\mathrm{D}}$            | 5.1       | $\mu W$          |

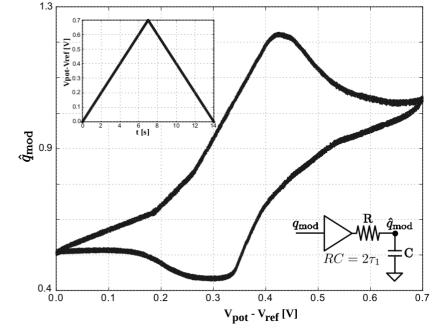

#### Cyclic Voltammetry

- Method for studying electrochemical reactions

- Triangular waveform is applied to the Reference-electrode, while the sensor current is measured simultaneously.

- VerilogA model

Ferrocyanide Cyclic Voltammetry

1 Amperometric Electrochemical Sensors

### 2 Potentiostatic $\Delta \Sigma$ Modulator architecture

3 Proposed architecture

4 Design methodology and trade-offs

### 5 Conclusions

### Conclusions

- **Compact architecture** thanks to the electrode-electrolyte interface used as an integrator stage in the  $\Delta\Sigma$  structure

- Minimalist analog circuits fully integrable in purely digital CMOS technologies

- **High resolution** with kHz-range clock frequencies: SQNR = 110dB @ 1kHz

- $\triangleright$  Ultra low-power (370nW) operation compared to sensor consumption

### Conclusions

- **Compact architecture** thanks to the electrode-electrolyte interface used as an integrator stage in the  $\Delta\Sigma$  structure

- **Minimalist** analog circuits fully integrable in purely digital CMOS technologies

- **High resolution** with kHz-range clock frequencies: SQNR = 110dB @ 1kHz

- **Ultra low-power (**370nW**)** operation compared to sensor consumption

### **Future work**

### **Power Consumption Comparison**

| Technology         | 0.18 µm              | 0.5 µm      | 0.13 µm      | 0.18 µm        | 2.5 µm      | 0.18 µm     |  |

|--------------------|----------------------|-------------|--------------|----------------|-------------|-------------|--|

| ADC structure      | Current to frequency | Delta-sigma | Single-Slope | Delta-sigma    | Delta-sigma | Delta-sigma |  |

| Sampling frequency | -                    | 100 kHz     | 1.25 kHz     | -              | 1 kHz       | 1 kHz       |  |

| FS current         | 150 nA               | 16 µA       | 600 nA       | <b>1.65 μA</b> | 2 μΑ        | 2 µA        |  |

| Power consumption  | 3 µW                 | 241 µW      | 56 µW        | 920 μW         | 25 µW       | 5 µW        |  |

| @ supply voltage   | @ 1.2 V              | @ 1.2 V     | @ 2 V        | @ 1.8 V        | @ 5 V       | @ 1.8 V     |  |

|                    |                      |             |              |                |             |             |  |

[This work]

### **Small-Signal Stability Analysis**

Linear model

#### Root Locus

- Stability region as a function of K

- Worst-case scenario when K is maximum

#### From stable situation

Sweep input: 0 to FS to find maximum quantizer gain Kmax (worst-case)

#### Stability region as a function of f<sub>z</sub>/f<sub>s</sub>

Sweep  $f_S/f_Z$  and check if Kmax is within the stable region

#### ເພື່ອກູ