# Class-AB Single-Stage OpAmp for Low-Power Switched-Capacitor Circuits

CSIC **Gun ()** juis S. Sutula<sup>1</sup>, M. Dei<sup>1</sup>, L. Terés<sup>1,2</sup> and F. Serra-Graells<sup>1,2</sup>

<sup>1</sup>Integrated Circuits and Systems Group, IMB–CNM(CSIC) <sup>2</sup>Dept. of Microelectronics and Electronic Systems stepan.sutula@imb-cnm.csic.es

Universitat Autònoma de Barcelona

#### Abstract

A new family of Class-AB OpAmp circuits based on single-stage topologies with non-linear current amplifiers is presented. The proposed architecture is characterized by generating all Class-AB current in the output transistors only. It exhibits low sensitivity to technology parameter variations and avoids the need for internal frequency compensation. It is suitable for low-power switched-capacitor circuits and optimized for a fast on-off operation and multi-decade load-capacitance specifications. A complete OpAmp design example is integrated in a standard 0.18-µm 1P6M CMOS technology. Compared to the MOS-only state-of-the-art Class-AB OpAmps, the presented architecture obtains the highest figure of merit.

Architecture

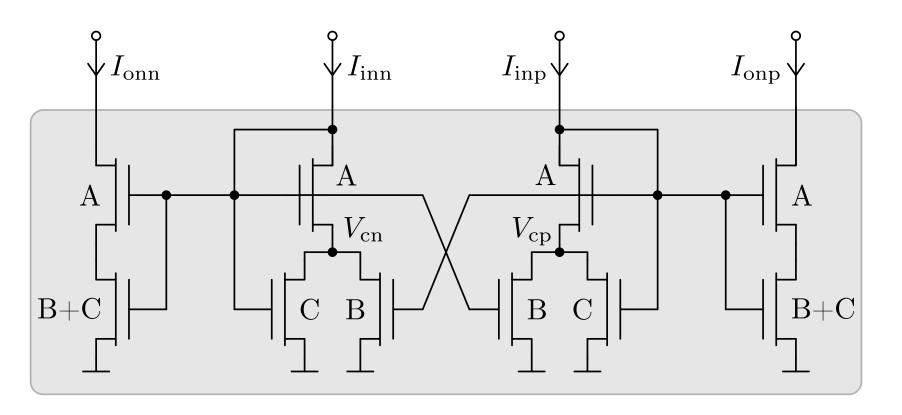

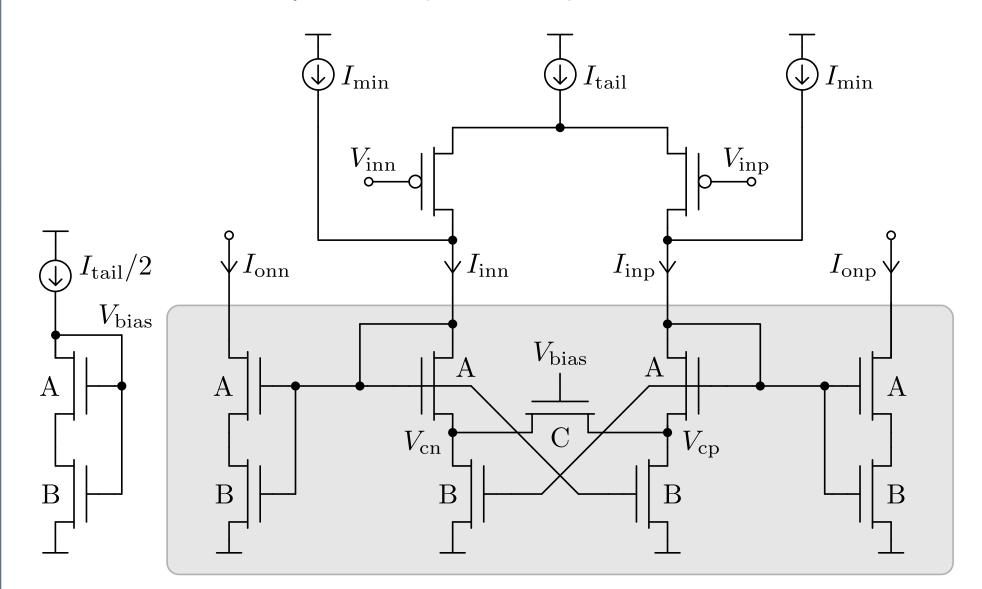

### **Type-II** Circuit

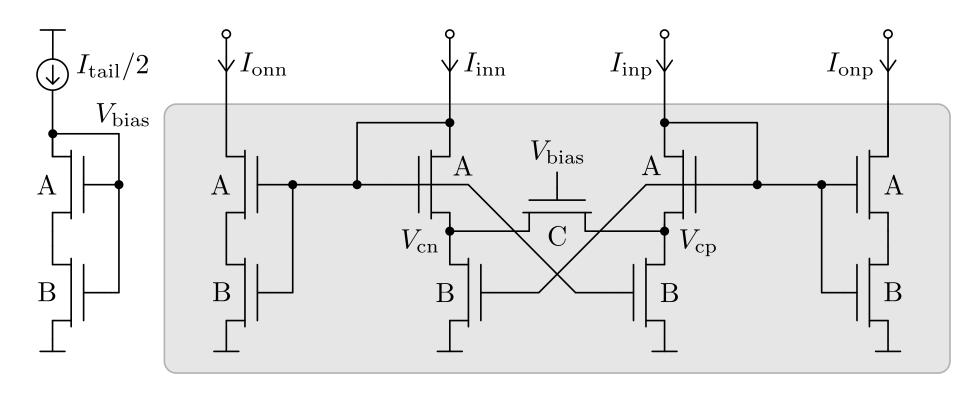

Here, the crossing transistor (C) of the Type-I circuit is replaced by two split counterparts (C-C), which are auto-biased. Thus, extra reference circuits are not needed and power consumption is reduced

### **Experimental Results**

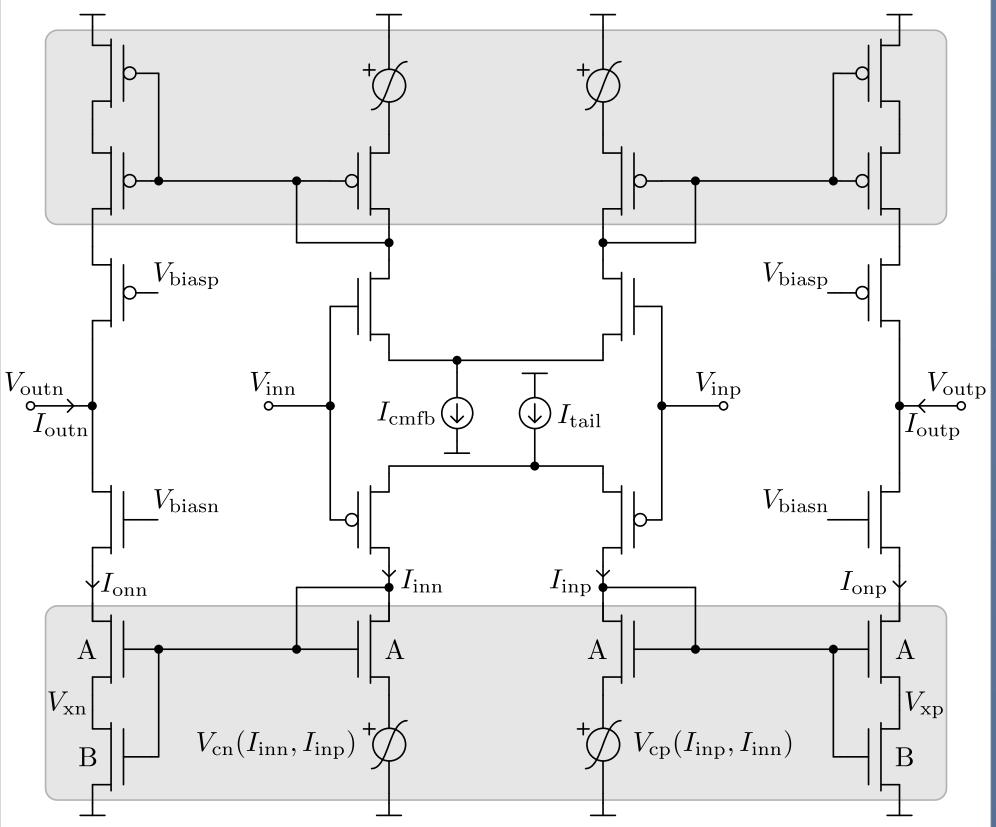

A single-stage-OpAmp architecture is proposed with two complementary Class-AB control paths for the NMOS and PMOS output transistors.

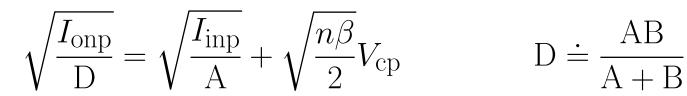

Supposing strong inversion operation for all boxed devices, each non-linear current amplifier behaves as

$I_{\text{inp}} = \left[ 2 \left( B \sqrt{\frac{I_{\text{onn}}}{D}} + C \sqrt{\frac{I_{\text{onp}}}{D}} \right) - (B + C) \left( \sqrt{\frac{I_{\text{onp}}}{D}} - \sqrt{\frac{I_{\text{inp}}}{A}} \right) \right] \left( \sqrt{\frac{I_{\text{onp}}}{D}} - \sqrt{\frac{I_{\text{inp}}}{A}} \right)$  $D \doteq \frac{A(B+C)}{A+B+C} \qquad \qquad I_{max} \simeq \frac{1+\frac{A}{C}}{1+\frac{A}{B+C}} I_{tail} > I_{tail}$

Independence from the technology parameters is also preserved.

## **Practical Design**

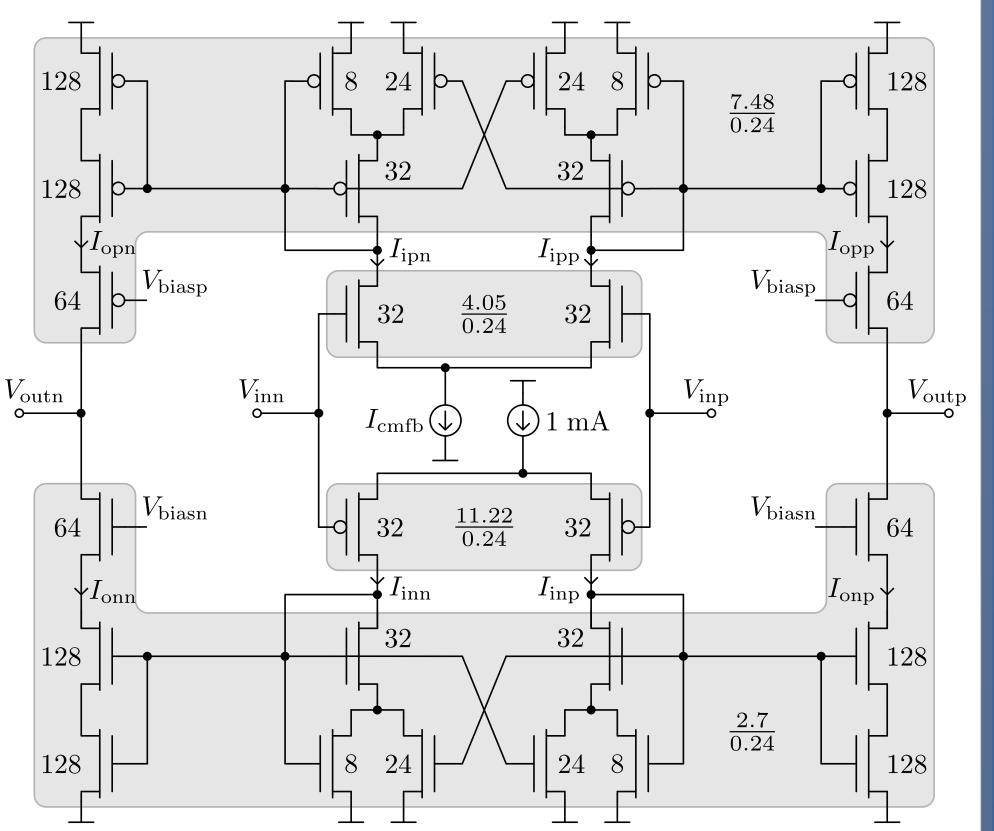

Type-II architecture is chosen for the design example in a 0.18-µm CMOS technology node.

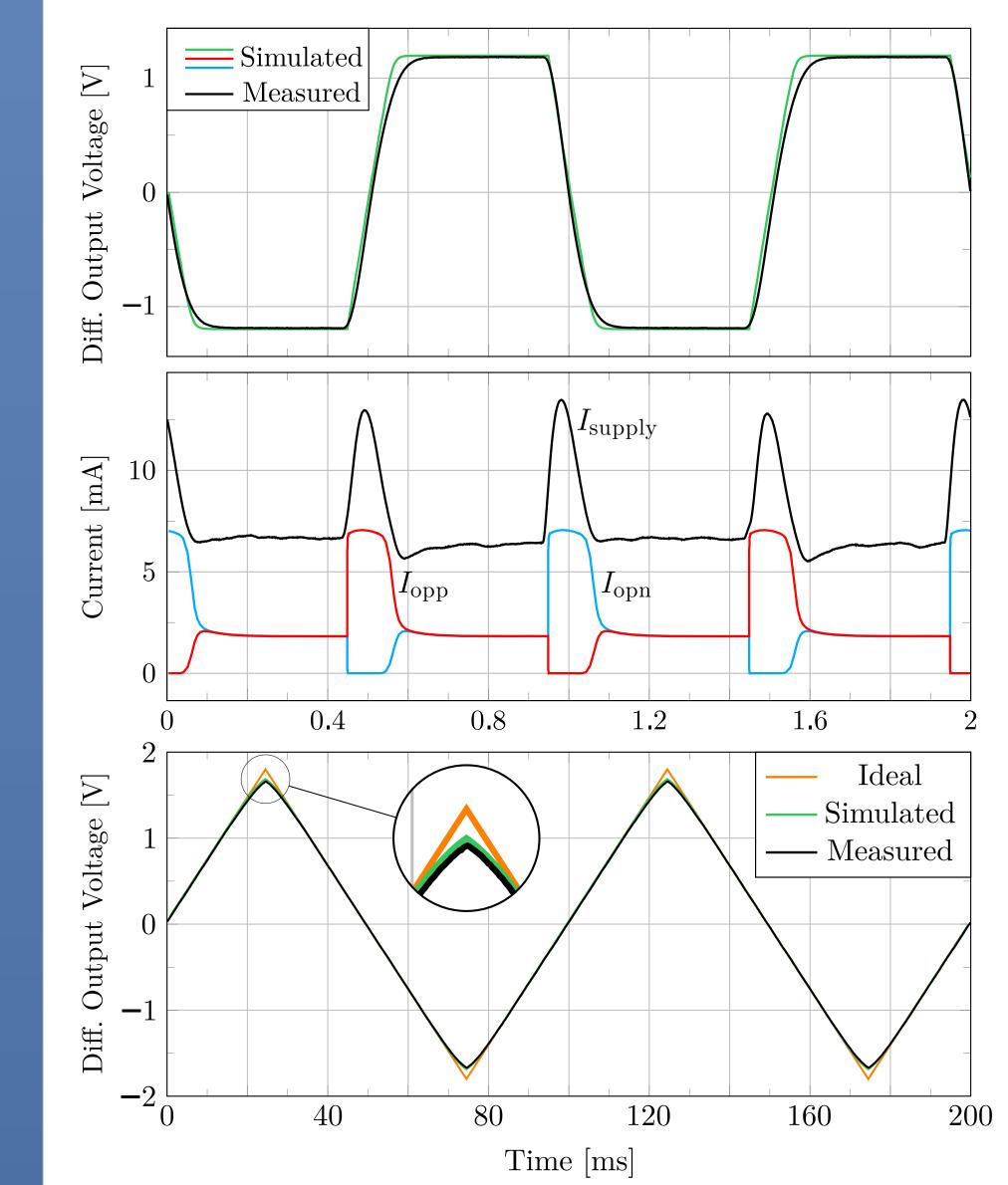

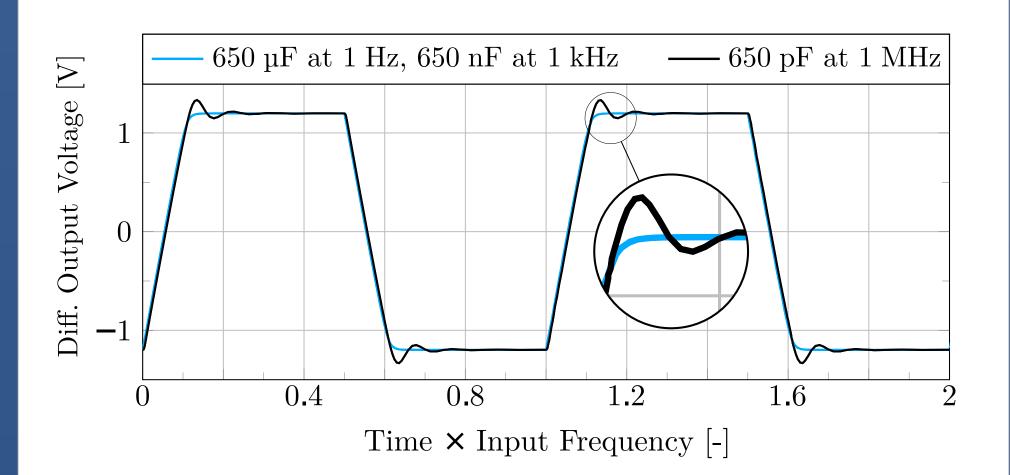

Operating at a 1.8-V power supply, a remarkable differential full scale of 3.3  $V_{pp}$  is measured. The performance of the proposed OpAmp is compared with others from published Class-AB amplifiers [1]–[5] by using the figure of merit (FOM) from [5]

|                   | $FOM = \frac{SR \cdot C_{\text{load}}}{P}$ |       |      | $\left[\frac{V}{\mus}\frac{pF}{\muW}\right].$ |        |              |                     |

|-------------------|--------------------------------------------|-------|------|-----------------------------------------------|--------|--------------|---------------------|

| Parameter         | [1]                                        | [2]   | [3]  | [4]                                           | [5]    | This<br>work | Units               |

| Technology        | 0.5                                        | 0.5   | 0.25 | 0.13                                          | 0.18   | 0.18         | μm                  |

| Supply            | 2                                          | 2     | 1.2  | 1.2                                           | 0.8    | 1.8          | V                   |

| DC gain           | 43                                         | 45    | 69   | 70                                            | 51     | 72           | dB                  |

| $C_{\text{load}}$ | 80                                         | 25    | 4    | 5.5                                           | 8      | 200          | pF                  |

| GBW               | 0.725                                      | 11    | 165  | 35                                            | 0.057  | 86.5         | MHz                 |

| Phase margin      | 89.5                                       | N/A   | 65   | 45                                            | 60     | 50           | 0                   |

| Slew rate, SR     | 89                                         | 20    | 329  | 19.5                                          | 0.14   | 74.1         | V/µs                |

| Static power, $P$ | 0.12                                       | 0.04  | 5.8  | 0.11                                          | 0.0012 | 11.9         | mW                  |

| Area              | 0.024                                      | 0.012 | N/A  | 0.012                                         | 0.057  | 0.07         | mm <sup>2</sup>     |

| FOM               | 59.33                                      | 12.50 | 0.28 | 0.98                                          | 0.93   | 1.25         | <u>V</u> pF<br>µsµW |

#### From the Class-AB viewpoint, the wanted functionality for these voltage-controlled current mirrors is:

$$\begin{cases} I_{\text{outp}} \equiv 0 & V_{\text{cp}} \equiv V_{\text{xp}} & I_{\text{onp}} \equiv I_{\text{inp}} \equiv \frac{I_{\text{tail}}}{2} & \text{Bias point} \\ \\ I_{\text{outp}} \not\equiv 0 & V_{\text{cp}} \not\equiv V_{\text{xp}} & \begin{cases} I_{\text{onp}} \ll I_{\text{inp}} \\ \\ I_{\text{onp}} \gg I_{\text{inp}} \end{cases} & \text{Class-AB operation} \end{cases}$$

### **Type-I** Circuit

A cross-coupled pair (B-B) is introduced to provide the positive feedback for the Class-AB operation, while a crossing transistor (C) play the role of a feedback limiter.

$I_{\rm inp} = B\left(2\sqrt{\frac{I_{\rm onn}}{D}} - \sqrt{\frac{I_{\rm onp}}{D}} + \sqrt{\frac{I_{\rm inp}}{A}}\right)\left(\sqrt{\frac{I_{\rm onp}}{D}} - \sqrt{\frac{I_{\rm inp}}{A}}\right) + C\left(\sqrt{\frac{2I_{tail}}{D}} - \sqrt{\frac{I_{\rm onp}}{D}}\right)$  $-\sqrt{\frac{I_{\text{onn}}}{D}} + \sqrt{\frac{I_{\text{inp}}}{A}} + \sqrt{\frac{I_{\text{inn}}}{A}} \left(\sqrt{\frac{I_{\text{onp}}}{D}} - \sqrt{\frac{I_{\text{onn}}}{D}} - \sqrt{\frac{I_{\text{inp}}}{A}} + \sqrt{\frac{I_{\text{inn}}}{A}} \right)$

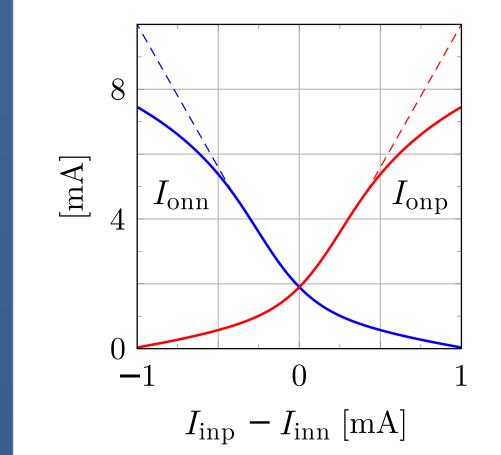

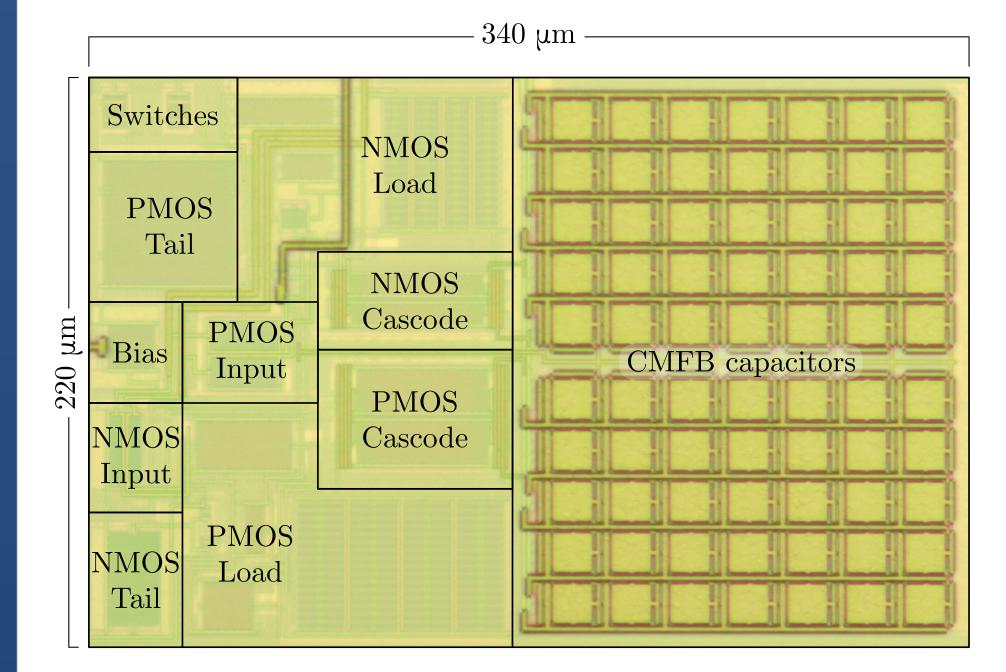

As shown, the number of transistor groups is minimized and minimum device lengths can be used. In this particular case, optimization finds the best performance for A=4, B=3 and C=1. The Class-AB behavior is demonstrated for the NMOS outputs.

The OpAmp is stable for a wide range of load capacitance values.

The OpAmp is integrated using a standard 0.18-µm 1P6M CMOS technology, achieving an overall area of 0.07-mm<sup>2</sup>. The circuit layout includes additional common-mode feedback (CMFB) averaging capacitors for switched-capacitor applications.

The works [1], [2] report higher FOM, but at the cost of requiring integrated resistors, which makes them more sensitive to technology parameter variations, and of a considerable lowering of their DC gain, which may be incompatible with high-precision applications. The works using MOS-only devices [3]–[5] present lower FOM and DC gain. Therefore, a contribution to the improvement of MOS-only Class-AB OpAmps is demonstrated.

### Conclusions

- A new family of Class-AB OpAmps has been presented.

- The architecture is based on a **single-stage** topology.

- The circuits do **not need** any internal frequency **compensation**.

- The Class-AB current peaks are produced in the output transistors only.

- The resulting OpAmps exhibit **low sensitivity** to the technology parameter variations.

- Good performance is achieved using a **simple** design flow.

- The Type II has been **successfully used** in a 16-bit 100-kS/s  $\Delta \Sigma$  ADC.

The process parameters  $\beta$  and n disappear from the currentamplifier equation. Hence, independence from technology is Under Class-AB high modulation, common-mode achieved. currents can be injected to prevent a possible self-latch.

#### References

[1] A. J. Lopez-Martin, S. Baswa, J. Ramirez-Angulo, and R. G. Carvajal, "Low-Voltage Super Class AB CMOS OTA Cells With Very High Slew Rate and Power Efficiency," IEEE Journal of Solid-State Circuits, vol. 40, pp. 1068-1077, 2005.

- [2] J. Ramirez-Angulo, R. G. Carvajal, J. A. Galan, and A. Lopez-Martin, "A Free But Efficient Low-Voltage Class-AB Two-Stage Operational Amplifier," IEEE Transactions on Circuits and Systems II: Expressed Briefs, vol. 53, pp. 568–571, 2006.

- [3] M. Yavary and O. Shoaei, "Very Low-Voltage, Low-Power and Fast-Settling OTA for Switched-Capacitor Applications," in Proceedings of the International Conference on Microelectronics, 2002, pp. 10–13.

- [4] M. Figueiredo, R. Santos-Tavares, E. Santin, J. Ferreira, G. Evans, and J. Goes, "A Two-Stage Fully Differential Inverter-Based Self-Biased CMOS Amplifier With High Efficiency," IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 58, pp. 1591–1603, 2011.

[5] M. R. Valero, S. Celma, N. Medrano, B. Calvo, and C. Azcona, "An Ultra Low-Power Low-Voltage Class AB CMOS Fully Differential OpAmp," in Proceedings of the IEEE International Symposium on Circuits and Systems, 2012, pp. 1967–1970.